【TC3xx芯片】TC3xx芯片的GTM模块详解

目录

6.5.5.1 Continuous Counting Up Mode

6.5.5.2 Continuous Counting Up-Down Mode

6.5.5.3 One-shot Counting Up Mode

6.5.5.4 One-shot Counting Up-Down Mode

7.5.5.1 Immediate Edge Propagation Mode

7.5.5.2 Individual De-glitch Time Mode (up/down counter)

7.5.5.3 Individual De-glitch Time Mode (hold counter)

7.5.5.4 Individual De-glitch Time Mode (reset counter)

7.5.5.5 Immediate Edge Propagation and Individual De-glitch Mode

7.5.8 .1 TIM?PWM Measurement Mode (TPWM)

7.5.8 .2 TIM Pulse Integration Mode (TPIM)

7.5.8 .3 TIM Input Event Mode (TIEM) ?

7.5.8 .4 TIM Input Prescaler Mode (TIPM)

7.5.8 .5 TIM Bit Compression Mode (TBCM)

7.5.8 .6 TIM Gated Periodic Sampling Mode (TGPS)

7.5.8 .7 TIM Serial Shift Mode (TSSM)

前言

GTM模块功能非常的强大也就会非常的复杂,我们在介绍GTM模块的时候仅站在工程开发者的角度去介绍需要用户关注和配置的关键地方,且仅重点介绍GTM对于PWM信号的输入输出功能,对于原理其其他复杂功能仅粗略介绍,详细的原理介绍请参考芯片手册,复杂的GTM功能作者也没有实践经验。

缩略词

| 简写 | 全称 |

| GTM | General Time Module |

| PWM | Pulse Width Modulation |

| CMU | Clock Management Unit |

| CCM | Cluster Configuration Module |

| TBU | Time Base Unit |

| TOM | Timer?Output?Module |

| CCU | Counter?Compare?Unit |

| TIM | Timer Input Module |

正文

1.GTM模块功能概述

通用定时器模块(General Timer Module)是博世(Bosch)公司所设计的一个模块。GTM可确保在汽车动力系统应用中实现准确的多输入数据采集和多输出信号生成。GTM可实时捕捉数字输入信号的变化并对其进行特征数据提取,以便进一步处理。由于GTM强大的可编程性,允许其使用复杂的脉冲调制(PWM)生成几乎任何信号形状。多个变成通道可并行允许,同时确保同步信号生成。

当前主流的半导体厂商,如Infineon, Renesas, NXP, ST, e.g.都在自家的MCU中集成了不同版本的GTM模块,满足不同的可编程PWM的需求。

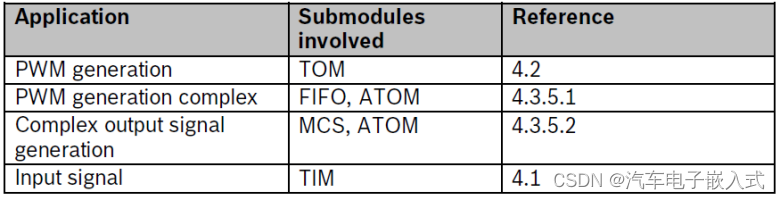

1.1 GTM具体功能

GTM基础功能

. 过滤,解析输入的PWM信号

.?输入可调制的(占空比,频率可可编程)PWM信号

GTM复杂功能

通过单个模块或者多个模块组合提供复杂的功能

. 无刷直流电机控制

. 发动机管理应用的发动机角度时钟

. 生成喷射/点火脉冲

….

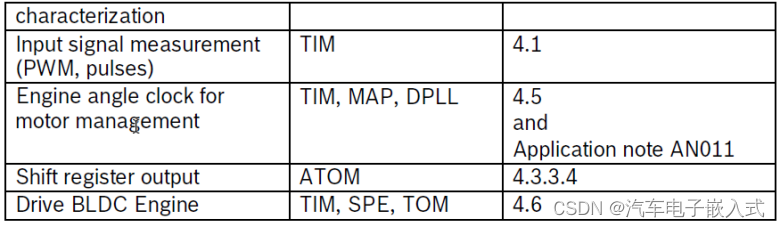

1.2 GTM架构

GTM 系统架构旨在为嵌入式控制应用提供灵活且可扩展的平台。 这种灵活性和可扩展性通过体系结构实现,其中子模块旨在提供特定于定时器的功能。 这些子模块由基础设施组件提供支持,这些基础设施组件提供时钟,时基(Time bases)和通信路径来连接子模块。 通过添加或删除不同应用程序域的子模块,可以实现可扩展性。

基础组件子模块

| 子模块 | 功能 |

| CMU | 为GTM内部模块和计数器提供时钟分频器 |

| TBU | 为其他子模块提供24位宽的时间戳 |

| ICM | 中断集中器,捆绑GTM内部中断,以减少到CPU的中断数量 |

| PSM | 参数存储模块,可用作FIFO,将参数存储进GTM或从GTM取值 |

| BRC | 广播数据,以一对多的方式通过高级路由单元传输数据 |

| ARU | 高级路由单元,以时分复用方式路由53位数据,实现一对一传输 |

输入输出子模块

| 子模块 | 功能 |

| TIM | 提供8个输出通道,可对输入信号进行特征提取或测量 |

| TOM | 提供16个通道用于产生PWM。每个通道既可以独立于其他通道允许,也可以相对于其他TOM通道允许 |

| ATOM | 与TOM不同,ATOM是与ARU连接的定时器输出模块。可以生成代表时间戳的PWM信号或复杂的输出序列 |

| DTM | 生成带死区的PWM。此外,DTM还可用于组合TOM或ATOM输出信号 |

MCS可以理解位GTM的内核。MCS有自己独立的内部RAM。可编程的对输入信号进行操作,并产生复杂的输出信号。输入信号铜鼓ARU路由到MCU,输出命令通过ARU路由到ATOM。

特定应用的子模块

| 子模块 | 功能 |

| DPLL | 用于发动机位置检测和生成角度时钟 |

| MAP | 负责将TIM0采样的信号映射到DPLL模块 |

| SPE | SPE子模块在TIM->SPE->TOM信号传输路径中提供无刷直流输入模式检测和无刷直流输出模式产生的功能 |

用于功能安全的子模块

| 子模块 | 功能 |

| CMP | CMP模块可以比较来自TOM或者ATOM模块的两个相邻通道输出,并在这两个信号不相同时产生错误 |

| MON | MON模块用于监控GTM内部时钟和MCS |

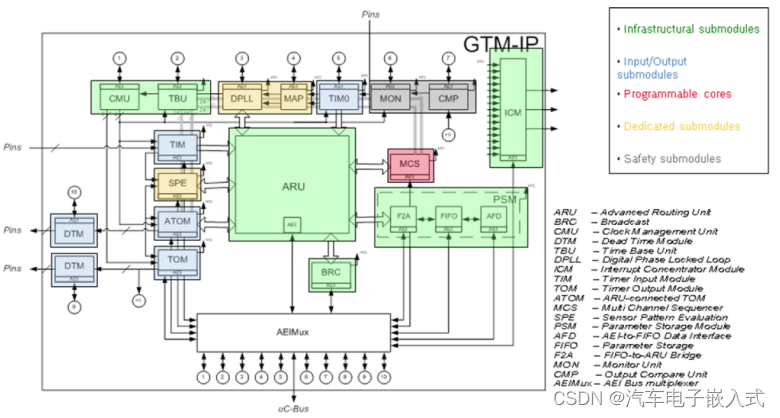

2. GTM模块输入时钟

GTM模块使用fGTM作为模块的输入时钟,根据<< ??? >>一文我们知道fGTM在Clock的CCU模块配置。

需要注意的是fGTM也就是GTM模块中的SYS_CLK. SYS_CLK是GTM?IP中的定义。

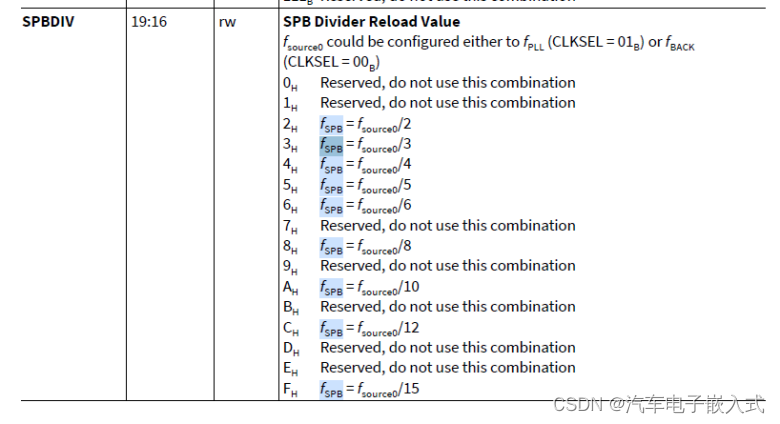

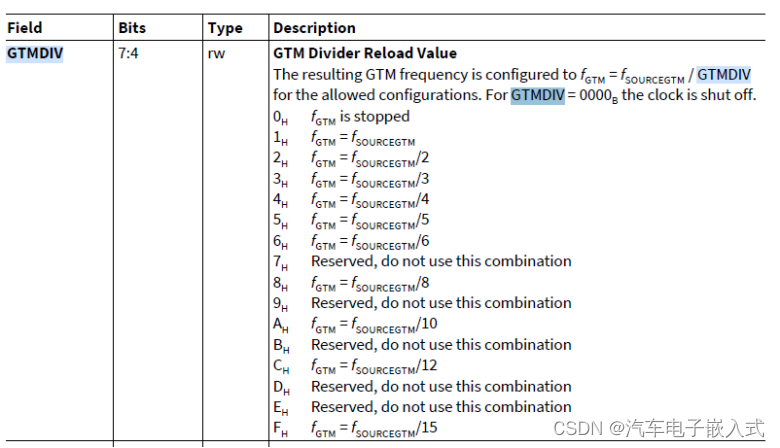

2.1.fGTM的值怎么计算

如上截图所示,fGTM的取值根据CCUCON0.GTMDIV的值和fSOURCEGTM的值来确定,fSOURCEGTM又根据CCUCON0.GTMDIV的不同而不同。

值得注意的是在MCAL配置工具EB中没有对CCUCON0.GTMDIV和CCUCON0.SPBDIV的配置,而是通过fSPB和fGTM的配置值去反推(生成寄存器的配置代码)fSOURCEGTM和CCUCON0.GTMDIV和CCUCON0.SPBDIV.

参考在<<【TC3xx芯片】TC3xx芯片的Clock System功能详解>>一文,如果我们配置:

fsource0 ==?fPLL0?== 300MHz

fsource1?==?fPLL1?== 320MHz

fsource2 ==?fPLL2?== 200MHz

fSPB == 100MHz

fGTM == 200MHz

则反推出:

CCUCON0.GTMDIV = 0x01

CCUCON0.SPBDIV = 0x03

也就是因为CCUCON0.GTMDIV == 0x01,则:

fGTM??/ 1 ?== fSOURCEGTM?== fSPB?* 2 == 200MHz.

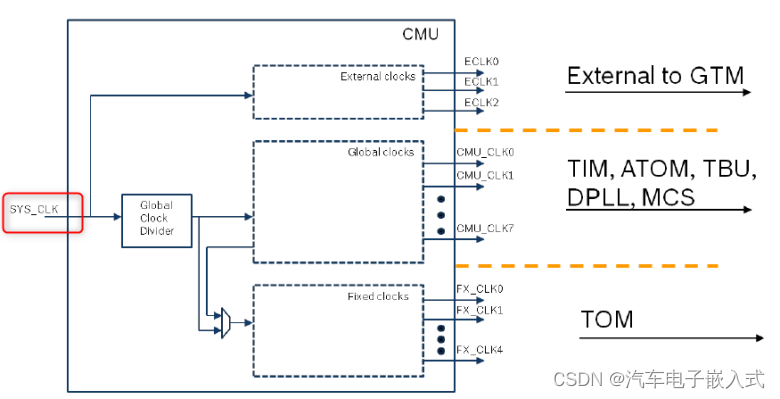

3. CMU

3.1 CMU功能

| 5 Fixed Clock | CMU_FXCLK[x] | Used for TOM sub-module for PWM generation |

| 9 Divided clocks | CMU_CLK[y] | Used for other sub-modules of GTM for signal generation |

| 3 external clocks | CMU_ECLK[z] | Used for external peripheral components |

CMU模块是系统时钟(SYS_CLK, 也就是fSTM)的时钟分频器?(clock divider),其他子模块的counter 计数都是由CMU提供。

考虑到GTM内部晶体管的功率消散,这个系统时钟不能超过?100MHz,GTM 内部的时钟最大频率可达到?200MHz。

SYS_CLK = fGTM?clock provided by the GTM wrapper. fGTM?max value is 2xfSPB = 200MHz

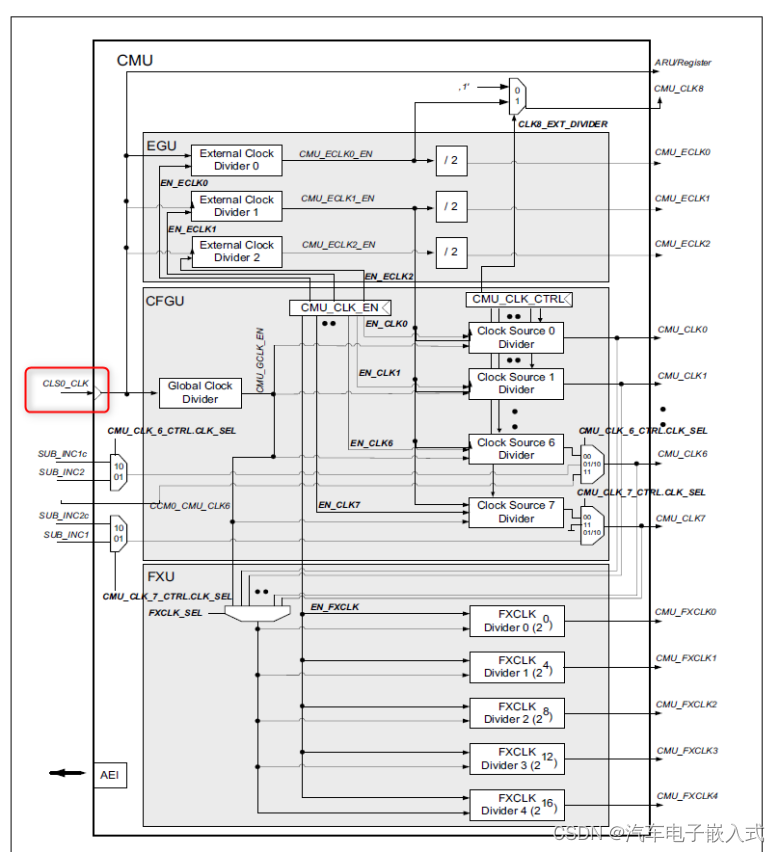

3.2 CMU时钟的计算

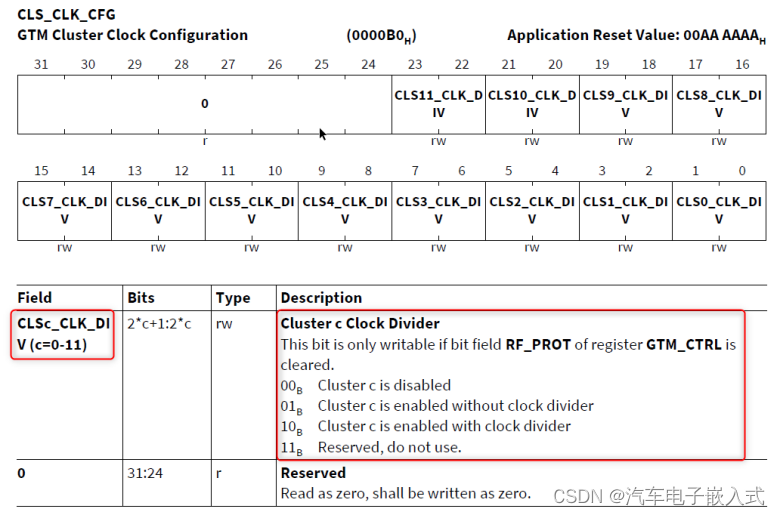

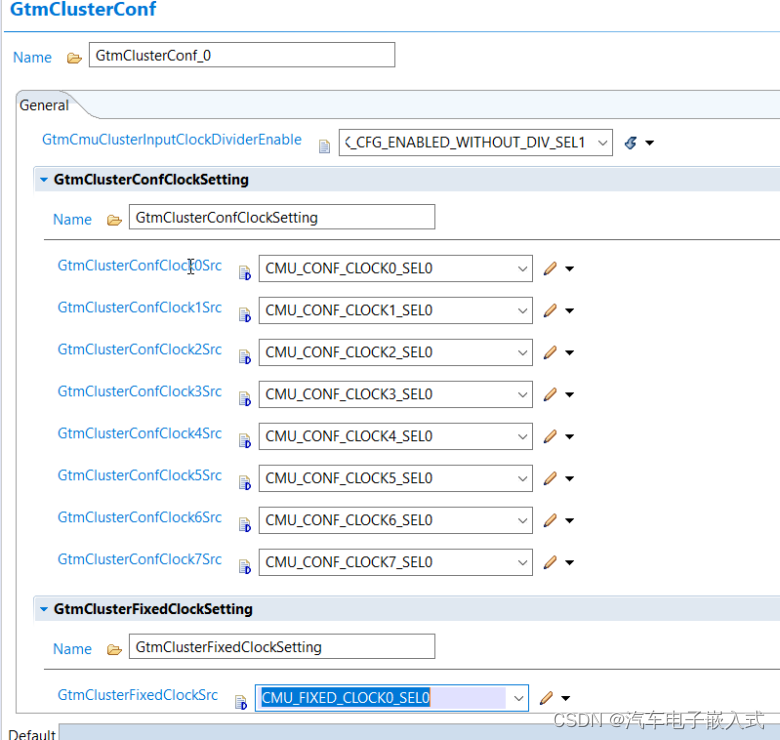

CMU模块的输入时钟是CLK0_CLK,这个CLK0_CLK不是在CCM模块配置,而是在GTM?TOP-Level Configuration Registers的CLS_CLK_CFG寄存器中配置。

3..2.1 CLS0_CLK怎么计算

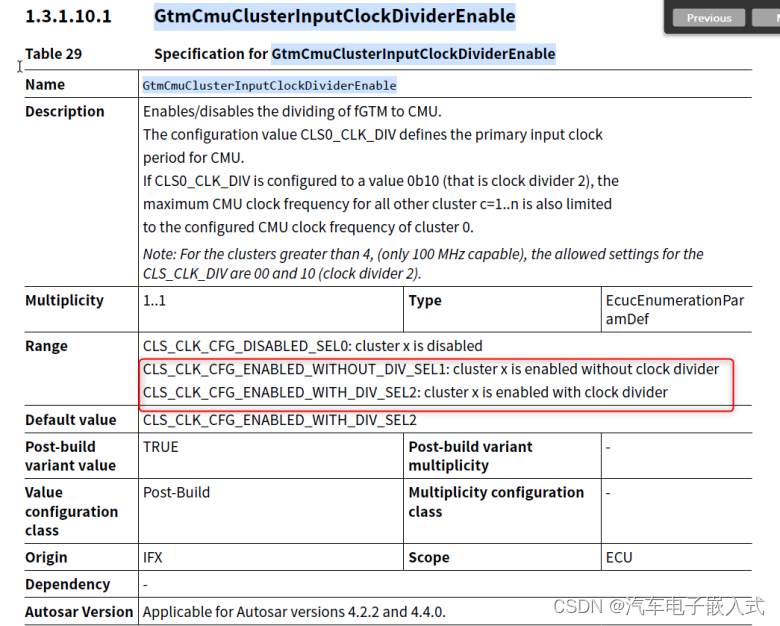

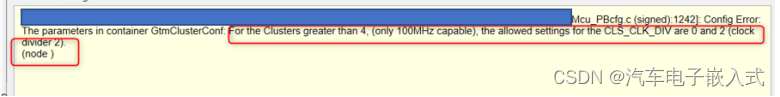

CLKS0_CLK的具体值由fSTM及其CLK_CLK_CFG.CLSc_CLK_DIV寄存器配置参数决定,具体规则见下文描述。

上图框选的内容对于CLK_CLK_CFG.CLSc_CLK_DIV寄存器位域的0x01和0x02配置值。

如果GtmCmuClusterInputClockDividerEnable配置为CLS_CLK_CFG_ENABLED_WITHOUT_DIV_SEL1则CLS0_CLK等于fSTM.

如果GtmCmuClusterInputClockDividerEnable配置为CLS_CLK_CFG_ENABLED_WITH_DIV_SEL2则CLS0_CLK等于fSTM/2 = 100 MHz,但是不推荐这么干。

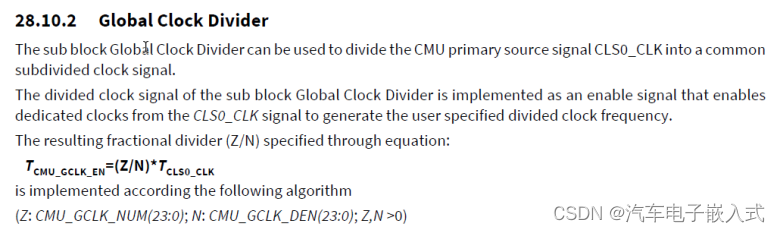

3.2.1 GTM Global Clock时钟计算

也就是fCMU_GLCLK ?= (N/Z)*fCLS0_CLK

For?Example:

fCLS0_CLK?= fSTM?== 200MHz

Z = 1

N = 1

则?fCMU_GLCLK ?= (N/Z)*fCLS0_CLK == 200MHz

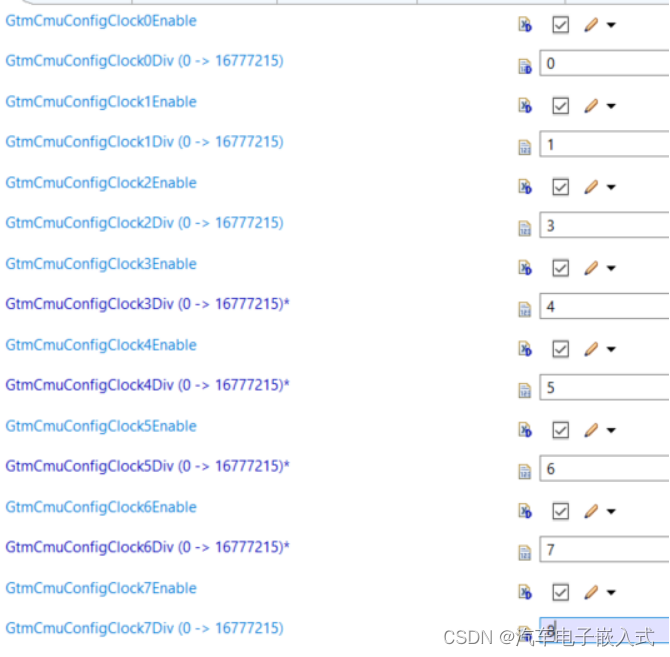

3.2.2 分频时钟的计算

fCMU_CLK[X] = fCMU_GCLK_EN / (CLK_CNT[X] + 1)

比如fCMU_CLK[2] = fCMU_GCLK_EN / (3 + 1) = 200 /?4 = 50 MHz

4. CCM

4.1 CCM功能

一个CMU连接多个CCM(TC37x有6个CCM),每个CCM输出的时钟给每个Cluster里面的模块(TIM,TOM,ATOM,e.g.)使用。

4.2 CCM时钟计算

每个CCM中的时钟和引用的CMU的时钟是一一对应的(时钟大小一样)。

5. TBU

5.1 TBU的功能

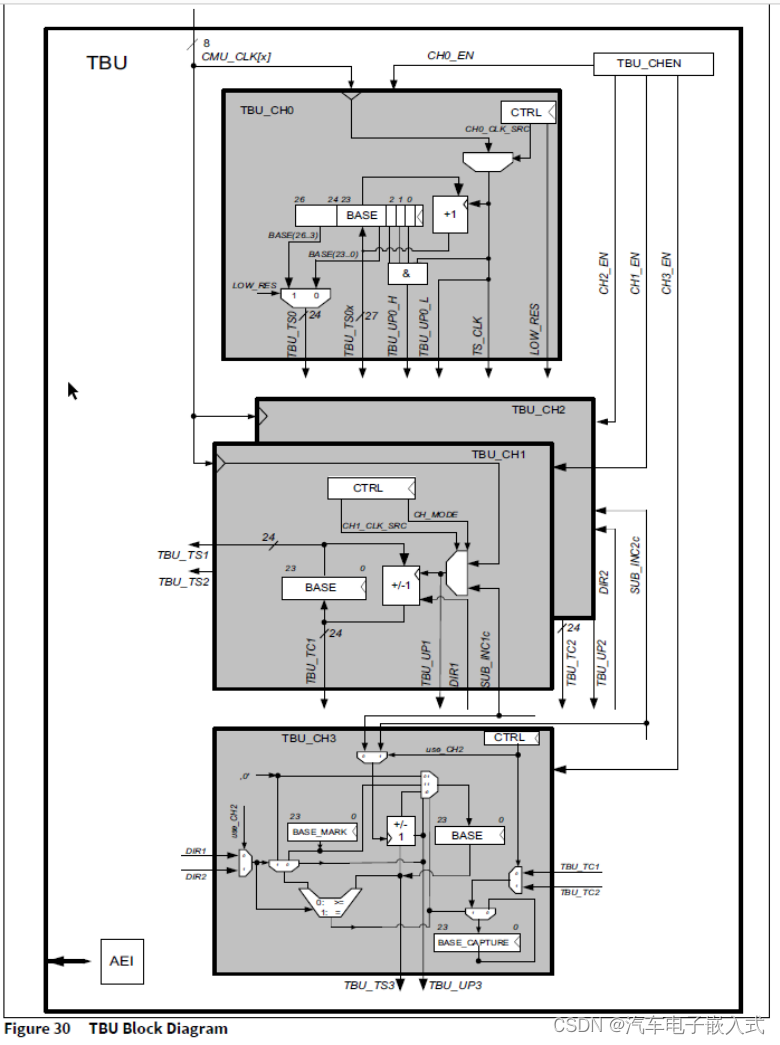

时间基准单元 TBU 为 GTM 提供通用时间基准。 TBU 子模块按通道组织,通道数取决于具体芯片型号。 TBU 内最多可实施四个通道。

TBU 信道 0 的时间基寄存器 TBU_CH0_BASE 为 27 位宽,可以配置为将 24 位下或 24 位上作为信号 TBU_TS0 提供给 GTM。 两个 TBU 通道 1 和 2 具有 24 位长度的时间基寄存器 TBU_CH[y]_base (y : 1 , 2)。 时间基准寄存器值 TBU_TS[y] 提供给 GTM 的后续子模块。

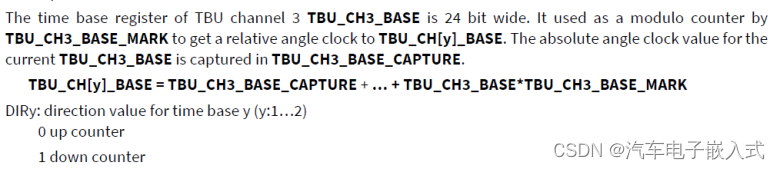

TBU 通道 3 TBU_CH3_BASE 的时基寄存器为 24 位宽。 它被 TBU_CH3_base_mark 用作模数计数器,以获得与 TBU_CH[y]_base 相对的角度时钟。 当前 TBU_CH3_BASE 的绝对角度时钟值在 TBU_CH3_base_capture 中捕获。

TBU_CH[y]_BASE = TBU_CH3_BASE_CAPTURE + … + TBU_CH3_BASE*TBU_CH3_BASE_MARK

The signal TBU_UP0_L is set to high for a single SYS_CLK period if the signal TBU_TS0 and TBU_TS0x is getting updated and TBU_UP0_H is set to high for a single SYS_CLK period, whenever the upper 24 bit of TBU_TS0 are updated.

个人理解:

1.只要CMU_CLK [0]加1,则TBU_UP0_L就会置高

2.?CMU_CLK [0]加2^24后,则TBU_UP0_H才置高

配置完TBU后,最终体现在对外的信号就是通过TBU_CHx_BASE[x, 0-3]读取4个Channel的基数值。

TBU_CH0_BASE的值随着CMU_CLK [0]?输入而循环增加。

TBU_CH1_BASE和TBU_CH2_BASE可以引入DIR1/2进行+1/-1,引入SUB_INC1c/2c进行补偿,而DIR和SUB_INC信号来自DPLL硬件模块(专用于发动机控制)。

TBU_CH3_BASE更加复杂,引入TBU_CH3_BASE_CAPTURE和TBU_CH3_BASE_MARK。

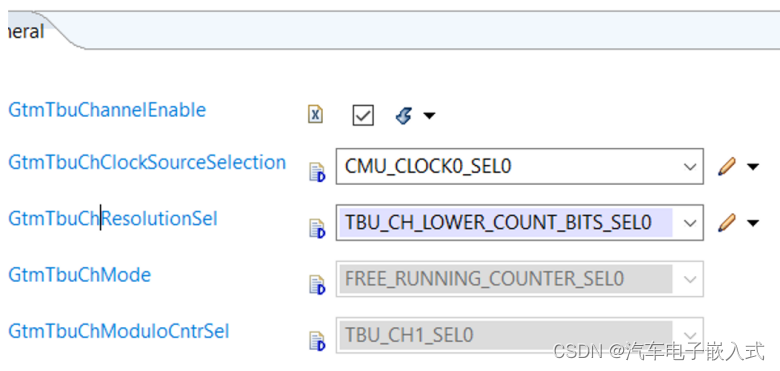

5.2 TBU时钟计算

对于非专用ECU(发动机控制器,电机控制器,e.g.)我们只要Enable TBU_CH0_BASE即可。

TBU_CH0_BASE使用CMU_CLOCK0(按照上文的配置应该是200MHz).

6. TOM

6.1 TOM功能

TOM主要用来输出简单的PWM信号。此外,在 Tom 输出 TOM[I]_CH15_OUT 时,可以生成脉冲计数调制信号。

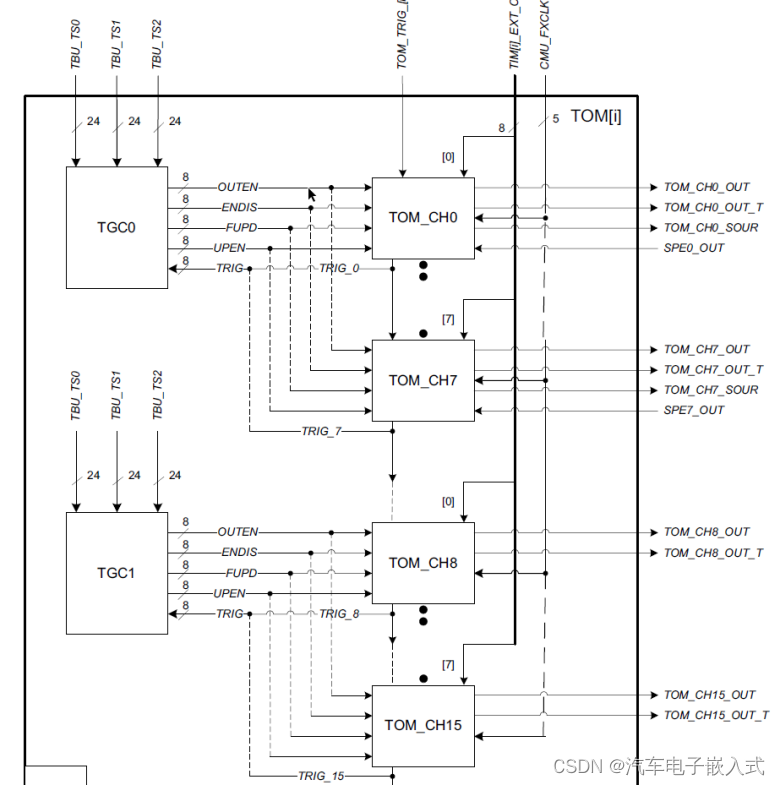

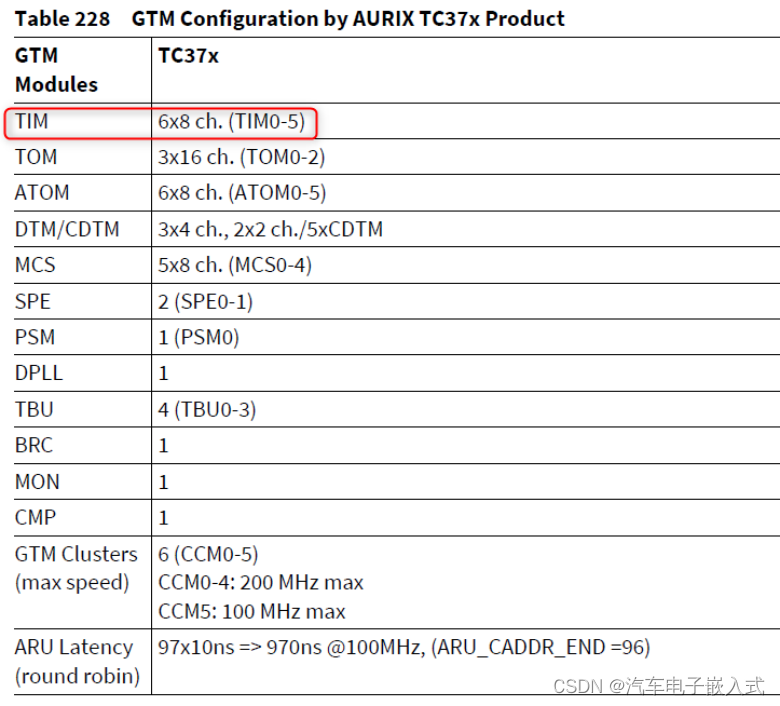

6.2 TOM硬件资源

以TC377为例。TC377有3个TOM硬件单元,每个TOM Unit有16个Channel(Channel0 – Channel15),也就是总共有3?* 16 = 48 Channel. 每个TOM Unit的16个Channel分为两组(Group 0和Group 1),Group 0为Channel0 – Channel7, Group?1为Channel8 – Channel15.

6.3 TOM中断

Channelx和Channelx+1共用一个IRQ.

For?Example:

为GTMTOM1Channel7配置中断,中断地址为:0xE10 + 1*0x20 + 3*4 == 0xE3C,在Os中配置IRQ的时候需要配置。

6.4 TOM时钟

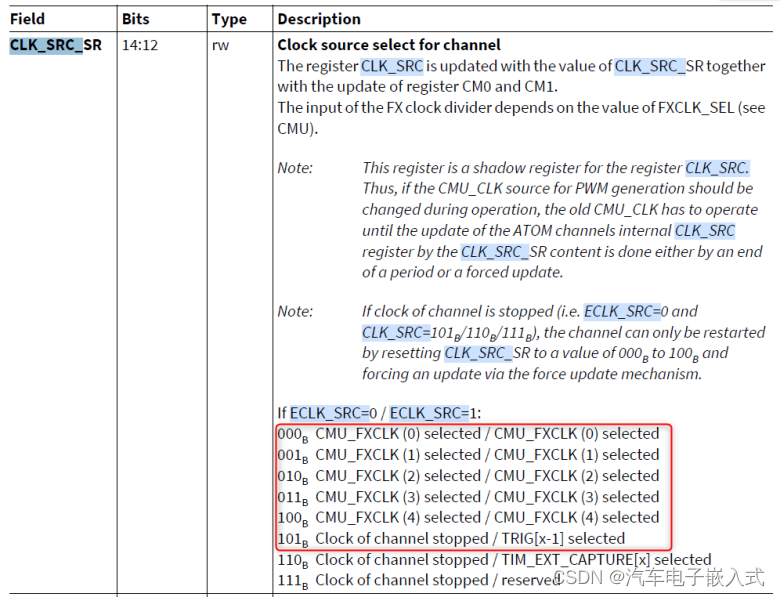

由上图可知CMU.FXU的输入时钟选用GTM_GLOBAL_CLOCK,也就是fCLS0_CLK,也就是200MHz.

CMU.FXU的输出时钟为:

CMU_FXCLK0 = 200MHz / 1 = 200 MHz

CMU_FXCLK1 = 200MHz / 16 = 12.5 MHz

CMU_FXCLK2 = 200MHz / 256 = 781.25KHz

CMU_FXCLK3 = 200MHz / 4096 = 48.828125KHz

CMU_FXCLK4 = 200MHz / 655336 = 3051.7578Hz

TOM每个通道的时钟源由TOMi_CHx_CTRL. CLK_SRC_SR配置。

问题:EB上MCU模块的GtmGlobalConfiguration上没有配置使用哪个CMU_FXCLKx?

答:EB上MCU模块的GtmGlobalConfiguration值配置Gtm的一切Global配置项,具体的PWM输出也就是TOM Channel的时钟配置,TIM?Channel的输入也就是TIM?Channel的时钟配置,需要在对应的PWM,ICU AUTOSAR标准模块配置。

6.5 TOM内部原理

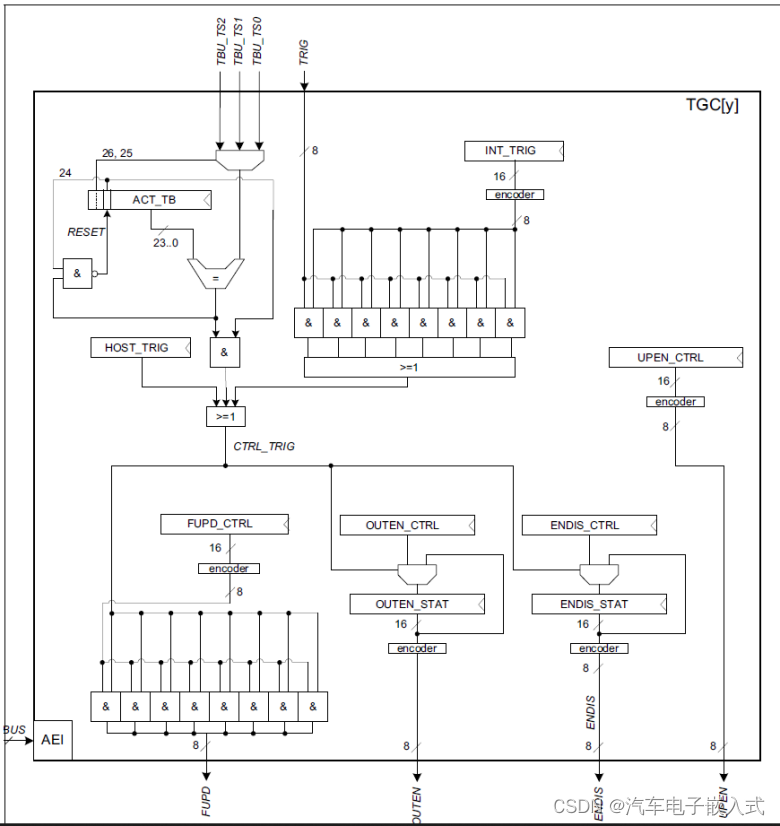

6.5.1 TOM通道使能

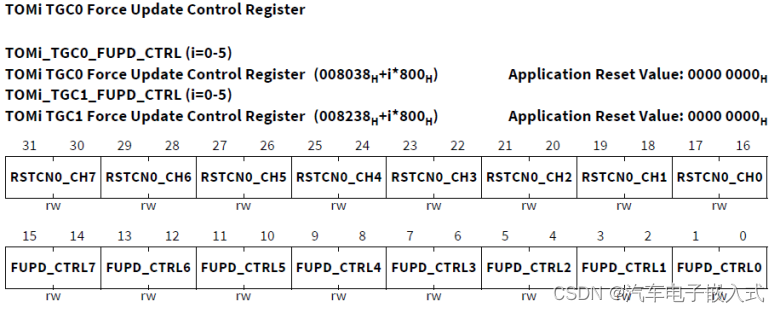

如上图所示,主要控制的就是TOM模块的使能和更新,也就是上图模块的三个输出,由TOM[x]_TGC[y]_FUPD_CTRL, TOM[x]_TGC[y]_OUTEN_CTRL,?TOM[x]_TGC[y]_ ENDIS_CTRL三个寄存器体现:

TOM[x]_TGC[y]_FUPD_CTRL:强制更新CM1(PWM占空比), CM0(PWM周期), CLK_SRC(时钟源信号),以及复位CN0(时钟计数寄存器).

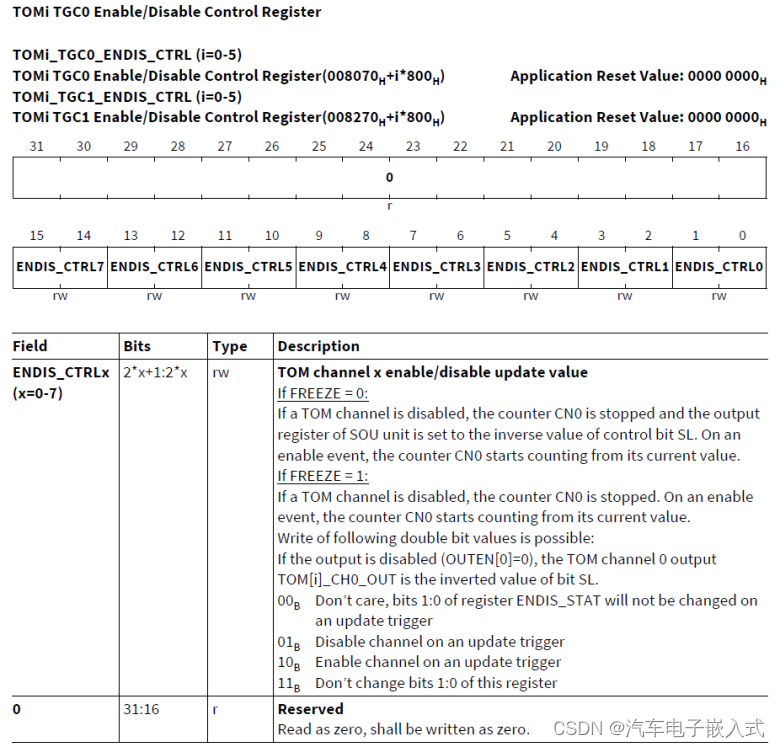

TOM[x]_TGC[y]_OUTEN_CTRL:控制Channel的Enable/Disable.

TOM[x]_TGC[y]_ ENDIS_CTRL:控制Output的Enable/Disable.

如果我们直接配置TOM[x]_TGC[y]_FUPD_CTRL, TOM[x]_TGC[y]_OUTEN_CTRL,?TOM[x]_TGC[y]_ ENDIS_CTRL三个寄存器,那它们既是输入也是输出,作为输入也就是我们配置这三个寄存器,作为输出就是这三个寄存器控制TOM通道的使能和更新。

除了直接配置TOM[x]_TGC[y]_FUPD_CTRL, TOM[x]_TGC[y]_OUTEN_CTRL,?TOM[x]_TGC[y]_ ENDIS_CTRL三个寄存器外,我们还可以通过以下三种Global方式来控制TOM通道的使能和更新,这样TOM[x]_TGC[y]_FUPD_CTRL, TOM[x]_TGC[y]_OUTEN_CTRL,?TOM[x]_TGC[y]_ ENDIS_CTRL这三个寄存器仅仅作为输出:

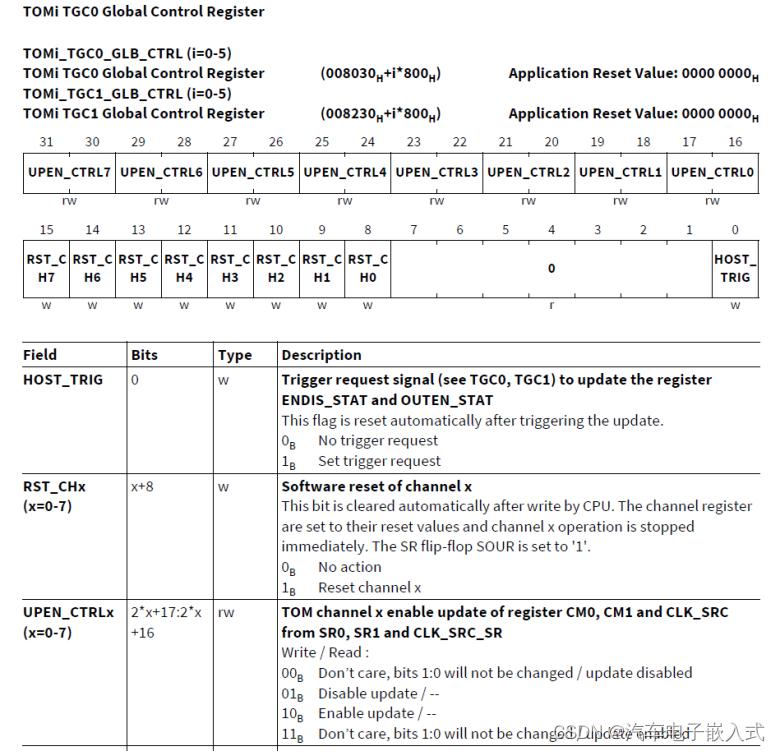

方式一:Host?CPU触发方式

TOMi(i=0-5)_TGCx(x=0-1)_GLB_CTRL.?HOST_TRIG: Enable/Disable所有通道的Channel和Output.

TOMi(i=0-5)_TGCx(x=0-1)_GLB_CTRL.?RST_CHx: Reset CN0 寄存器(时钟计数)。

TOMi(i=0-5)_TGCx(x=0-1)_GLB_CTRL.?UPEN_CTRLx: 强制更新CM1(占空比), CM0(PWM周期)和CLK_SRC寄存器(时钟源)。

方式二:TBU时间戳触发方式

TOMi_TGCx_ACT_TB((i=0-5),x=0-1).ACT_TB: 配置Compare的值。

TOMi_TGCx_ACT_TB((i=0-5),x=0-1).TB_TRIG: Timeout发生后自动置为,请求Enable所有TOM通道。

TOMi_TGCx_ACT_TB((i=0-5),x=0-1).TBU_SEL: 选择需要Compare的TBU时基。

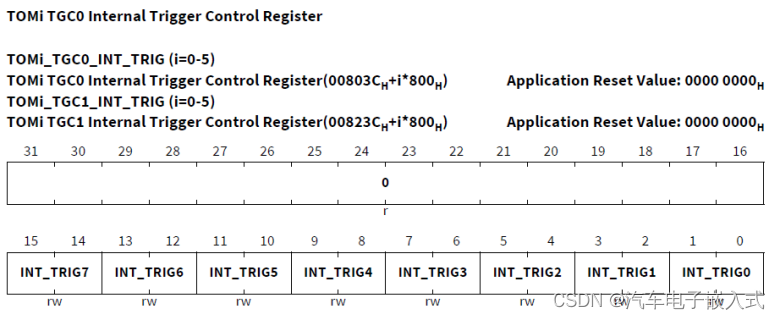

方式三:其他TOM通道信号触发方式

TOM[i]_TGC[y]_INT_TRIG是一个掩码寄存器。也就是说,其他8个TOM的输出信号作为TRIG_[X]本身都可以Enable?Channel的,通过配置TOM[i]_TGC[y]_INT_TRIG.INT_TRIGx可以Mask掉哪些通道有Enable的功能。

问题:TOM[i]_TGC[y]_ENDIS_CTRL和TOM[i]_TGC[y]_ENDIS_STAT寄存器的layout和位域信号完全一样,功能上有啥区别了?

答:Enable/Disable一个TOM通道,TOM[i]_TGC[y]_ENDIS_CTRL和TOM[i]_TGC[y]_ENDIS_STAT寄存器必须都被Used,寄存器 TOM[I]_TGC[y]_ENDIS_STAT?直接控制信号 ENDIS。 可以对该寄存器进行写访问。寄存器 TOM[I]_TGC[y]_ENDIS_CTRL?是一个阴影寄存器(SR, Shadow Register),如果三个触发条件之一匹配,它将覆盖寄存器 TOM[I]_TGC[y]_ENDIS_STAT?的值。

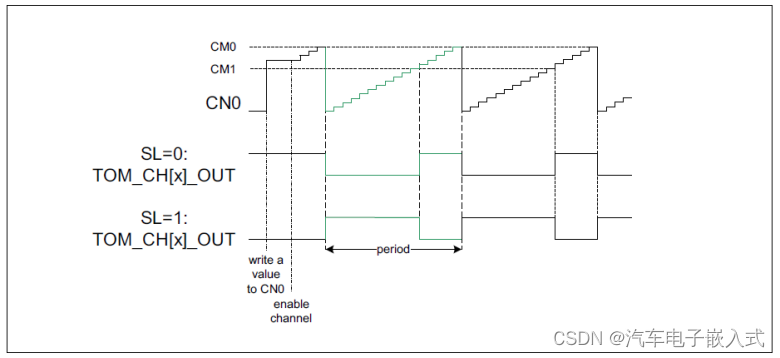

6.5.2 TOM通道输出

TOM[i]_CH[y]_CN0保存了输入时钟CMU_FXCLKx的计数值(Counter)。

TOM[i]_CH[y]_CM0保存了TOM通道输出的周期数(Period, 由用户配置PWM的周期)。

TOM[i]_CH[y]_CM1保存了TOM通道输出的占空比(Duty Cycle, 由用户配置PWM的占空比)。

问题:以上三个寄存器里面的具体值代表什么物理意义了?比如三个寄存器值是100,400,200。

答:以上三个寄存器保存的是基于通道时钟的Ticks数,比如我们使用的CMU_FXCLKx为200MHz,则一个tick的时间为1/200(us) = 5ms,那么:

TOM[i]_CH[y]_CN0?= 100 –>当前计数值为100个ticks,也就是500ms.

TOM[i]_CH[y]_CM0=?400 -> Period为400个Ticks,也就是2000ms,

TOM[i]_CH[y]_CM1=200 ->Duty Cycle为200个Ticks,也就是1000ms,也就是占空比为50%。

TOM[i]_CH[y]_CN0寄存器的清零由TOM[i]_CH[x]_CTRL寄存器的RST_CCU0位域信号。

两种清零方式:

方式一:CN0的计数值等于CM0是自动清零。

方式二:由上衣一个TOM通道TRIG_[x-1]或者外部捕获信号TIM_EXT_CAPTURE(x)清零。

当CN0寄存器的值大于CM0寄存器值的时候,触发TRIG_CC0信号;当CN0寄存器的值大于CM1寄存器值的时候,触发TRIG_CC1信号。也就是计数值大于PWM周期值和PWM占空比值都有内部信号产生,这样能触发对应的PWM脉冲输出。

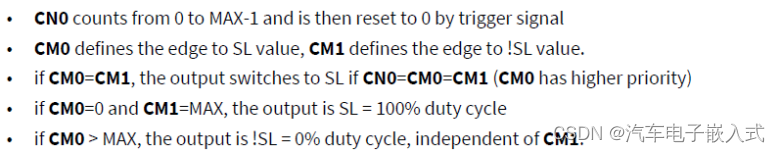

如果配置CN0寄存器的配置为它自己CCU0清零(RST_CCU0 = 0,CN0 >= CM0 -1),那么以下说明是有效的:

. CN0的变化规律为0?->?CM0 – 1 -> 0 -> …

. 如果CN0计数器达到CN0 > CM1,则一个!SL的边沿输出信号产生(比如SL配置为低电平1,!SL则为低电平0)。

. 如果CM0 = 0或者CM0=1,则CN0的值永远为0。

. 如果CM1=0,则TOM通道的输出(PWM输出)的占空比永远为0%(占空比 = CM1 / CM0),电平状态为!SL(SL配置为1,则占空比由SL也就是高电平1来计算,输出!SL也就是低电平0)。

.?如果CM1 >= CM0且CM0 > 1,则输出为SL(SL配置为1,则占空比由SL也就是高电平1来计算,输出SL也就是高电平1),占空比为100%。

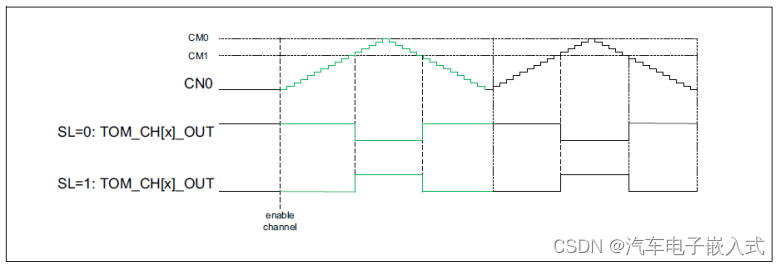

如果配置CN0寄存器的配置为其他TOM Channel清零或者TIM模块的外部捕获信号清零(RST_CCU0 = 1),那么以下说明是有效的:

TOM?Channel的初始电平状态由SL的反向状态确定。

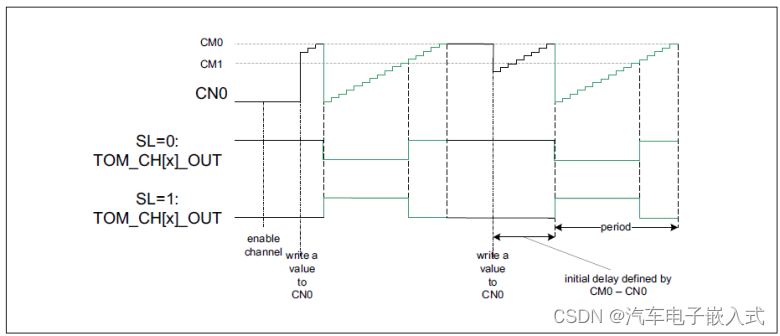

6.5.3 TOM占空比,周期,时钟频率的更新机制

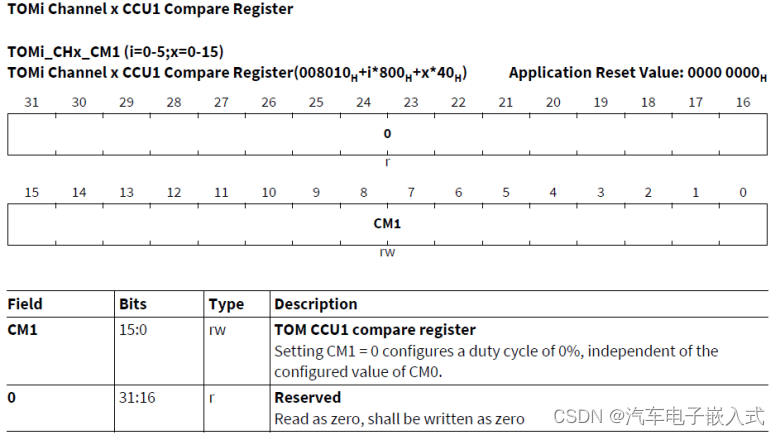

CM0寄存器保存PWM输出的周期计数值,SR0为CM0的Shadow Register.

CM1寄存器保存PWM输出的频率计数值,SR1为CM1的Shadow Register.

CLK_SRC确定PWM输出使用的时钟频率,TOM[i]_CH[x]_CTRL寄存器的CLK_SRC_SR位域信号为CLK_SRC的Shadow Register.

问题:怎么理解Shadow Register?

答:Shadow Register保存了下一次寄存器需要更新的值。比如TOM通道的PWM正在以CM0的周期,CM1的占空比,以及CLK_SRC的时钟正在对外输出,我们需要Update PWM输出的参数,那么我们可以先更CM0,CM1和CLK_SRC的Shadow Register,也就是先更新SR0,SR1和CLK_SRC_SR,这样在某个确定时刻统一把Shadow Register中内容更新到寄存器中。

问题:在哪个时间点把SR寄存器的内容更新到CM0,CM1和CLK_SR寄存器?

答:在CN0寄存器的值被Reset的时刻。

通过执行以下步骤,可以获得Duty Cycle,Period和计数器 CN0 时钟频率的同步更新,该更新将与新周期的开始同步生效:

第一步:

通过将寄存器 TOM[I]_TGC[y]_GLB_CTRL 的通道特定配置位 UPEN_CTRL[z] 设置为“ 0 ”,禁用使用相应阴影寄存器内容更新操作寄存器。

第二步:

往SR0,SR1,CLK_SRC_SR寄存器中写入期望的更新值。

第三步:

通过将寄存器 TOM[I]_TGC[y]_GLB_CTRL 的通道特定配置位 UPEN_CTRL[z] 设置为“ 1 ”,启用操作寄存器的更新。

注意:往SR寄存器中写入新的值,只会在Reset CN0的时候更新到CM0,CM1和CLK_SR,只有在UPEN_CTRL[z]?== 1的前提下才能在下一个新的周期完成实际输出更新。也就是说,往SR寄存器写入新的值一定是同步更新的。

6.5.4 TOM同步更占空比和异步更新占空比

只需将所需的新值写入 SR1,而无需事先禁用更新机制,即可实现仅占空比的同步更新 (如上一章所述)。 新的占空比下一个周期开始体现。

如果想独立于新Period?(异步) 的开始执行占空比的更新,则所需的新值可以直接写入寄存器 CM1。 在这种情况下,建议额外禁用整个同步更新机制 (即,在寄存器 TOM[i]_TGX[y]_GLB_CTRL中清除对应通道 [x] 的位 UPEN_CTRL[z] ,或者在写入 CM1 之前更新 SR1 的值与 CM1 相同。

6.5.5 计数模式

6.5.5.1 Continuous Counting Up Mode

在连续模式下, Tom 通道通过在寄存器 TOM[I]_TGC[y]_ENDIS_STAT 中设置相应的位来启用计数器寄存器 CN0 后,开始递增计数器寄存器 CN0。

生成的输出信号的电平状态(高电平?or 低电平)可以使用通道配置寄存器 TOM[I]_CH[x]_CTRL 的配置位 SL 进行配置。

如果计数器 CN0 从 CM0 重置为零,则期间的第一个边缘将在 TOM[I]_CH[x]_OUT 处生成。

如果 CN0 达到 CM1 ,则会生成周期的第二个边缘。

每次计数器 CN0 达到 CM0 的值时,它都会重置为零,并继续递增。

注意:这个模式应该是PWM输出的最常用模式,以下的几种模式应该是用于特殊的PWM输出常见,不在详述,具体可以去参考芯片手册。

6.5.5.2 Continuous Counting Up-Down Mode

6.5.5.3 One-shot Counting Up Mode

6.5.5.4 One-shot Counting Up-Down Mode

7. TIM

7.1 TIM功能

计时器输入模块 (TIM) 负责过滤和捕获 GTM 的输入信号。 可以在 TIM 通道内测量输入信号的几个特征。 对于高级数据处理,可通过 ARU 将检测到的 TIM 模块输入特性传送到 GTM 的后续处理单元。

输入特性是指检测到的输入上升或下降边缘的时间戳值以及新的信号电平,或者信道启用后接收到的边缘数,以及整个 PWM 周期的实际时间戳或 PWM 信号持续时间。

7.2 TIM硬件资源

以TC377为例。TC377有6个TIM硬件单元,每个TIM Unit有8个Channel(Channel0 – Channel7),也就是总共有6 * 8 = 48 Channel.

7.3 TIM中断

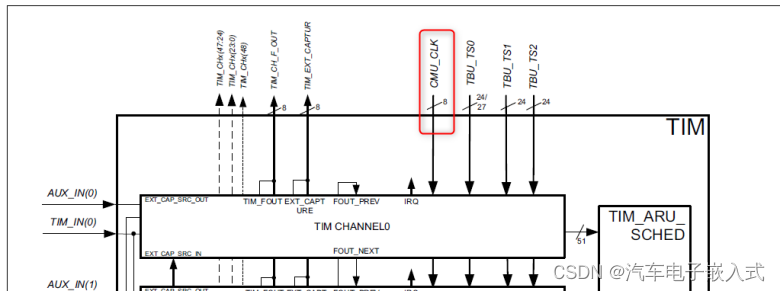

7.4 TIM时钟

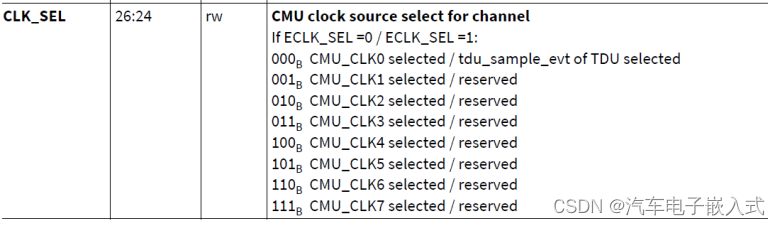

TIM模块使用CMU_CLK时钟,8个CMU_CLKx具体使用哪一个由TIM[i]_CH[x]_CRTL寄存器的CLK_SEL位域配置。

7.5 TIM内部原理

7.5.1 TIM功能概述

CPU可以通过AEI总线直接读取TIM模块的测量值,或者TIM模块将测量值通过ARU路由给其他GTM的子模块。

来自 TBU 的两 (三) 个Time Base连接到 TIM 通道,以对传入信号添加时间戳。 对于 TIM0 ,扩展的 27 位宽度时基 TBU_TS0 连接到 TIM 通道,用户必须选择下 24 位 (TBU_TS0 (23…0)) 或上 24 位 (TBU_TS0 (26…3)) 存储到 GPR0 和 GPR1 寄存器中。

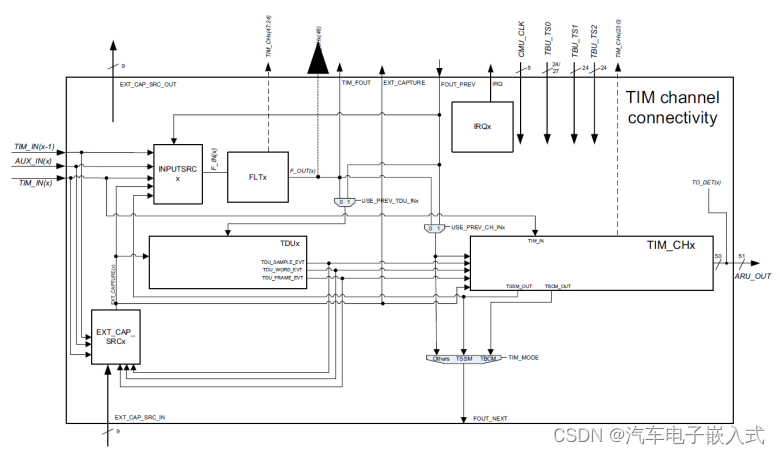

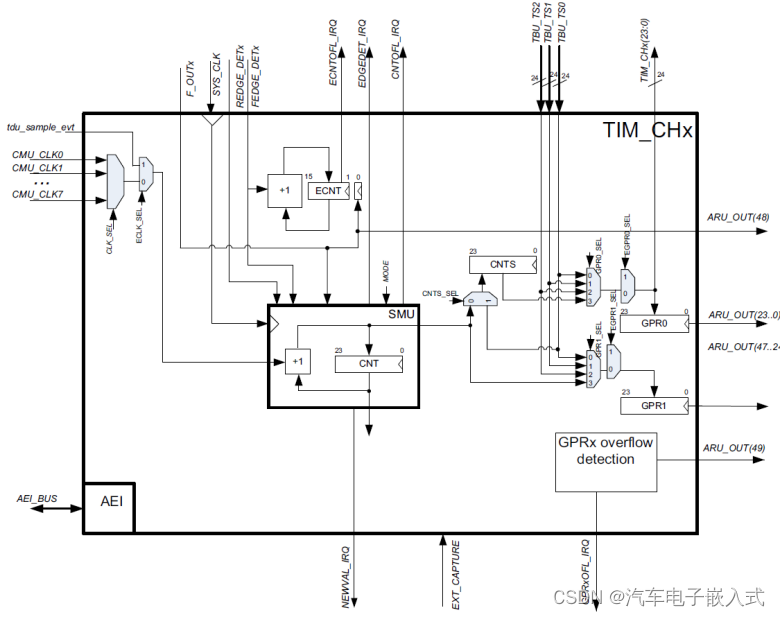

上图概述了TIM Channel的内部连接。 下面列出了具有主要功能的子单位:

INPUT_SRCx: 为过滤单元FLTx选择输入信号。

FLTx: 为输入信号提供了不同的硬件过滤机制。

TDUx: 超时检测单元 (在指定的持续时间内未检测到后续跳变沿Edge)

TIM_CHx: 通道测量单元。为过滤后的信号提供不同的测量机制。

IRQx: 本地中断控制器。

EXT_CAP_SRCx: 选择特定功能所需的本地信号 ext_capture (x).

根据配置位字段的值 USE_PREV_TDU _INX , USE_PREV_CH_INX 可以使用本地通道 x 或上一通道 x-1 的信号工作。

根据配置位字段 TIM_Modex 的值,可以向下一个通道提供不同的信号 (通过FOUT_NEXT)。

7.5.2 TIM输入源选择

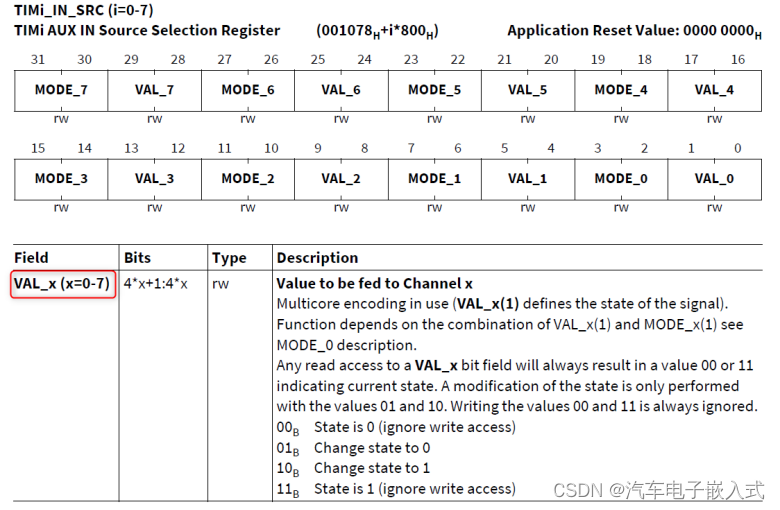

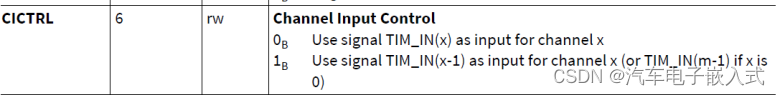

由TIMi_IN_SRC寄存器的VAL_x ,TIMi_IN_SRC寄存器的MODE_x,TIMi_CHx_CTRL寄存器的CICTRL三个信号组合配合TIMi_CHx_ECTRL寄存器的USE_LUT信号来决定TIM?Channel的输入源。

选择1:USE_LUT信号?= 00B

MODE_x = 0, VAL_x = 0: 输入信号由CICTRL信号决定,CICRTL = 0则TIM_IN(x)作为TIM Channel x的输入信号;CICRTL =10则TIM_IN(x-1)?作为TIM Channel x的输入信号。

MODE_x = 0, VAL_x = 1:TIM_AUX_IN(x)作为TIM?Channel x的输入信号。

MODE_x = 1:?VAL_x的状态作为TIM Channel(x)的电平状态,也就恒为高电平1或者恒为低电平0.

由于所有 8 个通道都捆绑在寄存器 TIM[I]_IN_SRC 中,因此可以同步控制所有 8 个输入通道。

通过在相应的 TIM[i] _CH[x]_CTRL 寄存器中设置 CICTRL 位字段,可以组合两个相邻通道。 这允许将一个输入信号上的复杂测量与两个 TIM 通道相结合。

选择2:USE_LUT信号! =00B

7.5.3 输入查看

通过读取 TIM_INP_VAL寄存器 ,可以观察一个硬件单元的所有通道的以下处理阶段的实际信号值:

.?TIM_IN (7:0) TIM输入同步后的信号

. TIM F_IN (7:0) TIM?INPUTSRC选择后的信号?(input to TIM_FLT)

. TIM F_OUT (7:0) TIM过滤后的信号?(output of TIM_FLT)

7.5.4 外部捕获源选择

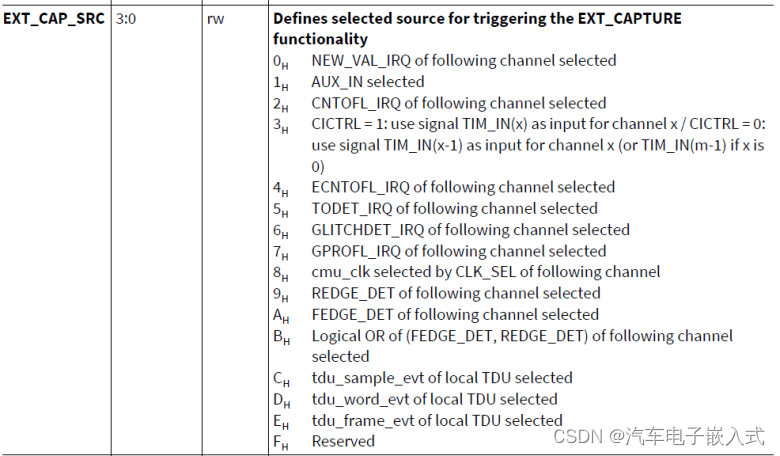

每个通道都可以在外部捕获信号 EXT_CAPTURE 上运行。 用于此信号的源可以通过寄存器 TIM[i] CH[x]_ECTRL 中的位字段 EXT_CAP_SRCx 进行配置。

外部捕获功能通过TIM[I]_CH[x]_CTRL寄存器的EXT_CAP_EN信号配置使能,它将在每个上升边缘触发。 将为选定输入信号 TIM_IN[x] 和 AUX_IN[x] 的每条上升边缘应用脉冲生成。

在某些 TIM 通道模式下,操作可以触发六个 TIM 通道中断源。 或者,也可以使用寄存器 TIM[i] _CH[x+1]_FORCINT 中的相应位通过软触发器发出这些命令。

这个外部捕获功能没怎么理解!!!!

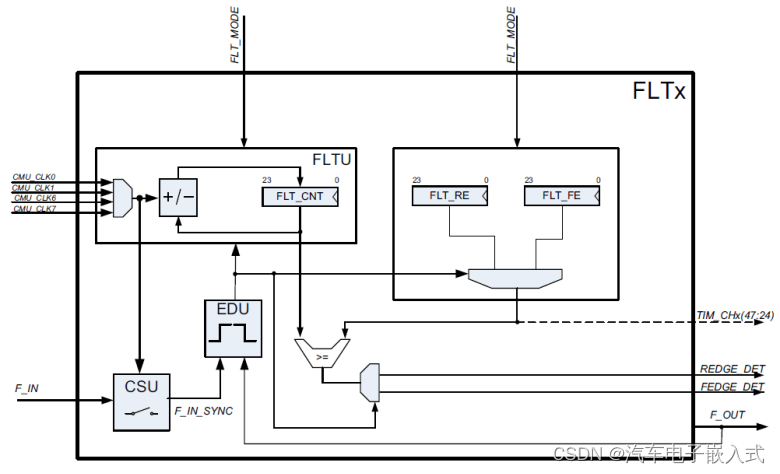

7.5.5 TIM过滤功能

过滤功能模块FLT由时钟同步单元(CSU),边沿检测单元(EDU),过滤计数器(FLTU)组成。

CSU使用的同步时钟由TIM[i]_CH[x]_CTRL寄存器的FLT_CNT_FRQ信号配置。

FLT模块提供以下过滤模式:

. immediate edge propagation mode,

. individual de-glitch time mode (up/down counter), and

. individual de-glitch time mode (hold counter).

. individual de-glitch time mode (reset counter).

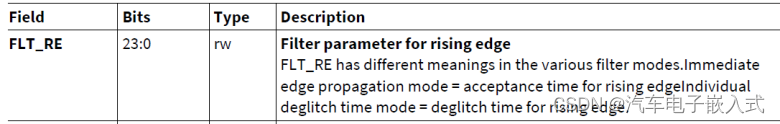

FLT_RE (rising edge)寄存器和FLT_FE (falling edge)寄存器配置不同过滤模式下的时间参数。

过滤时间计算:T=(FLT_xE+1)*TFLT_CLK

不同模式下FLT_RE和FLT_FE的意思

FLT_CNT计数器(没有对应寄存器可以查看)用来测量容错时间。

TIMi_CHx_CTRL寄存器的FLT_CNT_FRQ信号用来配置FLT_CNT的计数时钟。

FLT_CNT, FLT_FE and FLT_RE都是24位信号,如果我们选用的时钟为CMU_CLK0的分辨率(resolution)为50ns,则最大错误消除或者容错时间为838ms.

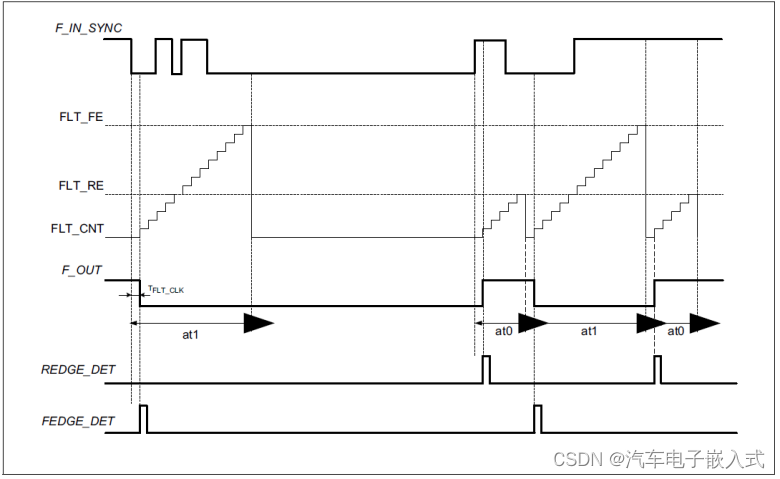

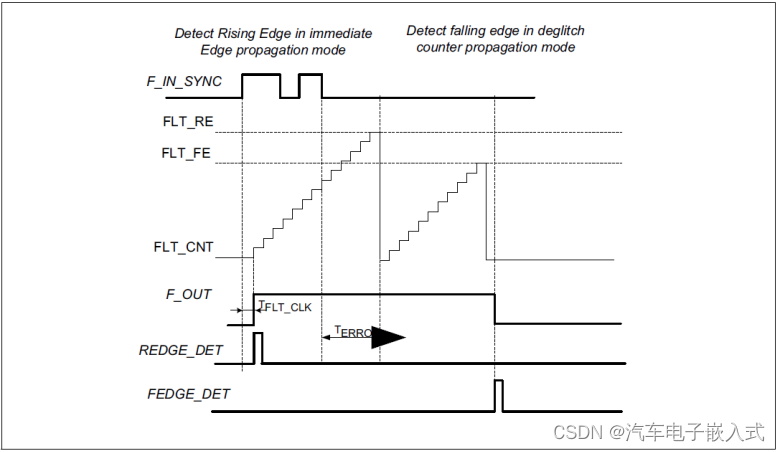

7.5.5.1 Immediate Edge Propagation Mode

理解:

1)FLT_CNT初始状态计数值为0,F_IN_SYNC第一个上升沿到达F_CNT开始上升沿有效时间计数,F_CNT第一次计数的时候F_OUT输出一个高电平,同时REDGE_DET输出一个脉冲标识一个有效的上升沿信号。

2)FLT_CNT继续增加,FLT_CNT在到达FLT_RE这个最小有效阈值(上升沿持续最小时间)前F_IN_SYNC上的跳变沿信号都会被丢弃/忽略。

3)FLT_CNT到达FLT_RE这个最小阈值的时候发现F_IN_SYNC和F_OUT都是高电平状态,FLT_CNT清零等待下一个上升沿到达才开始计数。

理解:

前半部分

1)FLT_CNT初始状态计数值为0,F_IN_SYNC第一个下降沿到达F_CNT开始下降沿有效时间计数,F_CNT第一次计数的时候F_OUT输出一个低电平,同时FEDGE_DET输出一个脉冲标识一个有效的下降沿信号。

2)FLT_CNT继续增加,FLT_CNT在到达FLT_FE这个最小有效阈值(下降沿持续最小时间)前F_IN_SYNC上的跳变沿信号都会被丢弃/忽略。

3)FLT_CNT到达FLT_RE这个最小阈值的时候发现F_IN_SYNC和F_OUT都是低电平状态(一样的电平状态),FLT_CNT清零等待下一次上升到达开始检测。

后半部分

1)F_IN_SYNC上升沿信号到达,F_CNT开始上升沿有效时间计数,F_CNT开始计数的时候F_OUT输出一个高电平,同时REDGE+DET输出一个脉冲标识一个有效的上升沿信号。

2)?FLT_CNT继续增加,FLT_CNT在到达FLT_RE这个有效阈值前F_IN_SYNC上的跳变沿信号被忽略。

3) FLT_CNT到达FLT_RE的时候发现F_IN_SYNC和F_OUT的电平状态不一样,FLT_CNT清零后立马开始下降沿有小有效时间计数,同时F_CNT第一次计数的时候F_OUT输出一个低电平,同时FEDGE_DET输出一个脉冲标识一个有效的下降沿信号。

4)FLT_CNT到达FLT_FE之前F_IN_SYNC上的跳变沿信号都会被忽略。

5)FLT_CNT到达FLT_FE时发现F_IN_SYNC和F_OUT的电平状态不一样,FLT_CNT清零后立马开始上升沿最小有效时间计数,同时F_CNT第一次计数的时候F_OUT输出一个高电平,同时REDGE_DET输出一个脉冲标识一个有效的上升沿信号。

6) 类似过程…

理解Immediate Edge Propagation Mode,后面的几种模式很容易理解。

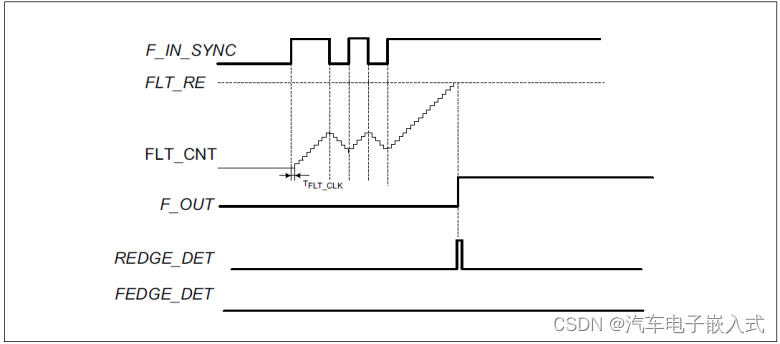

7.5.5.2 Individual De-glitch Time Mode (up/down counter)

7.5.5.3 Individual De-glitch Time Mode (hold counter)

7.5.5.4 Individual De-glitch Time Mode (reset counter)

7.5.5.5 Immediate Edge Propagation and Individual De-glitch Mode

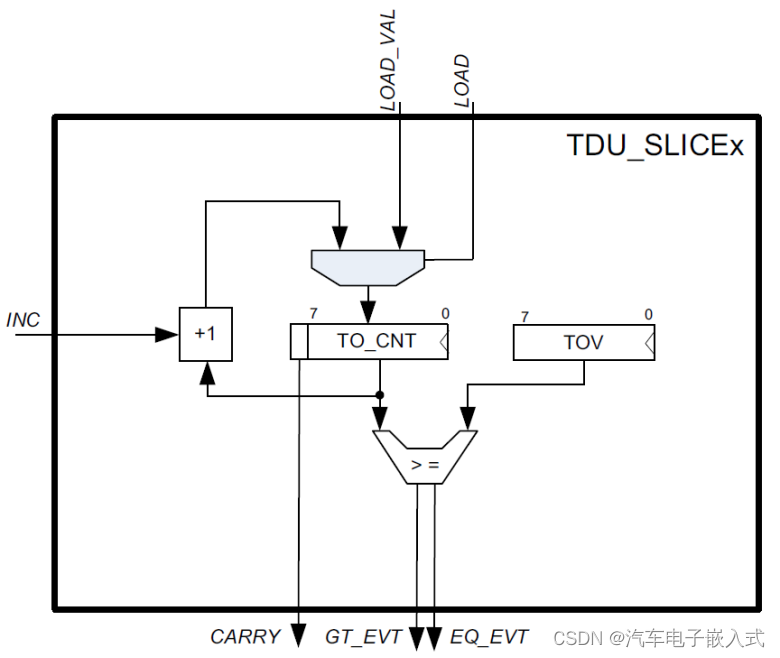

7.5.6 超时检测

超时检测装置 (TDU) 负责对 TIM 输入信号进行超时检测。

TIM 子模块的每个通道都有自己的超时检测装置 (TDU) ,可在相应通道的过滤输入信号上设置超时事件。

Timeout在工程应用中一般可以Disable掉,其内部原理感兴趣的可以去阅读芯片手册。

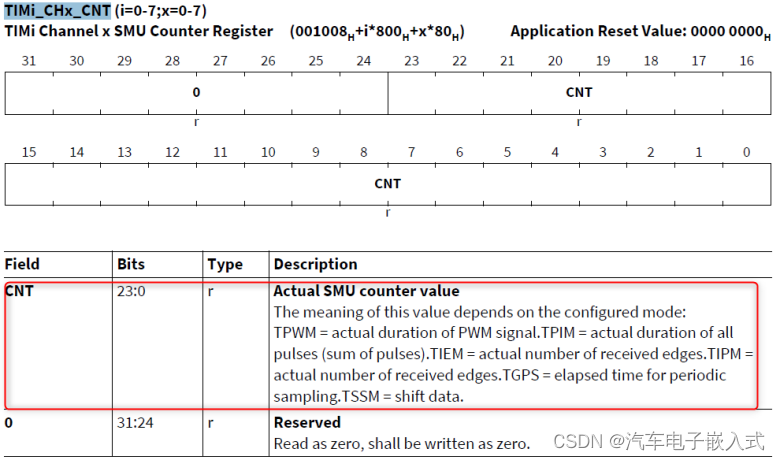

7.5.7 TIM通道架构

TIMi_CHx_ECNT寄存器的ECNT信号是一个边沿计数器。

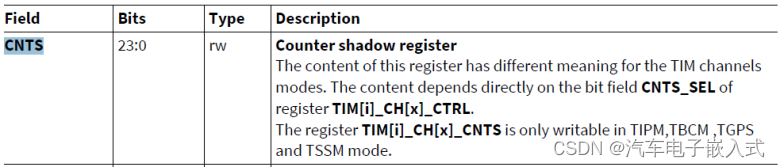

TIMi_CHx_CNT寄存器的CNT信号是计数器,根据Channel模式的不同,器含义不同。

TIMi_CHx_CNTS寄存器的CNTS信号是CNT的Shadow信号。

TIMi_CHx_GPR0,TIMi_CHx_GPR1寄存器的GPR0,GPR1信号根据Channel的模式不同含义不同。

TIM[i]_CH[x]_TDU寄存器的TOV信号来自TDU模块的超时信号。

7.5.8 TIM通道模式

TIM[i]_CH[x]_CTRL寄存器的TIM_MODE信号配置TIM?Channel模式。

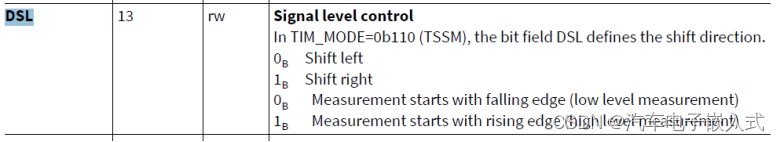

TIM[i]_CH[x]_CTRL寄存器的DSL信号配置TIM?Channel从哪个电平状态开始测量。

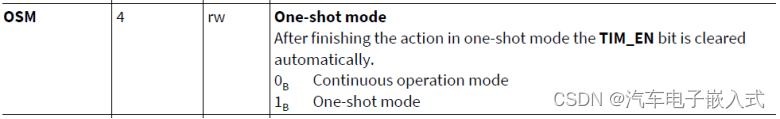

TIM[i]_CH[x]_CTRL寄存器的OSM信号配置TIM?Channel适用一次测量的one-shot模式还是连续测量的continuous模式。

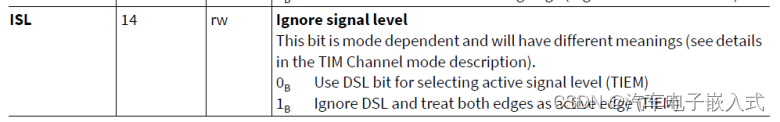

TIM[i]_CH[x]_CTRL寄存器的ISL信号配置TIM?Channel是否使用双边沿测量。

7.5.8 .1 TIM?PWM Measurement Mode (TPWM)

适用场景:TPWM模式适用于PWM信号的周期(Period)和占空比(Duty?Cycle)的测量。

TIM[i]_CH[x]_GPR0寄存器:保存占空比Duty Cycles计数值(Ticks数)。

TIM[i]_CH[x]_GPR1寄存器:保存周期Period计数值(Ticks)。

7.5.8 .2 TIM Pulse Integration Mode (TPIM)

适用场景:TPIM模式适用于测量高脉冲或者低脉冲次数(高还是低由TIM[i]_CH[x]_CTRL.DSL信号配置)。

TIM[i]_CH[x]_GPR0寄存器:保存脉冲数目(高/低电平脉冲由DSL信号决定)。

TIM[i]_CH[x]_GPR1寄存器:保存脉冲数目(高/低电平脉冲由DSL信号决定)。

7.5.8 .3 TIM Input Event Mode (TIEM) ?

适用场景:TPIM模式适用于测量边沿(edges)数目,通过配置DSL及ISL信号可以实现上升沿还是下降沿还是双边沿数目。

TIM[i]_CH[x]_GPR0寄存器:边沿(edges)数目。

TIM[i]_CH[x]_GPR1寄存器:边沿(edges)数目。

7.5.8 .4 TIM Input Prescaler Mode (TIPM)

适用场景:TPIM模式适用于测量边沿(edges)数目,通过配置DSL及ISL信号可以实现上升沿还是下降沿还是双边沿数目。和TIEM不一样的是,中断产生的时机可配置,可以在产生1个,2个,…xxx个edges后产生一个中断。

TIM[i]_CH[x]_GPR0寄存器:边沿(edges)数目。

TIM[i]_CH[x]_GPR1寄存器:边沿(edges)数目。

7.5.8 .5 TIM Bit Compression Mode (TBCM)

复杂模式,将多路TIM Channel信号组合成复杂信号通过ARU路由给其他模块使用。不清楚具体的使用场景。

7.5.8 .6 TIM Gated Periodic Sampling Mode (TGPS)

复杂模式,不清楚具体的使用场景。

7.5.8 .7 TIM Serial Shift Mode (TSSM)

复杂模式,不清楚具体的使用场景。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Nginx 实战闲谈第3讲:Centos7环境下Nginx版本升级

- 炫酷按钮制作(HTML+CSS+Javascript)

- (二)Explain使用与详解

- 2024年腾讯云4核8G服务器最大并发多少?

- 高可用架构

- 前端(二)

- 【Vue】事件修饰符详解

- 【云原生】Kubernetes Operator模式

- Unity inspector绘制按钮与Editor下生成与销毁物体的方法 反射 协程 Editor

- VUE3实现点击按钮下载文件功能