硅的选择性蚀刻

引言

随着CMOS技术缩小到10纳米以下,栅极需要新的MOSFET架构来保持对器件的控制。这种器件的理想架构是环绕栅极(GAA)结构。虽然在前几代器件中,MOSFETs是平面结构,但GAA结构的圆柱形几何形状使得器件制造需要高度选择性的各向同性蚀刻。

本文中我们描述了一种下游H2/CF4/Ar等离子体化学物质,其蚀刻硅,但在Ge和Si0.5Ge0.5上诱导亚纳米厚度碳的净沉积。高选择性是通过使用一个较低的表面温度来获得的,表面温度是通过独立于下游等离子体操作来实现的。由于下游等离子体是在0.1torr或更高的压力下使用的,蚀刻没有离子成分,应该是各向同性的,这是纳米线选择性蚀刻的理想选择。

实验与讨论

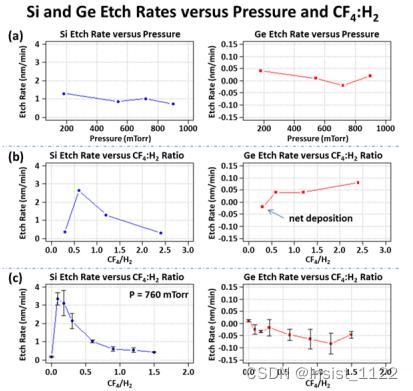

图1显示了压力和CF4流速对硅和锗蚀刻速率的影响。H2/CF4/Ar等离子体可以蚀刻表面(减少质量)或沉积碳质膜(增加质量)。Si和Ge的蚀刻速率很大程度上取决于氟自由基的流量以及表面上的碳自由基的流量,氟自由基与表面反应产生挥发性蚀刻产物(SiF4和GeF4 ),而CxHyFz(g)自由基与表面反应并形成表面结合的*CxHyFz。

当CF4流量增加时,有足够的*CxHyFz来减缓Si的蚀刻。由于在Si和Ge表面上都能形成*CxHyFz物质,因此与Si*CxHyFz相比,Ge*CxHyFz物质对表面钝化更有效。这种差异可能与硅-氟键强度(565千焦/摩尔)与锗-氟键强度(481千焦/摩尔)的差异有关。

图1:硅和锗的蚀刻速率

由于从衬底和薄膜逸出的深度有限,硅和硅锗上的碳层厚度估计约为2毫升。此外,由于反应物和产物必须通过Si和SiGe上的相同膜扩散,所以蚀刻速率不可能受到碳质膜扩散的限制。相反,碳膜对硅和硅锗有不同的影响,它在抑制SiGe的蚀刻方面是很有效的,但在Si上却是无效的。

结论

英思特研究表明选择性是由于H2/CF4/Ar等离子体在Si和Ge或Si0.5Ge0.5上形成的约2 ML厚的CxHyFz层,其对蚀刻的不同抑制性导致的。氟自由基与Ge或Si0.5Ge0.5的放热反应一致,该反应被CxHyFz层强烈抑制,而在Si上,CxHyFz层则不足以完全抑制蚀刻。

在原料气中用D2代替H2会引起反向动力学同位素效应(IKIE ),并增加了约42倍的Si和Si0.5Ge0.5的蚀刻速率,保留了显著的蚀刻选择性。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!