verilog基本语法-时序逻辑基础-记忆单元

概述:

组合逻辑虽然可以构造各种功能电路,但是他有一个缺点就是输入改变时,输出会立即发生改变。因此历史信息不能被保存下来。两个能够保存信息的存储单元被设计出来,用于保存历史信息。一个是锁存器,另外一个是触发器。锁存器是电平敏感的,抗噪能力差,保存信息的准确性受到挑战。通常不会使用锁存器来保存信息,但是在FPGA中,保留了大量的锁存器的功能,这是因为触发器本身是由锁存器构造成的,保留锁存器功能并不会消耗FPGA的额外资源。触发器是边沿敏感的,信息修改只发送在时钟触发的边沿,时钟边沿通常非常短暂,数据修改的时间也非常短,避免了数据被外部干扰。这是设计级联时序逻辑电路非常重要的条件。本节主要介绍verilog构造这些存储单元的使用方法。

内容:

1.锁存器

2.触发器

3.寄存器

4.同步复位电路

5.异步复位电路

6.边沿检测电路

1. 锁存器

代码

module regtest(

input clk, // system clock

input a,

input b,

output reg y, // output signal

output reg y1 // output signal

);

always @ (*) begin

/*if语句锁存器*/

if (a == 1)

y = b ;

/*case语句锁存器*/

case ( a )

0 : y1 = b ;

endcase

end

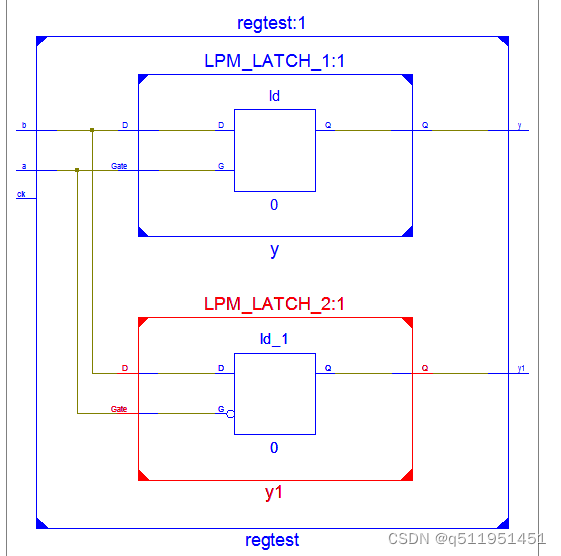

endmoduleRTL结构图,锁存器基本结构D为输入,Q为输出,G为门控电路,不带o的G为高电平修改存储内容,带o的为低电平修改存储内容。此外存储器的clk时钟免疫。

技术原理图,锁存器在FPGA中命名为ld。

2. flip_flop触发器

代码

module regtest(

input clk, // system clock

input rst_n,

input a,

output reg y, // output signal

output reg y1 // output signal

);

always @ (posedge clk ) begin

y <= a ;

end

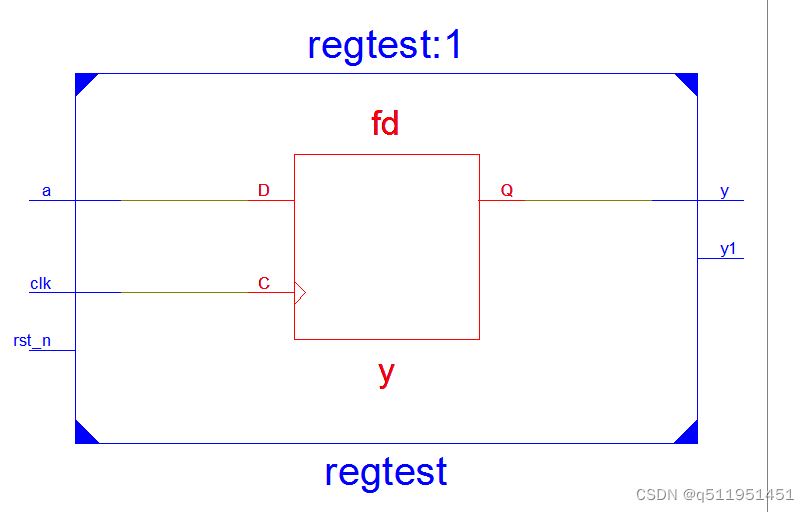

endmoduleRTL结构图,触发器在FPGA中村委fd,D为输入,Q为输出,C为时钟,上升边沿有效,带o的为下降沿有效。

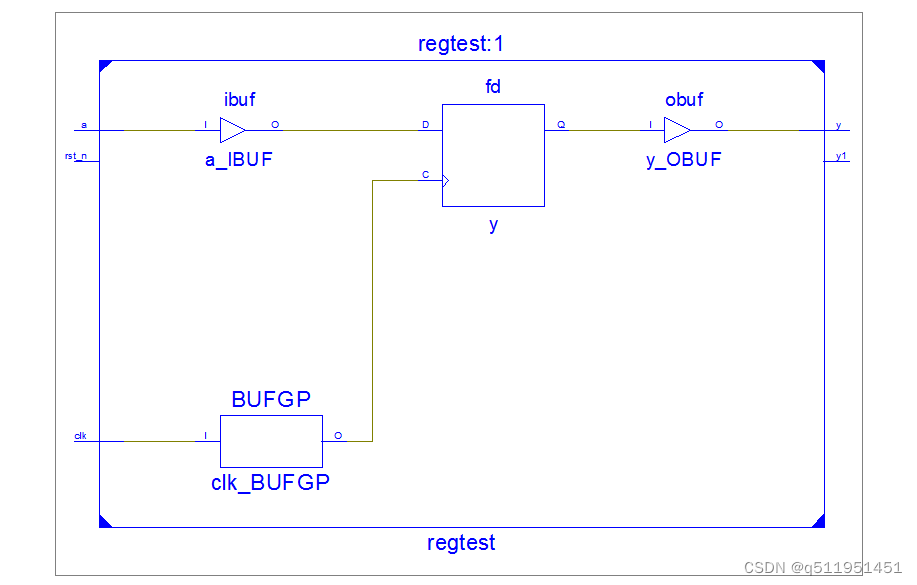

技术原理图,图中显示,除了输入增加了ibuf,输出增加了obuf缓存外,另外增加了bufgp时钟缓存。

3. 寄存器

一个数据往往不仅仅只由1bit构成,而是由多个bit构成,列表8bit层位byte,16bit称为short,32bit称为int,64bit称为..,等数据类型。把多个存储元素捆绑到一起,FPGA称为reg寄存器。他相当于C语言中的变量,它的数据可以修改,但是存储数据的电路不能修改。FPGA的寄存器可以由latch锁存器构成,也可以由flip_flop触发器构成,综合工具根据verilog语法判断,构造的电路是锁存器还是寄存器。

代码示例:

// 3. 寄存器

module regtest(

input clk, // system clock

input rst_n,

input c,

input [7:0] ain,

input [7:0] bin,

output reg [7:0] aByte,

output reg [7:0] bByte

);

// 构造触发器寄存器

always @ (posedge clk ) begin

aByte <= ain ;

end

// 构造锁存器寄存器

always @ (* ) begin

if(c) begin

bByte = bin ;

end

end

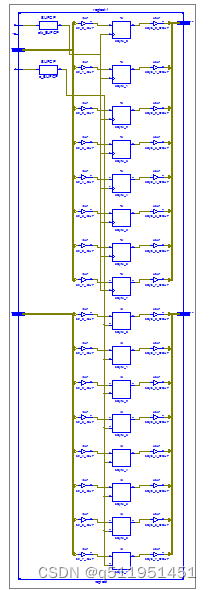

endmoduleRTL结构图

技术原理图,由图可知,锁存器reg由一系列的latch电路构成,触发器reg由一系列的flip_flop构成。

3. 同步复位

代码

module regtest(

input clk, // system clock

input rst_n,

input ain,

output reg areg

);

// 构造触发器寄存器

always @ (posedge clk ) begin

if(rst_n==0) begin

areg <= 0 ;

end else begin

areg <= ain ;

end

end

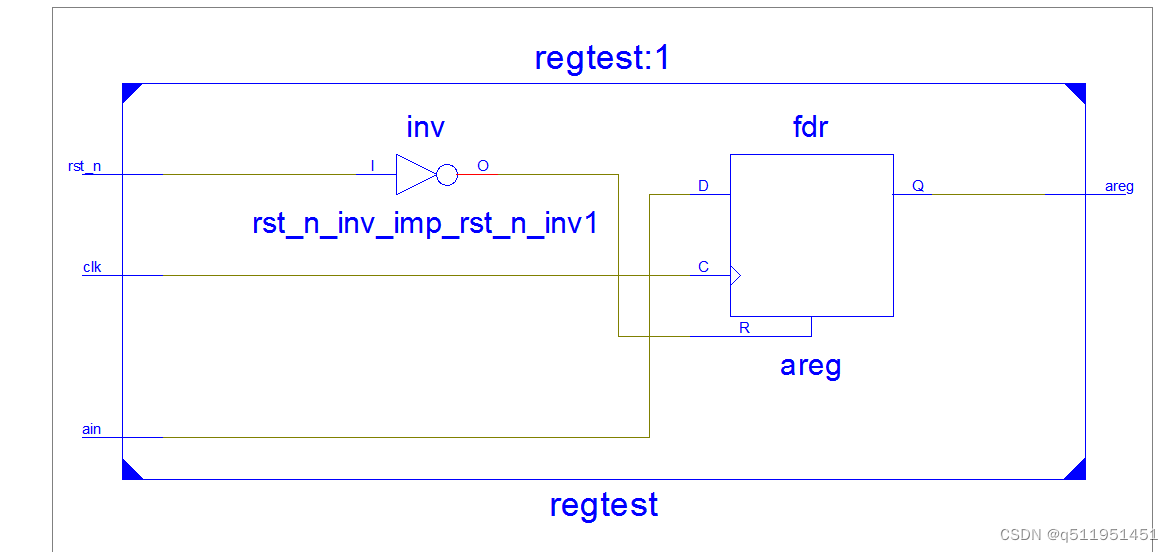

endmoduleRTL结构图,同步复位使用的是fdr触发器。

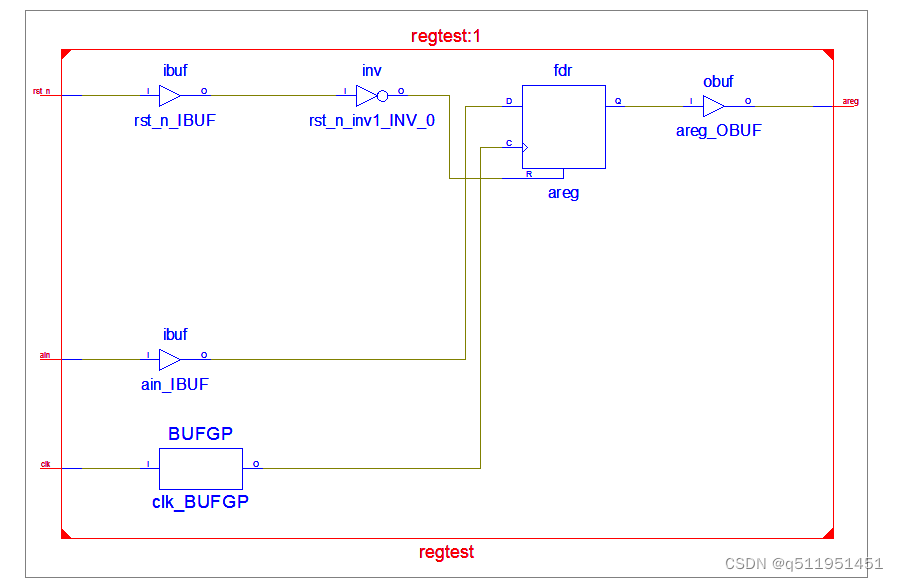

技术原理图

4. 异步复位

代码

module regtest(

input clk, // system clock

input rst_n,

input ain,

output reg areg

);

always @ (posedge clk or negedge rst_n ) begin

if(rst_n==0) begin

areg <= 0 ;

end else begin

areg <= ain ;

end

end

endmodule

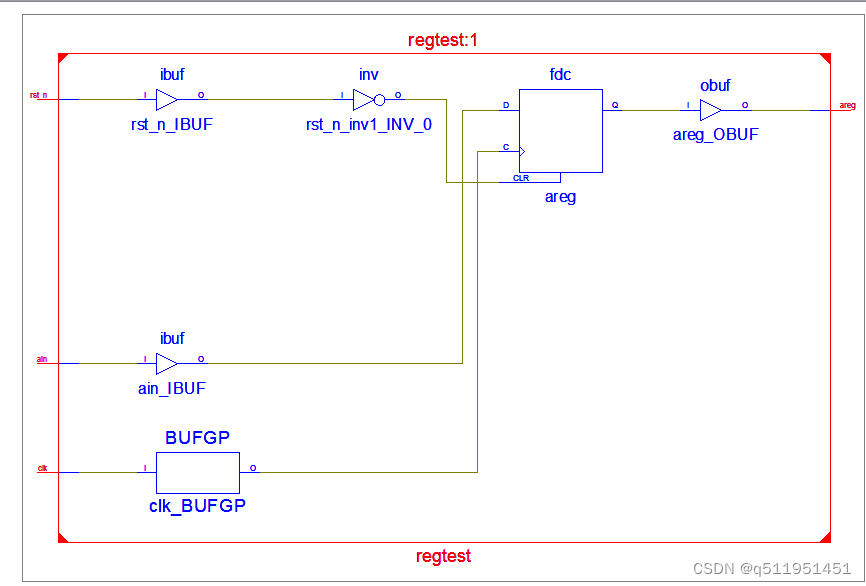

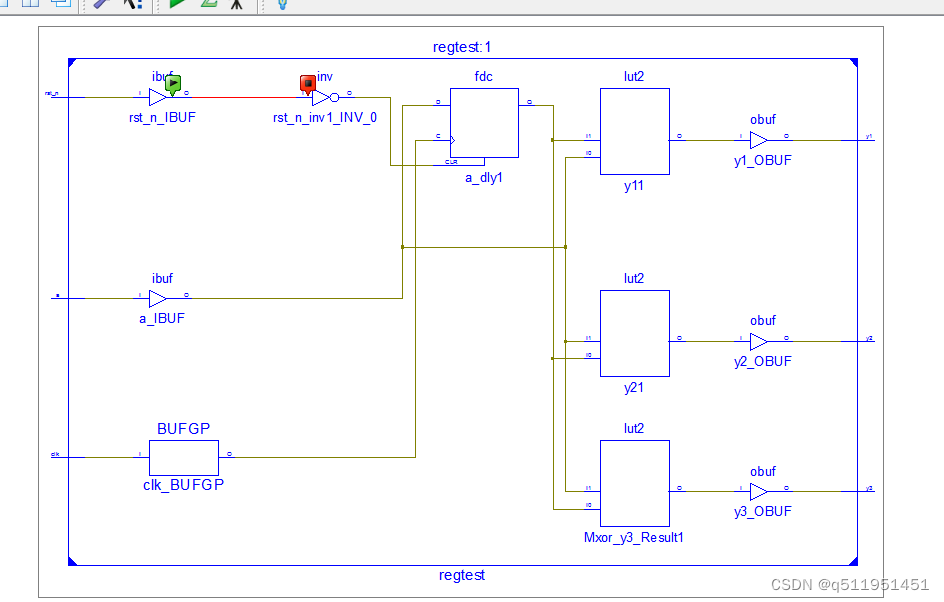

RTL结构图,异步复位FPGA使用的是FDC触发器

技术原理图

5. 边沿检测电路

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input a ,

output y1 , // output signal

output y2 , // output signal

output y3 // output signal

);

reg a_dly1 ;

always @ (posedge clk or negedge rst_n ) begin

if (rst_n == 1'b0)

a_dly1 <= 1'b0 ;

else

a_dly1 <= a ;

end

assign y1 = a & ( ~a_dly1 ) ;

assign y2 = ~a & a_dly1 ;

assign y3 = a ^ a_dly1 ;

endmodule

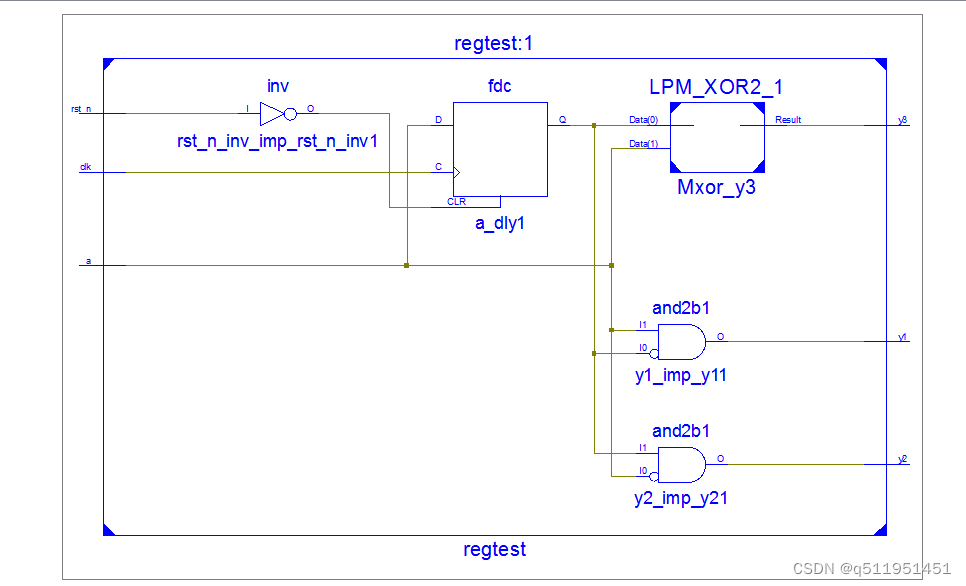

RTL结构图,使用一个同步复位触发器fdc构成寄存器,对输入数据进行一个时钟延时,延时后的结果与数据进行逻辑运算,分别得到上升沿,下降沿,以及双边沿标志位。

技术原理图,触发器使用fdc实现,组合逻辑电路使用Lut查找表实现。所有的时序逻辑都可以看成式组合逻辑与触发器的组合。

6 总结

1. FPGA的存储元素可以由锁存器或者触发器来实现

2. 寄存器代表这存储元素,相当于c语言的变量,数据可以修改,存储数据的电路不能被修改。

3. FDGA提供同步复位触发器和异步触发器,并且保留锁存器,但是一般都不使用。

4. 所有时序逻辑都可以由组合电路+触发器来实现,FPGA的神秘面纱被解开了。他的本质就是用LUT来设计特点组合逻辑功能电路,通过触发器+LUT来设计时序逻辑电路。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- iOS 开发设计 App 上架符合要求的截图

- C++day1

- 软件验收测试计划、验收测试报告案例模板参考

- LeetCode刷题---逆波兰表达式求值

- 设计模式③ :生成实例

- spring 基于注解管理bean @Autowired

- Java中Collections.singletonList的使用

- 宠物热潮席卷欧美:探秘宠物经济的蓬勃发展与增长动力

- 如何用GPT完成论文高效写作?

- JavaWeb笔记之JavaWeb JDBC