数字逻辑实验之利用D触发器,设计并实现三位扭环计数器

发布时间:2023年12月27日

【实验要求】:

采用Moore(摩尔型)电路,利用D触发器,设计并实现三位扭环计数器并用Verilog编程语言写出其代码。

【实验目的】?

- 掌握时序逻辑电路的设计方法;

- 熟悉Vivado2014集成开发环境和;

- 实现如下图所示的三位扭环计数器。

?

?

【实验环境】

- FPGA虚拟仿真平台。

- Vivado2014 集成开发环境。

- Verilog编程语言。

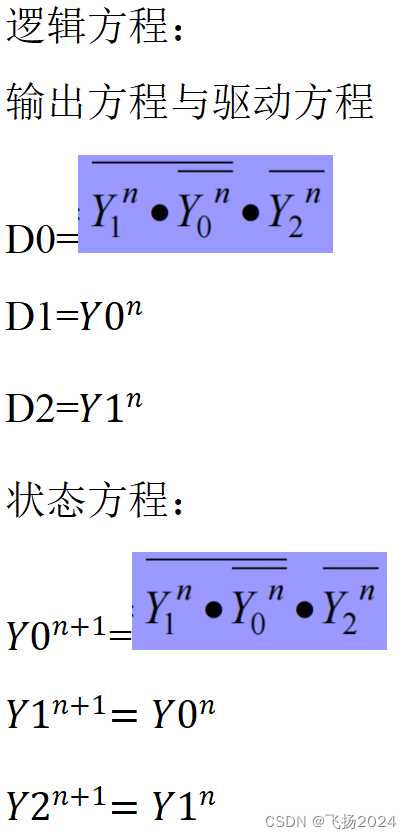

【实验原理】包括:功能描述,真值表,逻辑方程,电路图,Verilog代码实现(硬件映射代码),实验结果或者仿真结果。

功能描述:扭环计数器(Twisted Ring Counter),也称作反向反馈移位寄存器,是一种特殊的移位寄存器。在三位扭环计数器中,输出不仅从最后一个触发器反馈到第一个,而且是反向反馈。因此,在三位的情况下,它会产生一个3位长度的重复序列。

真值表:

| 现态 | 激励函数 | 次态 | ||||||

| Y2(n) | Y1(n) | Y0(n) | D2 | D1 | D0 | Y2(n+1) | Y1(n+1) | Y0(n+1) |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

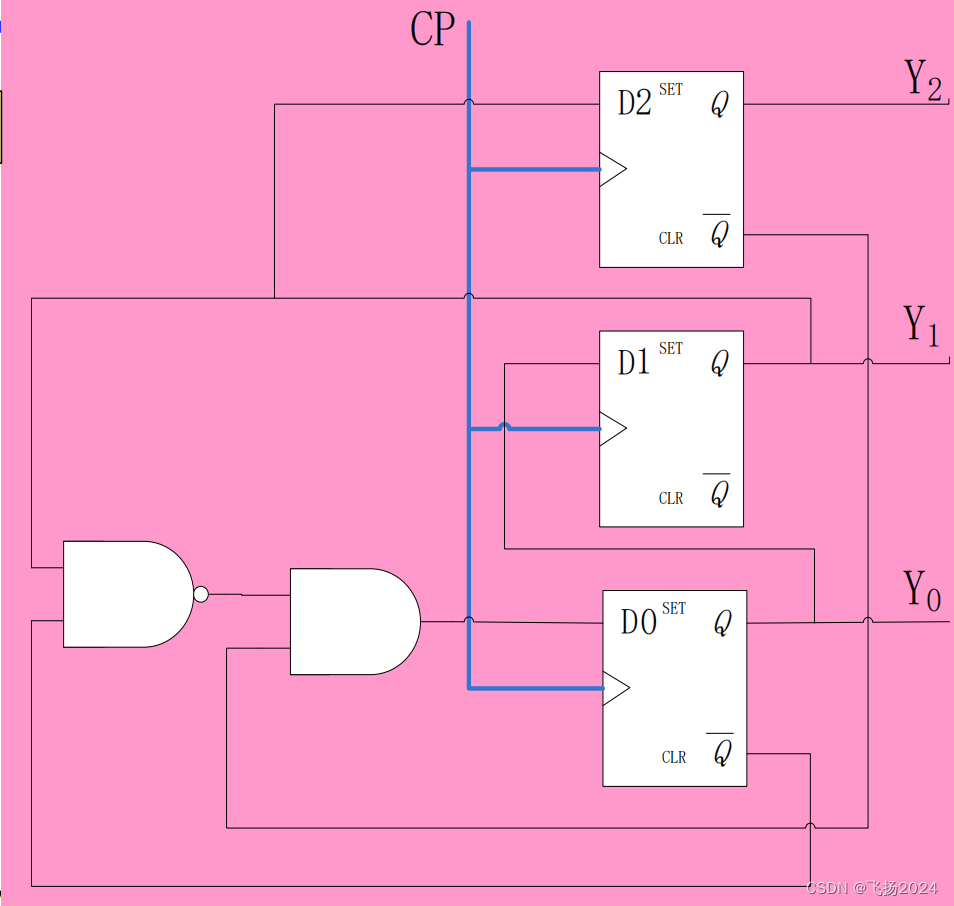

电路图:

代码原理以及实现:

//三位扭环计数器Verilog编程代码

module D(

input clk,

input reset,

input d,

output reg q

);

always @(posedge clk or posedge reset)

begin

if(reset) q<=0;

else?q<=d;

end

endmodule

module circle_3(

input clk,

input rst,

output [2:0] q

);

wire d2,d1,d0;

assign?d0=~q[2]&&~(q[1]&&~q[0]);

assign d1=q[0];

assign d2=q[1];

D dt2(clk, rst,d2,q[2]);

D dt1(clk, rst,d1,q[1]);

D dt0(clk, rst,d0,q[0]);

?endmodule

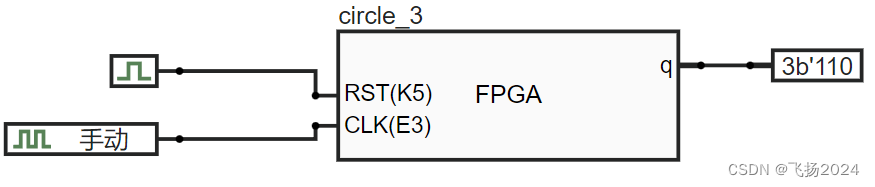

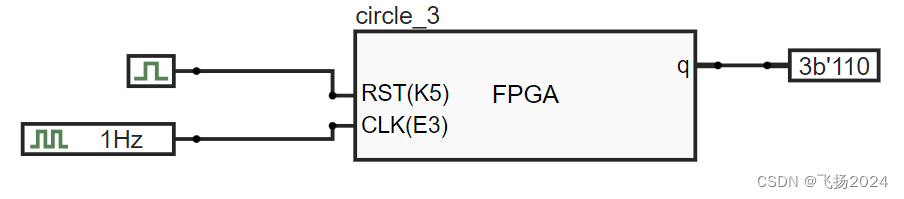

仿真结果(烧写结果):

?

?

点赞关注 不然我会伤心的呀?

文章来源:https://blog.csdn.net/weixin_74461129/article/details/135115612

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!