verilog计数分频

发布时间:2024年01月09日

clk_div.v

module clk_div

(

input rst,

input clk,

input [31:0]max_count_value,

output reg clk_o

);

reg [31:0]cnt;

always@(posedge clk or negedge clk)

begin

if(rst==1'd0)

begin

clk_o<=1'd0;

cnt<=0;

end

else

begin

if(cnt==max_count_value)

cnt<=1;

else

cnt<=cnt+1;

if(cnt==0 || cnt==max_count_value/2 || cnt==max_count_value)

clk_o<=~clk_o;

end

end

endmodule

clk_div_tb.v

`timescale 1ns / 1ps //单位ns,精度ps

module tb_clk_div();

//输入

reg clk;

reg rst;

//输出

wire clk_o;

/*

比如用系统时钟生成串口波特率为115200的时钟,则Freq1为系统时钟频率,

Freq2=115200

*/

parameter Freq1=32'd100_000_000;

parameter Freq2=(Freq1*32'd2)/32'd3;

//实例化

clk_div u0(

.rst(rst),

.clk(clk),

.max_count_value(32'd2*Freq1/Freq2),

.clk_o(clk_o)

);

initial

begin

clk=1'd0;

rst=1'd0;

#20;//等待20ns,以完成复位

rst=1'd1;

end

//1s=10^3ms=10^6us=10^9ns

//f=100MHz=10^8Hz,T=10ns

always

#5 clk=~clk; //每隔5ns时钟翻转,即周期为10ns的时钟信号

endmodule

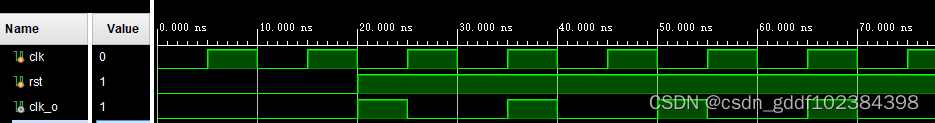

仿真波形:

文章来源:https://blog.csdn.net/csdn_gddf102384398/article/details/135479696

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- layui文本编译器支持多图上传,图片上传排序,删除图片功能

- 性能测试-jemeter:安装 / 基础使用

- momentum2靶机

- Linux | 20 个常用的 Linux 基本指令

- 1500千头养猪场污水处理设备技术方案

- vue保姆级教程----深入了解 Vue Router的工作原理

- Eva.js是什么(互动小游戏开发)

- 回归预测 | Python基于Encoder-TCN-BIGRU-Decoder多变量回归预测

- Redis Cluster基于客户端对mget的性能优化

- Java Redis 和 memcache 有什么区别?