[verilog] Verilog 数值表示

主页: 元存储博客

前言

Verilog中,可以使用多种方式表示数值。

1. 整数表示

1.1 整数数据类型

基数格式共有四种,分别是十进制('d 或 'D),十六进制('h 或 'H),二进制('b 或 'B),八进制('o 或 'O)。数值可以指定位宽,也可以不指定位宽。

二进制表示法:以’b’或’B’为前缀,后跟一串0和1的数字序列。例如,4位宽的二进制数值可以表示为4’b1010。

八进制表示法 , 以’o’ 或 ‘O’ 为前缀, 如八进制数77, 8’o77。八进制数值77转换为十进制表示是63。

十进制表示法:直接使用十进制数字表示。例如,十进制数值23可以表示为8’d23, 也可直接用 23。

十六进制表示法:以’h’或’H’为前缀,后跟一串0-9和A-F的数字序列。例如,8位宽的十六进制数值可以表示为8’h7F。32’h3022_c0de // 32bit 的十六进制数值,下划线 _ 是为了增强代码的可读性。

整数表示法:使用整数变量声明和赋值。例如,使用整数变量n表示数值100可以表示为integer n = 100。

1.2 整数转换函数

Verilog提供了一些系统函数来处理整数。

$dec():将十六进制或二进制表示的整数转换为十进制数。

$bin():将十进制或十六进制表示的整数转换为二进制数。

$hex():将十进制或二进制表示的整数转换为十六进制数。

module integer_example;

reg [7:0] binary_num = 8'b11001011;

reg [15:0] decimal_num = 134;

reg [7:0] hex_num = 8'hCB;

initial begin

$display("Binary number: %b", binary_num);

$display("Decimal number: %d", decimal_num);

$display("Hexadecimal number: %h", hex_num);

$display("Decimal representation of binary number: %d", $dec(binary_num));

$display("Binary representation of decimal number: %b", $bin(decimal_num));

$display("Hexadecimal representation of decimal number: %h", $hex(decimal_num));

end

endmodule

结果:

Binary number: 11001011

Decimal number: 134

Hexadecimal number: CB

Decimal representation of binary number: 203

Binary representation of decimal number: 10000110

Hexadecimal representation of decimal number: 86

2. 负数表示

在Verilog中,负数可以使用有符号二进制补码表示法表示。有符号二进制补码表示法中,最高位(MSB)用来表示符号,0表示正数,1表示负数。其余位表示数值部分。

在进行运算时,Verilog会根据这种表示法进行符号扩展和溢出处理。例如,如果要对两个8位的有符号数进行相加,Verilog会自动进行符号扩展和溢出处理,以保证运算结果正确。

在Verilog中,负数可以使用两种表示方式:补码和符号-数(Sign-Magnitude)。下面分别介绍这两种表示方式的实践。

符号-数表示法: 符号-数表示法是另一种表示负数的方法。在符号-数表示法中,最高位为符号位,0表示正数,1表示负数,其余位表示数值的二进制表示。

例如,假设我们要表示-5,将5的二进制表示为0101,然后将最高位改为1得到符号-数表示:1101。所以-5的符号-数表示为1101。

在Verilog中,可以使用固定位数的有符号数据类型(如reg signed)来表示符号-数。例如,可以声明一个8位有符号变量来表示-5:

reg signed [7:0] num; assign num = 8'sb1101;

补码表示法: 补码是最常用的表示负数的方法。在补码表示法中,最高位为符号位,0表示正数,1表示负数。补码的数值计算方式为:正数的补码与其本身相同,负数的补码等于其绝对值的反码加1。

例如,假设我们要表示-5,首先将5的二进制表示取反得到反码:0101 -> 1010,然后将反码加1得到补码:1010 + 1 = 1011。所以-5的补码表示为1011。

在Verilog中,可以使用固定位数的有符号数据类型(如reg signed)来表示补码。例如,可以声明一个8位有符号变量来表示-5:

reg signed [7:0] num; assign num = 8'sb1011;

需要注意的是,补码表示法在进行数值计算时更方便,因为在补码的加减运算中,可以直接按照二进制数的运算规则进行操作。而符号-数表示法在进行数值计算时需要进行额外的处理,如判断符号位并进行特殊计算。因此,在大多数情况下,补码表示法更常用。

3. 实数表示

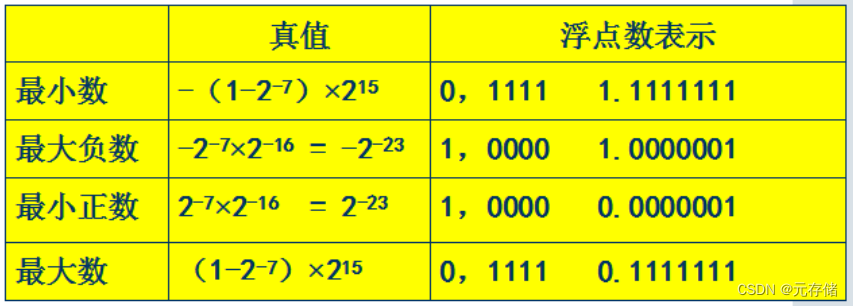

Verilog中的实数可以用固定的点表示法或浮点表示法来表示。

固定点表示法使用一个固定的小数点位置来表示实数。例如,如果我们选择小数点在整数部分的最后一位后面,那么实数3.14就可以表示成314。在Verilog中,可以使用整数类型来表示固定点数,并使用一个参数来指定小数点的位置。

浮点表示法使用科学计数法来表示实数,包括一个尾数和一个指数。在Verilog中,可以使用实数类型来表示浮点数。

下面是一些示例,演示了如何使用固定点表示法和浮点表示法来表示实数:

使用固定点表示法:

parameter FIXED_POINT = 16; // 小数点的位置

reg [31:0] fixed_point_number;

initial begin

fixed_point_number = 3.14 * (1 << FIXED_POINT);

$display("Fixed point number: %d", fixed_point_number);

end

使用浮点表示法:

reg [31:0] float_number;

initial begin

float_number = 3.14;

$display("Floating point number: %f", float_number);

end

在Verilog中,实数类型使用32位浮点数表示,其中24位用于尾数,8位用于指数。因此,在浮点表示法中,实数的精度会有限。为了提高精度,可以使用更高位数的固定点表示法。

4. 逻辑电平表示

Verilog HDL 有下列3种基本的值来表示硬件电路中的电平逻辑:

0:逻辑 0 或 “假”

1:逻辑 1 或 “真”

z 或 Z:高阻

z 意味着信号处于高阻状态,常见于信号(input, reg)没有驱动时的逻辑结果。

5. 逻辑值表示

逻辑值可以用以下两个关键字来表示:

0(代表逻辑低,表示逻辑“假”或“假设”)

1(代表逻辑高,表示逻辑“真”或“成立”)

这两个关键字分别用于表示逻辑门的输入和输出值。在Verilog中,逻辑值可以用于描述和表达逻辑门的功能和行为。逻辑值可以用于逻辑门之间的连接,以实现数字电路的功能。

用逻辑值true和false来表示布尔数据。例如,真值true可以表示为1’b1。

6. 字符表示法

用ASCII码或Unicode编码表示字符数据。例如,字符’A’可以表示为8’h41’。

7. 字符串表示

字符串可以用字符串字面值表示,字符串字面值被包围在双引号(")或单引号(')之间。

使用双引号表示字符串:

module example;

reg [7:0] data = "Hello";

initial begin

$display("%s", data);

end

endmodule

使用单引号表示字符串:

module example;

reg [7:0] data = 'Hello';

initial begin

$display("%s", data);

end

endmodule

Verilog中还支持转义序列来表示特殊字符,如换行符(\n),制表符(\t),回车符(\r)等。

module example;

reg [31:0] data = "Hello\nWorld!";

initial begin

$display("%s", data);

end

endmodule

字符串"Hello\nWorld!“被赋值给32位寄存器data,当打印出来时,”\n"将被解释为换行符。

参考文献

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 盘点好用内容合规监测工具

- CentOS 7.9 安装PostgreSQL以及配置服务

- 《Linux系列》Linux磁盘MBR分区扩容

- Nature | Baker团队用AI设计出史上最高互作强度的蛋白质

- 人工智能与数据分析:新时代的趋势和机会

- 微信小程序之WXSS模板样式、页面配置(.json)和网络数据请求

- 软件测试/测试开发/测试管理丨Page Object模式:为什么它是Web自动化测试的必备工具

- 二叉树 经典例题

- SRv6 报文转发

- 万界星空开源MES/注塑MES/开源注塑MES/免费MES/MES源码