数字IC设计入门超详细步骤!看这一篇就够了!

看到很多小伙伴都不了解数字IC设计该怎么学,下面就来给大家来具体讲讲。

其实对于初级数字 IC 设计工程师而言,不仅仅需要较好的 Verilog 语法功底,还要熟悉企业的 Linux 环境以及 EDA 工具,此时你就需要掌握 Shell,Vim,SVN 等公司操作环境,以及 VCS,Verdi,SpyGlass 等公司开发环境。

随着工艺的发展,芯片肯定是尺寸越来越小,至于小到什么样的程度是极限,这很难知道。但不管怎么去生产制造,我们讲时序,你 set up,任何时候都是 set up,这是属于一个基本性的东西,基本上跟你工艺的情况关系不大。

不管你是2纳米的也好,还是200 纳米,我们讲 2000 纳米的这样一个工艺,基础性的东西是一定的,你可能会碰到额外的问题,比如功耗。

建议大家,去打好技术的基础,我们讲了rtl,特别是sta,特别是电路方面的基础。将来你去做不管是 2 纳米也好,5 纳米也好,方法基本上都是类似的,只是迭代的次数更多一点而已。

数字 IC 设计是有一定的门槛的,入门需要需要掌握许多知识点和技能。

- 了解数字系统基础知识:掌握了解数字系统的基本概念、逻辑门电路、计算机体系结构等知识,可以从网络上找到一些较好的入门课程和教材。

- 学习EDA工具:掌握EDA工具(集成电路设计工具),了解最常用的仿真、静态时序分析工具和器件模拟等软件,比如:Cadence、Mentor Graphics等,可以通过相关网站申请试用版的EDA工具进行学习和实践。

这里给大家放个口:数字IC设计资料

各阶段主要工作及EDA工具

芯片架构:根据项目需求确定架构,输出设计规格说明书(design spec)

RTL设计:利用硬件描述语言对电路进行寄存器传输级(RTL)的描述

RTL仿真:检验RTL设计代码是否实现了spec描述的功能,也称为前仿真,综合后再进行的仿真称为后仿真(时序仿真)——工具VCS、NC、Modelsim

逻辑综合:把RTL设计代码映射到特定的工艺库上,添加约束文件,输出成门级网表Netlist——工具DC

形式验证:从功能上对综合后的网表进行验证,保证综合过程中没有改变原先HDL描述的电路功能,常用的就是等价性检查方法——工具Formality

静态时序分析:STA,在时序上对电路进行验证,检查电路是否存在建立时间和保持时间的违例——工具PT

DFT:扫描链插入,使设计中的所有寄存器可以通过设计的输入输出进行控制和观察,用于在芯片生产之后测试芯片的良率

布局布线:布局(确定各种功能电路的摆放位置),时钟树的插入(时钟信号的布线),布线(普通信号的布线)——工具ICC、Innovus

寄生参数提取:提取延迟信息

静态时序分析:加入了布局布线延迟,更真实的时序分析 ——工具PT

版图验证:DRC设计规则检查/LVS版图一致性检查——工具Calibre、Hercules、Diva/dracula

3.学习数字电路和优化方法:掌握数字电路的设计方法和常见的电路结构,了解常见的数字电路优化方法,有助于提高电路的性能和可靠性。

4.掌握常用的数字IC设计流程:可以学习数字IC设计流程,有助于更深入地理解数字IC设计的实现方式和流程。

数字IC设计流程

确定项目需求

确定芯片的具体指标:功能、功耗、性能、IO外设等

市场来提出需求,研发来评估需求

系统级设计

用系统建模语言对各个模块描述

由系统工程师完成

前端设计【逻辑】

RTL设计、RTL仿真(EDA仿真验证)、硬件原型验证(FPGA硬件原型验证)、电路综合(RTL代码映射(MAP)成门级网表(STD CELL))

后端设计【物理】

版图设计、物理验证、后仿真等

5.实践项目:了解常用数字IC设计模块的设计与开发流程,尝试开发简单的有限状态机/逻辑模块或仿真程序等。

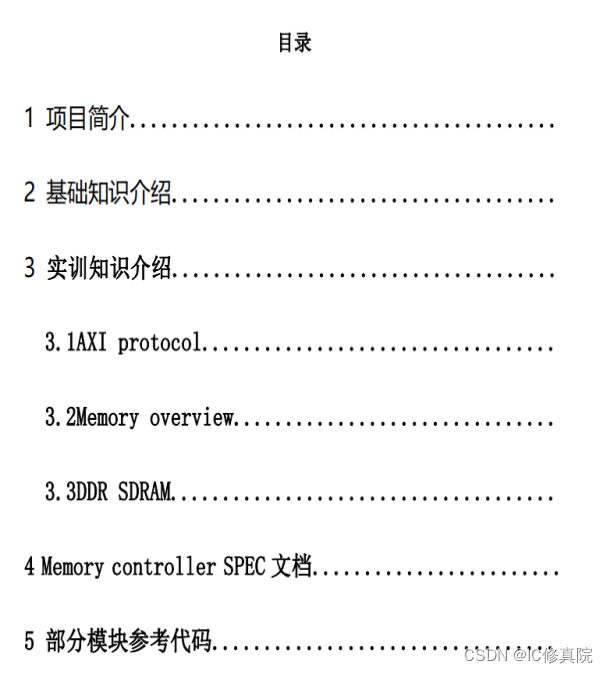

本项目设计完成了一个 memory controller 模块,实现了对 array read/write/refresh的控制,其接口完成了 AXI bus 到 array interface 之间的转换。

ASIC设计流程

数字前端

看完之后大家学会了吗?如果你还是没有学习思路的话,也可以跟行业内工程师具体了解一下学习的方向和方法。上面所涉及到的资料也可以分享给大家。

这里给大家放个口:数字IC设计资料

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 神经网络可以计算任何函数的可视化证明

- 银河麒麟v10 安装mysql 8.35

- 外包干了2个月,技术退步明显.......

- 基于果蝇算法优化的Elman神经网络数据预测 - 附代码

- 项目运行报错集锦

- 把Vue3模板复用玩到了极致,少封装几十个组件!

- MFC使用高速绘图控件high-speed Charting Control绘制柱形图

- 实战10 角色管理

- 旧书回收小程序搭建,实现旧书回收再利用

- 【深度学习-目标检测】05 - YOLOv1 论文学习与总结