ZYNQ程序固化

将程序存储在非易失性存储器中,在上电或者复位时让程序自动加载运行。

这个过程需要启动引导程序( Boot Loader)参与,Boot Loader会加载FPGA配置文件,以及运行在ARM中的软件应用。

一、简介

ZYNQ Soc的启动和配置过程中,既需要PS的配置信息,又需要PL的配置信息。

ZYNQ系列是没有办法只固化PL的程序的(NorFlash、SD卡等是连接在PS端的)。

PS 支持多种片外非易失性存储器(Quad SPI Flash,NAND Flash,NOR Flash 或 SD 卡)。

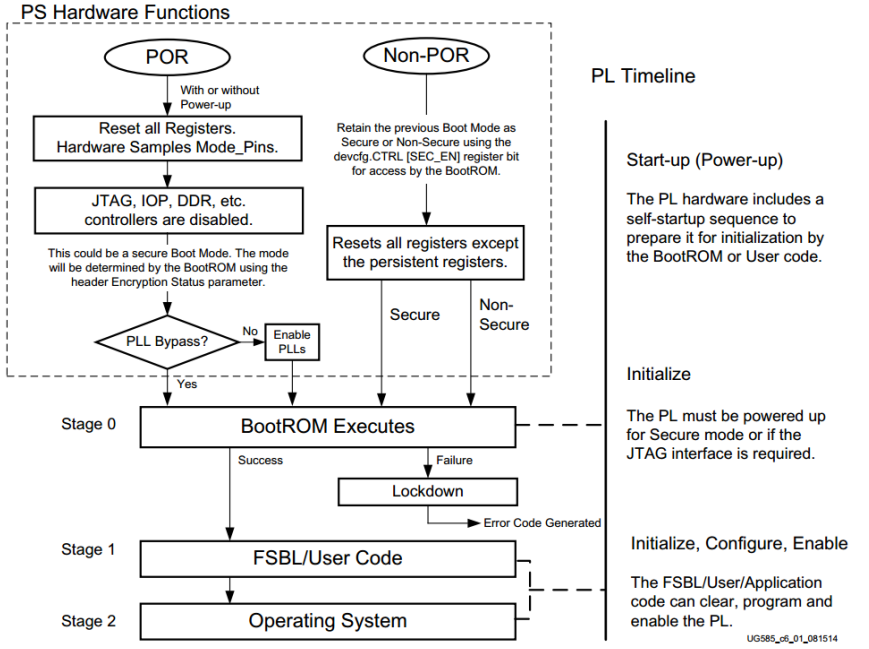

ZYNQ SoC 的启动由片上的 BootROM 开始。

片上 BootROM 是 ZYNQ 芯片上的一块非易失性存储器, 它包含了 ZYNQ 所支持的配置器件的驱动,里面的代码是不可修改的。

BootROM 中的代码首先会在片外的非易失性存储器中寻找一个头文件,头文件里定义了一些启动信息,用于配置 BootROM 的运行。

BootROM 执行之后,下一个配置阶段被称为 First-Stage Boot Loader(FSBL),它是由设计者所创建的。 FSBL 可以配置 DDR 存储器和硬件设计过程中所定义的一些外设。这些器件需要在加载软件应用及配置 PL 之前就初始化完毕。

FSBL 的工作内容:

- 初始化 PS

- 如果提供了 BIT 文件,则配置 PL

- 加载裸机应用程序到 DDR 中

- 开始执行裸机应用程序

PL 的配置是通过处理器配置访问接口(Processor Configuration Access Port,PCAP)进行的,它允许对 PL 进行部分配置或者完全配置。

ZYNQ 的启动镜像需要如下文件:

- Boot ROM 头文件,控制 Boot ROM的设置

- First-Stage Boot Loader,FSBL文件

- PL 配置文件,即 BIT 文件

- PS软件应用程序,即ELF文件

Boot ROM Header文件是自动生成的。

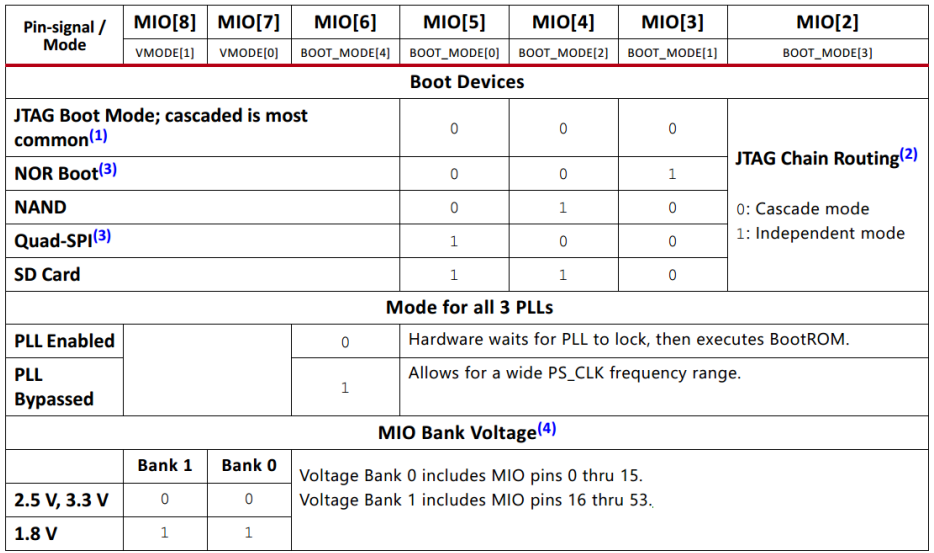

ZYNQ SoC 使用多个模式引脚来决定配置器件的类型、软件的存储位置以及其他的系统设置,这些引脚共享PS 端的MIO 引脚。

总共有 7 个模式引脚,分别为 MIO[8:2],前四个引脚定义启动模式,第五个引脚定义是否使用 PLL,第六个和第七个引脚定义上电过程中 MIO bank0 和 bank1 的 bank 电压。

通常模式下,锁相环PLL是启动的,PS-CLK提供时钟信号,经过三路PLL:

- ARM PLL,产生时钟用于CPU和互联

- IO PLL,产生时钟用于IO外围设备

- DDR PL,产生时钟用于DDR、DRAM 控制器和AXI-HP接口

在上电复位(Power On Reset,POR)之后,硬件会采集模式引脚的状态,禁用器件内部的模块,并根据模式引脚的设置选择是否使能 PS 的时钟锁相环。

整个系统的启动过程如下图

二、固化操作

2.1 生成固化文件

在Block Design 的ZYNQ Processing System模块中要使能SD外设和QSPI外设。

- 使能SD外设,将程序固化到SD卡中。

- 使能QSPI外设,将程序固化到Flash中。

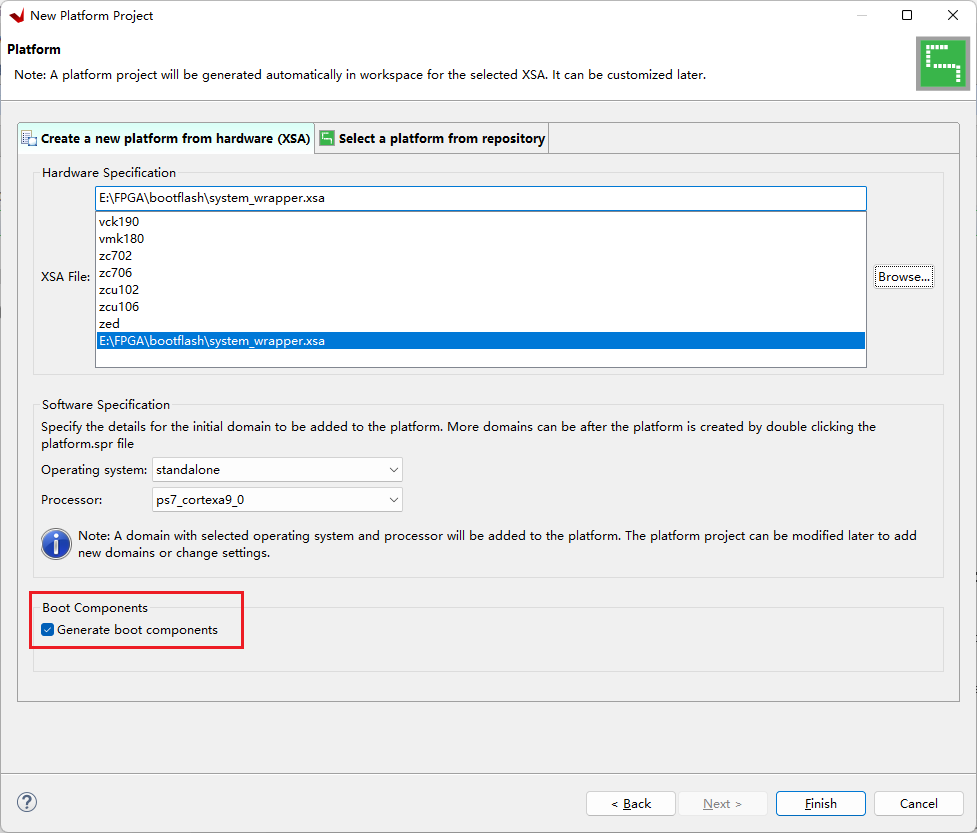

在创建platform的步骤中需要勾选Generate boot components (生成启动组件)选项,勾选之后,软件会自动在硬件平台工程里生成 fsbl 的相关文件。

工程编译后,在系统工程和应用工程下会各自生成一个Debug文件夹。

- 系统工程下的 Debug 文 件里包含的是 BOOT.BIN(固化文件)

- 应用工程下的 Debug 文件里包含的是 elf文件(应用工程烧录文件)

同时,硬件平台工程文件夹下也生成了 fsbl.elf(启动引导文件)

也可以手动生成BOOT.BIN文件

bif文件是BOOT.BIN文件的参数描述。

3个文件的添加顺序不能乱。

2.2 固化到SD卡

将生成的 BOOT.bin 文件拷贝到 SD 卡根目录下。(SD卡文件系统为FAT32格式)。

将板卡启动模式设置为从SD卡启动。

2.3 固化到Flash

将程序固化到 QSPI Flash 需要使用 JTAG 下载器。( 此时要设置为从JTAG启动 )

Vitis 软件的菜单栏中点击"Xilinx->Program Flash"。

在弹出的 Program Flash Memory 界面中中配置BOOT.BIN文件路径和FSBL文件路径。

点击"Program",开始对 Flash 进行编程。

Flash编程完成后,将板卡启动模式设置为从QSPI Flash启动。

参考

【正点原子】启明星ZYNQ之嵌入式Vitis开发指南v1_2

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Redis命令 - Lists命令组常用命令

- Shape-IoU:考虑边框形状与尺度的度量

- 【软件工程】走近演化过程模型:软件开发的不断进化之路

- oracle materialized views 是啥

- 微信小程序内部跳到外部小程序

- 虚拟化技术、Docker、K8s笔记总结

- Milvus数据一致性介绍及选择方法

- STM32 Uart中断发送打印乱码问题记录

- 叠加文件夹内所有png文件 python

- 找出前缀异或的原始数组