《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(3)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(2)

2.1 存储器域与PCI总线域

2.1.2 PCI总线域

在x86处理器系统中,PCI总线域是外部设备的重要组成部分。实际上,在Intel的x86处理器系统中,所有的外部设备都使用PCI总线管理。而AMD的x86处理器系统中还存在一条HT(HyperTransport)总线,HT总线的主要目的是替代FSB(Front Side Bus)总线,但是也可以作为本地总线连接一些高速设备即HT设备,因此在AMD的x86处理器系统中还存在HT总线域。本书不对HT总线做进一步介绍。

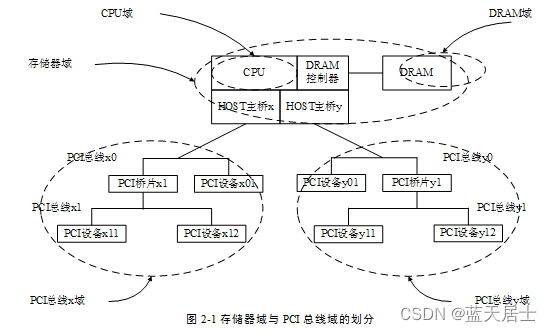

PCI总线域(PCI Segment)由PCI设备所能访问的地址空间组成。在一个处理器系统中,可能存在多个HOST主桥,因此也存在多个PCI总线域。如在图2-1所示的处理器系统中,具有两个HOST主桥,因而在这个处理器系统中存在PCI总线x和y域。

在多数处理器系统中,分属于两个PCI总线域的PCI设备并不能直接进行数据交换,而需要通过FSB进行数据交换。值得注意的是,如果某些处理器的HOST主桥支持Peer-to-Peer数据传送,那么这个HOST主桥可以支持不同的PCI总线域间的数据传送。

PowerPC处理器使用了OCeanN技术连接两个HOST主桥,OCeaN可以将属于x域的PCI数据请求转发到y域,OCeaN支持PCI总线的Peer-to-Peer数据传送。

2.1.3 处理器域

处理器域是指一个处理器系统能够访问的地址空间的集合(对比上边,PCI总线域由PCI设备所能访问的地址空间)。处理器系统能够访问的地址空间由存储器域和外部设备域组成。其中,存储器域地址空间较为简单;而在不同的处理器系统中,外部设备域的组合结构并不相同。如在x86处理器系统中,外部设备域主要由PCI总线域组成(上边已提到),因为大多数外部设备都是挂接在PCI总线上的;而在PowerPC处理器和其它处理器系统中,有相当多的设备与FSB直接相连,而不与PCI总线相连。

本书仅介绍PCI总线域而不对其它外部设备域进行说明。其中,存储器域与PCI总线域之间通过(由)HOST主桥联系在一起。深入理解这些域的关系是深入理解PCI体系结构的关键所在,实际上这也是理解处理器体系结构的基础。

通过HOST主桥,处理器系统可以将处理器域划分为存储器域和PCI域。其中,存储器域与PCI总线域彼此独立,通过HOST主桥进行数据交换。HOST主桥是联系存储器域和PCI总线域的桥梁,是PCI总线域的实际管理者。

有些书籍认为HOST处理器是PCI总线域的管理者,这种说法并不准确(这一点,在第1章中一提到)。假设在一个SMP处理器系统中,存在4个CPU而只有1个HOST主桥,那么这4个CPU无法判断究竟谁才是HOST处理器。不过,究竟是哪个处理器作为HOST处理器并不重要,因为在一个处理器系统中,是HOST主桥管理PCI总线域,而不是HOST处理器。当一个处理器系统含有多个CPU时,如果每个CPU都可以访问HOST主桥,那么这些CPU都可以作为这个HOST主桥所管理的PCI总线树的HOST处理器。

本节内容较多,更多内容请看下回。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 全球FPGA市场的有趣格局

- ubuntu 20.04 使用 webrtc-streamer自动退出,报错GLIBC 问题解决方法

- 《GreenPlum系列》GreenPlum初级教程-03GreenPlum系统管理

- 初识java

- 高性能3D Web轻量引擎HOOPS SDK助力制造业信息共享与协同!

- 网页版音乐元数据编辑器Music Tag Web

- 智慧校园大数据平台功能模块

- 我把MySQL运行在Docker上,差点完了……

- 【Flink-Kafka-To-ClickHouse】使用 Flink 实现 Kafka 数据写入 ClickHouse

- 基于Java SSM框架实现学生综合考评作业成绩管理系统项目【项目源码+论文说明】计算机毕业设计