LTPI协议的理解——LTPI协议的定义和结构

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

LTPI协议的理解——LTPI协议的定义和结构

定义

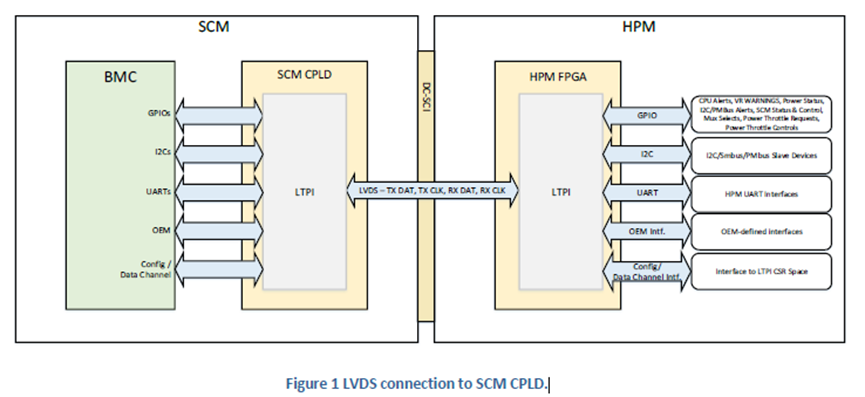

LTPI (LVDS Tunneling Protocol & Interface,LVDS 隧道协议和接口)是一种协议和接口,设计用于在 HPM 和 SCM 之间传输各种低速信号。它不仅支持 GPIO 的隧道传输,还支持 SMBus、I2C、UART 等低速串行接口的隧道传输。它还可以通过额外的专有 OEM 接口进行扩展,并为 HPM CPLD 和 SCM CPLD 之间的原始数据隧道提供支持。

DC-SCM 2.0 LTPI 结构

LTPI 接口可以通过两个 FPGA/CPLD 器件来实现,以便与典型的 BMC 器件进行配置:

- HPM FPGA – 提供本地 HPM 接口与 LTPI 的桥接

- SCM CPLD – 提供到本地 SCM 接口的 LTPI 桥接

DC-SCM LTPI 接口实现了通道的概念,其中每个通道都映射到 DC-SCM 和 HPM 上的特定类型的物理接口。 LTPI 接口定义了以下通道:

? GPIO 通道

? I2C/SMBus 通道

? UART 通道

? OEM 渠道

? 数据通道

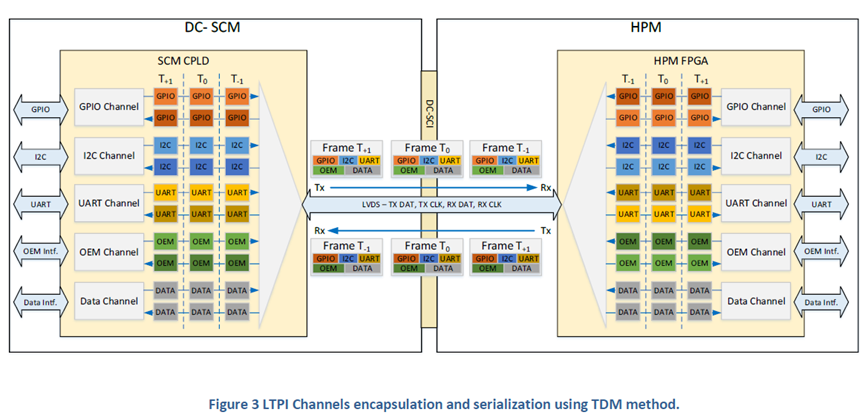

LTPI使用高速LVDS全双工链路的时分复用(TDM)在SCM和HPM之间发送和接收LTPI信道。如下图所示,在LVDS链路上的每个相等时隙中,都有一个LTPI帧正在传输。在通过LTPI接口发送的每个帧中,分配给特定信道的比特数与专用于每个信道的LTPI带宽成正比。为了最大限度地减少对LTPI信道的延迟影响,假设LTPI帧是没有任何帧间间隙的。在无法避免帧间间隙的实现中,建议帧间间隙时间保持恒定,以最小化延迟变化并简化实现。

GPIO通道

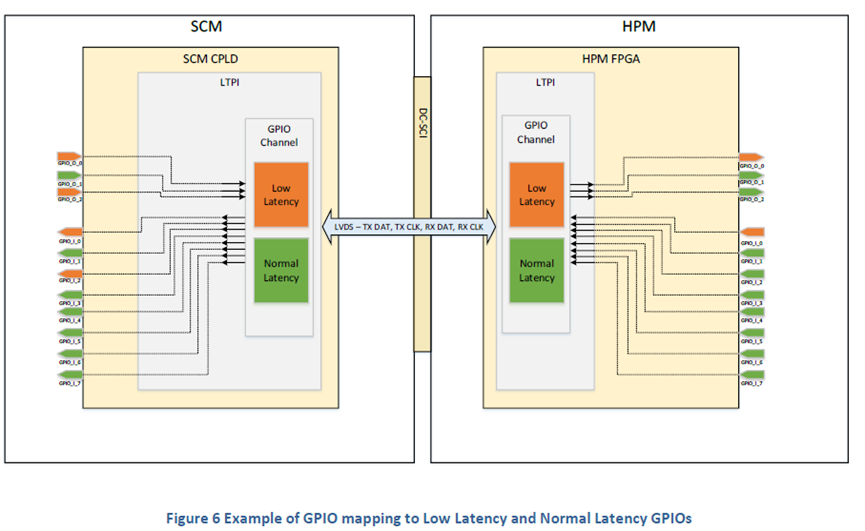

GPIO通道用于通过LTPI接口传输低速HPM和SCM GPIO。GPIO通道定义低延迟和正常延迟GPIO。GPIO映射到低延迟GPIO部分还是映射到正常延迟GPIO部分看具体使用情况。LTPI-GPIO通道中物理GPIO到低延迟和正常延迟GPIO的映射示例如下图。注:GPIO是一个通用术语,它可以是软件(HPM上的CPU或SCM上的BMC)控制的输入/输出,也可以是行为类似于物理直接连接的纯硬件数字信号。

低延迟GPIO: 为每个低延迟GPIO分配的最大LTPI带宽。每个GPIO被映射到LTPI帧中的特定比特,并随着每个LTPI帧而更新。

正常延迟GPIO:最大LTPI带宽分配在LTPI帧中预定义数量的比特上。所有位在正常延迟GPIO之间共享。根据LTPI帧中分配的NL GPIO的数量和NL GPIO位的数量,更新所有NL GPIO需要多个LTPI帧。

GPIO的数量:受分配给LL GPIO的LTPI帧比特数的限制,受NL GPIO可接受的延迟限制。NL GPIO越多,延迟越高。

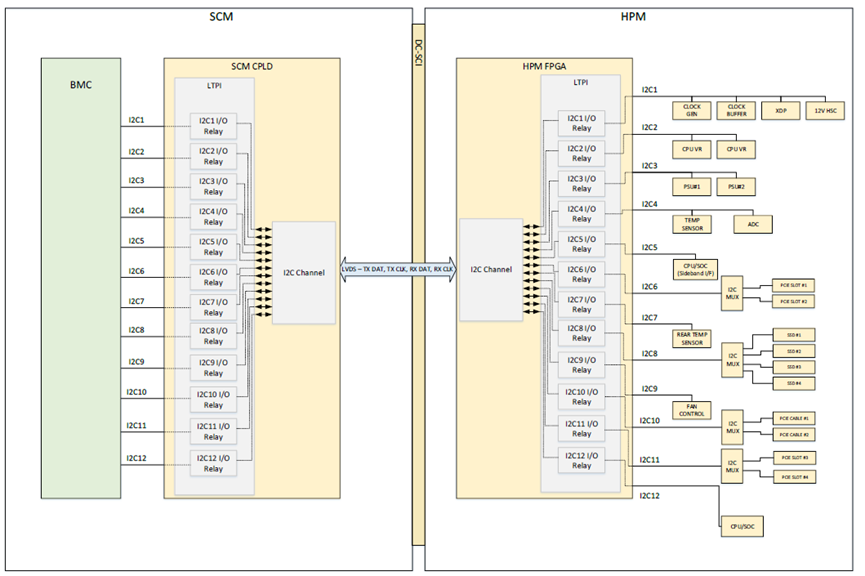

I2C/SMBus通道

I2C/SMBus通道用于通过LTPI接口对I2C/SMBus总线进行隧道传输,用于SCM或HPM上只有一个控制器的链路。DC-SCM LTPI I2C/SMBus隧道解决的主要用例如图所示。

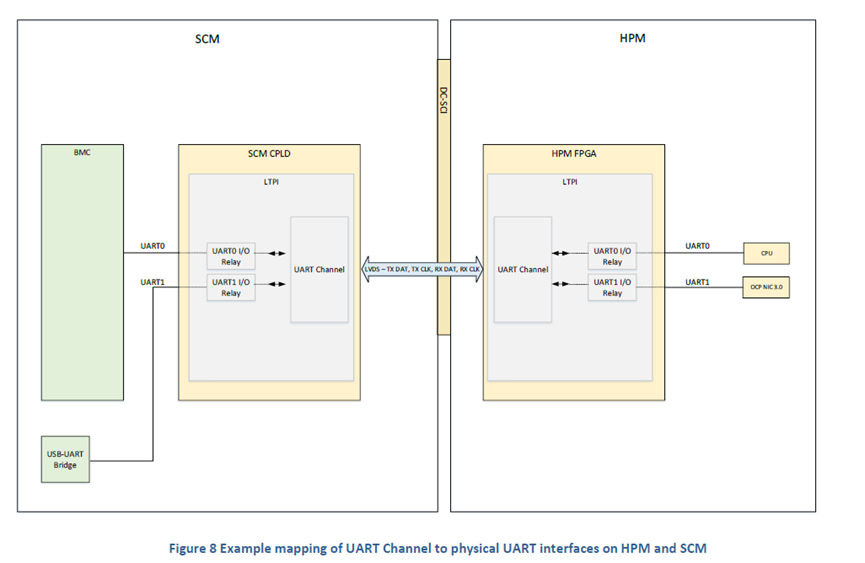

Uart通道

UART通道用于通过LTPI在SCM和HPM之间传输物理UART接口。UART通道支持使用流量控制信号对多个全双工UART接口进行隧道传输。UART接口通过LTPI进行隧道传输,并重建为类似于GPIO和I2C通道的物理UART接口。如下图中UART的使用示例所示,通过隧道传输的HPM UART接口可以直接连接到BMC或其他设备。

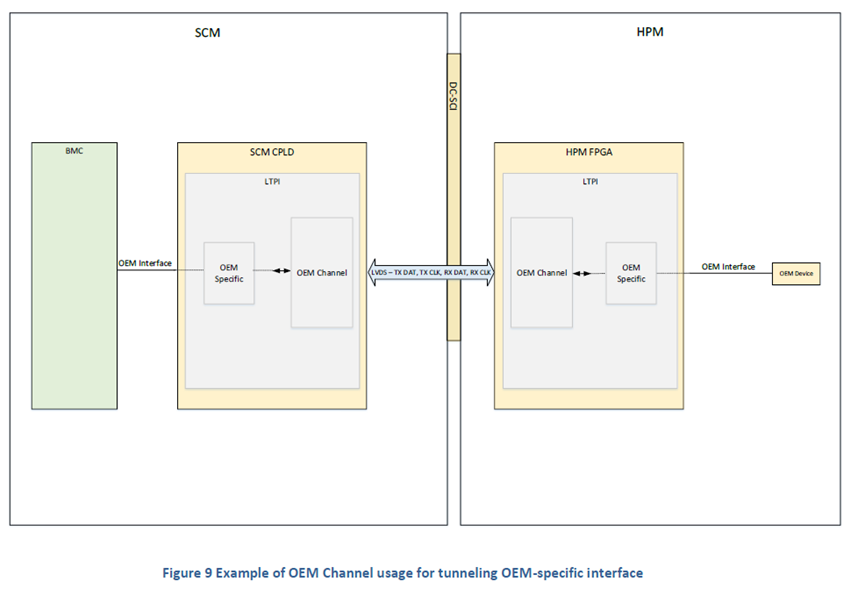

OEM通道

OEM通道允许通过LTPI进行OEM特定接口隧道传输。OEM可以采用与其他通道相同的方法来实现专有接口隧道。定义OEM特定的接口细节和通道设计超出了规范的范围。OEM通道仅被定义为使用DC-SCM LTPI实现OEM扩展和专有接口的占位符。

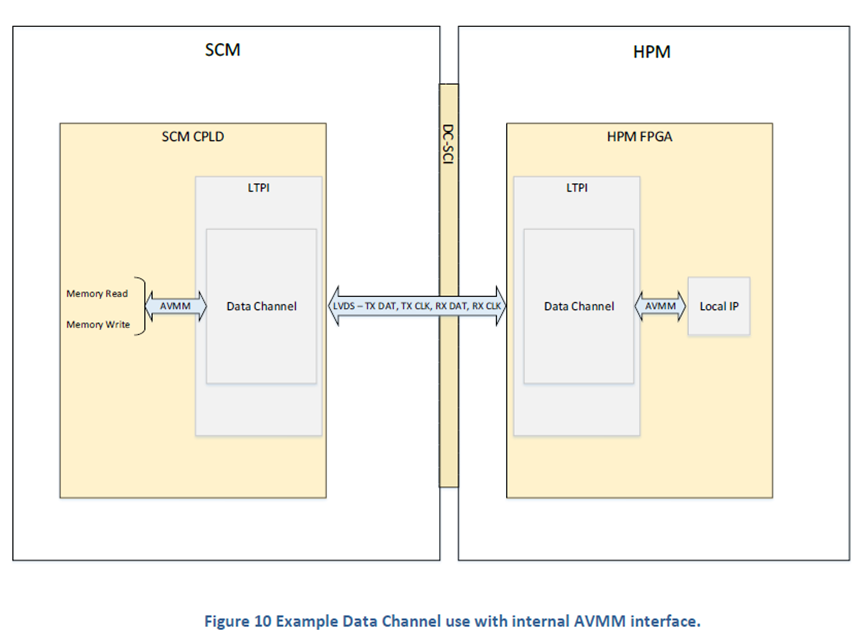

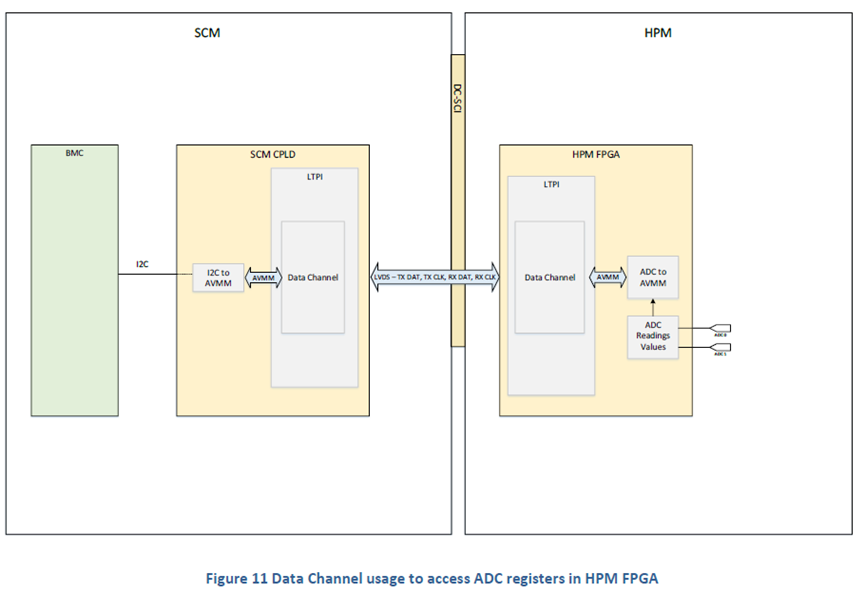

数据通道

数据通道允许通过LTPI在SCM CPLD和HPM FPGA之间进行数据隧道传输。这增加了实现LTPI扩展以满足特定设计需求的灵活性和可能性。数据通道遵循内存映射接口的概念,例如Avalon内存映射(AVMM)或Wishbone总线。如下图中的示例所示,数据通道实现了一个内部AVMM总线,该总线允许在SCM CPLD和HPM FPGA之间映射内存空间,并使用遵循AVMM总线支持的标准化IP块。数据通道允许从位于LTPI接口后面的IP进行随机访问数据读取和写入。只有当有写入或读取数据的请求时,数据通道访问才会按需进行。

数据通道使用的一个示例如下图所示,其中数据通道用于访问内置在HPM FPGA中的ADC的模数转换器读数。BMC对数据通道的访问可以由BMC SOC支持并连接到SCM CPLD的任何标准接口提供,例如SPI、I2C或类似接口。在下面的示例中,BMC使用I2C接口来触发来自ADC的读取。I2C AVMM桥接器解释BMC读取并将其转换为AVMM数据读取,这些读取通过LTPI接口传递到HPM FPGA。数据通道的定义是通用的,它不与任何特定的数据总线接口绑定。

总结

可以看到,LTPI协议解决的是将很多低速通道汇聚为一对LVDS线,使得设备之间的连线非常简单,且很少的连线更便于传输。至于具体是怎么将很多低速接口进行传输的,后面讲到的帧定义会提到。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 第11章 GUI Page489~494 步骤三十 保存画板文件02 实现存盘函数SaveFile

- web前端之复制图片到div中、使用contenteditable属性把元素变为可编辑状态、FileReader

- React实现字符串首字母大写、翻转字符串、获取用户选定的文本

- 图像的颜色及Halcon颜色空间转换transfrom_rgb/trans_to_rgb/create_color_trans lut

- DevEco Studio 项目启动工程和Device Manage

- 轻量封装WebGPU渲染系统示例<53>- 多盏灯灯光照在地面的效果

- 最佳利用Mock提升测试效率的7个技巧!

- 用通俗易懂的方式讲解:使用 LangChain 和 LlamaIndex 从零构建PDF聊天机器人

- linux系统ping命令小技巧

- 多维护健康:新生儿补充多维注意事项