vivado 创建合成约束

创建合成约束

Vivado Synthesis将您设计的RTL描述转换为技术映射网表。这个过程分几个步骤进行,包括一些定时驱动优化。AMD FPGA包括许多可以以多种不同方式使用的逻辑功能。你的需要约束来引导合成引擎找到满足所有设计的解决方案实现结束时的需求。Vivado IDE合成有四类约束:

?RTL属性

?时间限制

?物理和配置限制

?详细的设计约束

RTL属性

RTL属性必须写入RTL文件中。他们通常选择某些的映射样式部分逻辑,以及保留某些寄存器和网络,或控制设计最终网表中的层次结构。

有关USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION的更多信息,请参阅合成和实施约束文件。

DONT_TOUCH属性示例:

set_property DONT_TOUCH true[get_cells fsm_reg]

时间限制

时序约束必须通过一个或多个XDC文件传递给合成引擎。只有以下与设置分析相关的约束对合成结果有任何实际影响

物理和配置约束

合成算法忽略了物理和配置约束。详细的设计约束

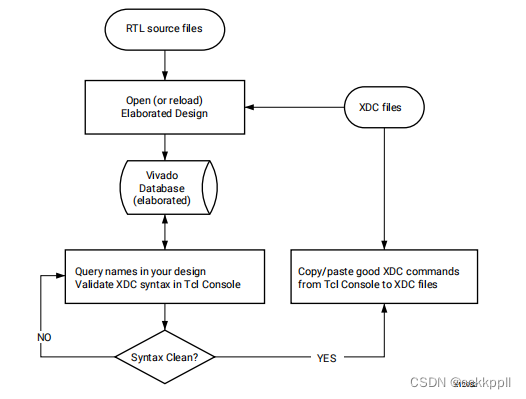

在流程的这一点上,网络延迟建模仍然不是很准确。主要目标是在启动之前,获得一个符合定时或少量失败的合成网表实施在许多情况下,您将不得不经历几个XDC和RTL修改迭代之后才能达到此状态。基于RTL的XDC创建迭代如下图所示。它基于利用精心设计来查找设计中要查找的对象名称

约束以进行合成。在将XDC命令保存到中之前,必须使用Tcl控制台验证它们的语法XDC文件。通过精心设计,您可以创建约束。

编写合成约束时可以安全使用的设计对象有:

?顶级端口

?手动实例化的基元(单元和引脚)一些RTL名称在创建详细设计的过程中被修改或丢失。以下是

最常见的情况:

?单比特寄存器名称

?多位寄存器名称

?吸收寄存器和网络

?分层名称

单比特寄存器名称

默认情况下,寄存器名称基于RTL中的信号名称加上_reg后缀。例如,对于VHDL和Verilog中定义如下的信号,生成的实例名称在阐述过程中是wbDataForInputReg_reg:

下图显示了寄存器及其引脚的示意图。可以定义寄存器实例或其引脚上的约束。

多位寄存器名称

默认情况下,寄存器名称基于RTL中的信号名称加上_reg后缀。你只能在XDC命令中查询和约束多位寄存器的各个位。例如,对于VHDL和Verilog中定义如下的信号,生成的实例名称在细化过程中有loadState_reg[0]、loadState_reg[1]和loadState_reg[2]:VHDL:信号加载状态:std_logic_vvector(2下降到0);Verilog:reg[2:0]负载状态;下图显示了寄存器的示意图。多位寄存器显示为单个位寄存器的矢量。矢量尽可能以紧凑的方式表示原理图。每个单独的位也可以单独显示

通过使用以下模式,只能单独或成组约束每个寄存器:

?仅寄存器位0

?所有寄存器位

loadState_reg[*]

因为上面的名称也对应于合成后网表中的名称基于它们的约束很可能也适用于实现。

吸收寄存器和网

RTL源中的一些寄存器或网络可能会在详细设计中消失(或合成设计)。例如,内存块、DSP或移位寄存器推理需要将多个设计对象吸收到一个资源中。而不是使用这些对象来定义约束,请尝试查找可以使用的其他连接寄存器或网络。

分层名称

除非你计划强制Vivado合成以保持设计的完整层次,否则有些或者可以在合成期间使层次结构的所有级别变平。有关更多信息,请参阅-在《Vivado Design Suite用户指南:合成》中的此链接处显示flatten_hierarchy信息(UG901)。

例如,考虑位于设计的子级别中的以下寄存器。详细说明设计示例:

inst_A/inst_B/control_reg

在合成过程中(假设没有对此寄存器进行特殊优化),您可以得到平面名称或层次名称,具体取决于工具选项或设计结构。平面网表中的实例名称:

inst_A/inst_B/control_reg(F)

层次网表中的实例名称:

inst_A/inst_B/control_reg(H)

没有明显的区别,因为/字符也用于标记扁平的层次结构水平。当查询内存中的对象时,您会注意到这一差异。以下内容命令将返回F而不是H的网表对象:

%get_cells-分层*inst_B/control_reg

%get_cells-inst_A*control_reg

为了避免与层次名称相关的问题,AMD建议您执行以下内容:

?使用get_*命令而不使用-histrared选项。

?用正斜杠(/)字符明确标记层次结构的所有级别,如中所示阐述了设计观点。

不带-histrared选项的示例:

?此选项适用于平面网表和分层网表:

%get_cells inst_A/inst_B/*_reg

%get_cells inst_*/inst_B/control_reg

?另一种选择是:

%get_cells-hier-filter{NAME=~inst_A/inst_B/*_reg}

%get_cells-hier-filter{NAME=~inst_*/inst_B/control_reg}

由于转换,某些合成前约束可能不再适用通过对设计进行合成来执行。要解决这些问题,请执行以下操作:

1.找到适用于合成网表的新XDC语法。

2.将约束保存在新的XDC文件中,仅在实现过程中使用。

3.移动不能再应用于单独XDC文件的合成约束仅用于合成。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- android studio 按键点击事件的实现方法

- 融云获评「全球领航者·年度服务商」,自制《地图》引领行业风潮

- 程序包org.junit.jupiter.api不存在

- 扩展边界opencv

- Spring Cache 的使用

- 实战Vue.js与校园便利平台:前端开发的最佳实践与技巧

- Spring MVC 的核心组件

- 从源码到实践:深入了解鸿鹄电子招投标系统与电子招投标

- VS2022 WinForm自动缩放

- JAVA项目信创改造2024年