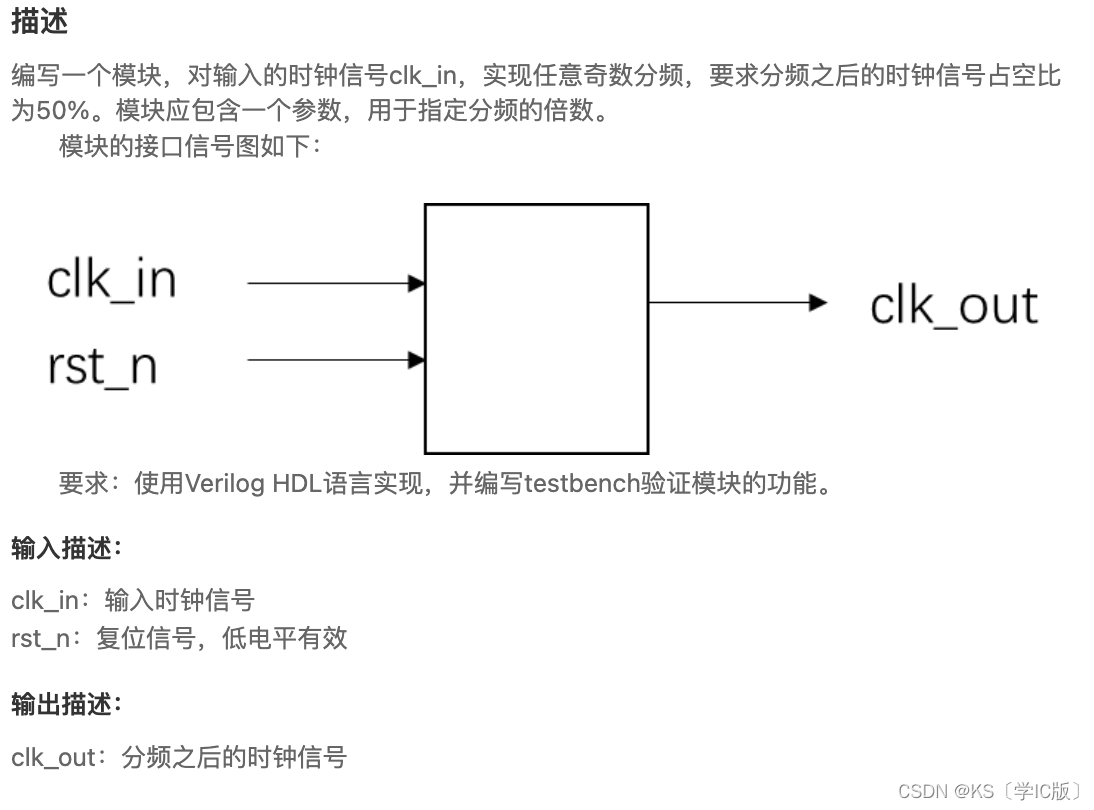

「Verilog学习笔记」任意奇数倍时钟分频

发布时间:2024年01月05日

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

`timescale 1ns/1ns

module clk_divider

#(parameter dividor = 5)

( input clk_in,

input rst_n,

output clk_out

);

parameter CNT_WIDTH = $clog2(dividor - 1) ;

reg flag1, flag2 ;

reg [CNT_WIDTH:0] cnt ;

always @ (posedge clk_in or negedge rst_n)

if (!rst_n) cnt <= 0 ;

else cnt <= cnt == dividor - 1 ? 0 : cnt + 1 ;

always @ (posedge clk_in or negedge rst_n)

if (!rst_n) flag1 <= 0 ;

else if (cnt == (dividor - 1) >> 1) flag1 <= ~flag1 ;

else if (cnt == dividor - 1) flag1 <= ~flag1 ;

else flag1 <= flag1 ;

always @ (negedge clk_in or negedge rst_n)

if (!rst_n) flag2 <= 0 ;

else if (cnt == (dividor - 1) >> 1) flag2 <= ~flag2 ;

else if (cnt == dividor - 1) flag2 <= ~flag2 ;

else flag2 <= flag2 ;

assign clk_out = flag1 || flag2 ;

endmodule

文章来源:https://blog.csdn.net/m0_54689021/article/details/135406432

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 开源云真机平台-Sonic平台-python自定义脚本-config.yaml方式实现全局配置参数的读写操作

- SQL慢语句执行的很慢,如何分析优化呢,(如何优化的呢?)

- RHCE: 主从DNS服务器配置 (实现正反向解析)

- 《新课程教学》(电子版)是正规期刊吗?能评职称吗?

- 【Java】实验四 多线程与并发

- PyQt6 QMessageBox对话框控件

- [蓝桥杯学习] 倍增LCA

- 奇怪的电梯------[解析]广度优先搜索

- Proxyman:现代本地Web调试代理工具

- 【Java 进阶篇】Jedis 操作 Hash:Redis中的散列类型