【SV的过程语句和子程序_2023.12.25】

发布时间:2023年12月27日

SV的过程语句

硬件世界:module,interface

软件世界:program,class(不会综合成硬件电路)

always描述硬件的行为,只可以在module或interface中使用

initial按照时间顺序测试,即软件方式来完成,在module或interface或program中使用

SV拓展:

always_ff:寄存器,必须是时序逻辑电路,否则会报错

always_comb:组合逻辑

always_latch:锁存器

软件的过程语句

function

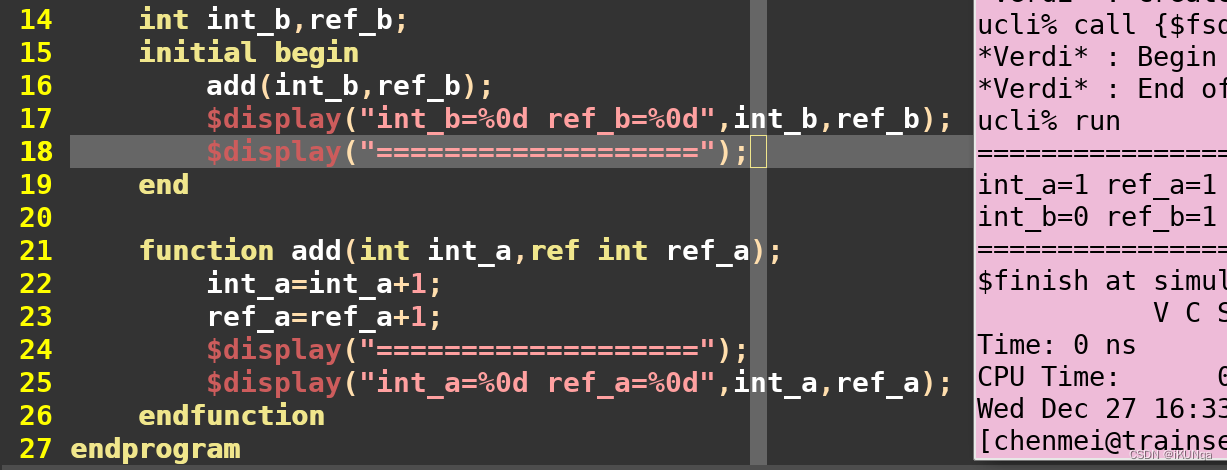

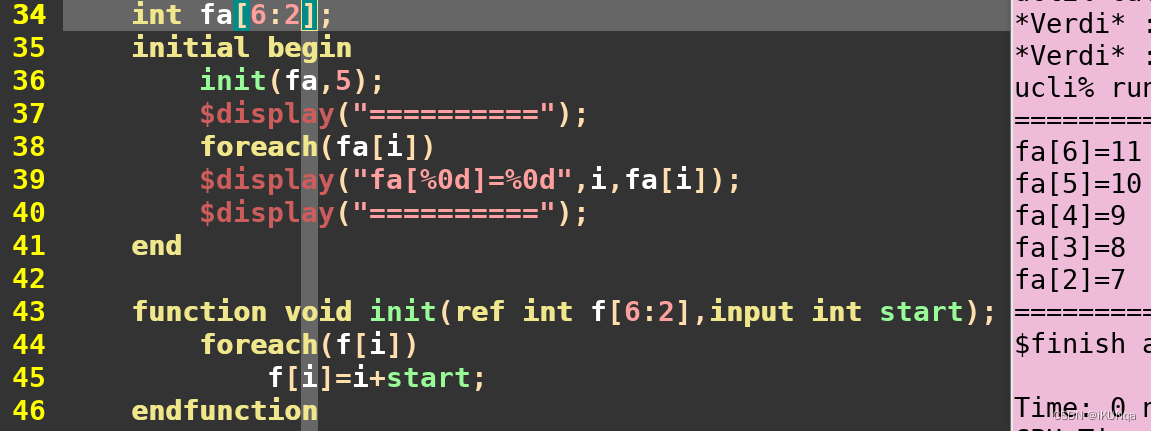

可input、output(最好不要使用)、inout(最好不要使用)或引用参数ref(相当于指针,直接操作实参,如下图)

可返回数值或不返回void

一旦return后边语句不会再执行

function int double(input int a);//int:若无,默认logic的input;在function后加void则不返回数值

只有数据类型可在形参列表中被声明为ref类型,线网类型不可以

使用ref时,为了保护数据对象只被读取不被写入,可通过const去限定re声明f的参数

声明参数时,可以给入默认数值,调用时可省略该参数的传递

不能使用耗时语句(@event、wait event、#delay)

task

无法通过return返回结果,只能通过output、inout或ref的参数来返回

return:终止程序的作用

可使用耗时语句

function和task均可调用function,task只调用task

wait和@的区别

@(变化)

wait(有效电平)/ wait(clk.triggered())//等待电平的触发,会报错,因为clk不是event类型的变量,不能用triggered函数

SV的子程序

参数传递

task many(input int a=1,b=2,c=3,d=4);

many(.c(5));//1 2 5 4

子程序的返回

Verilog只能返回一个简单值,SV可返回一个数组

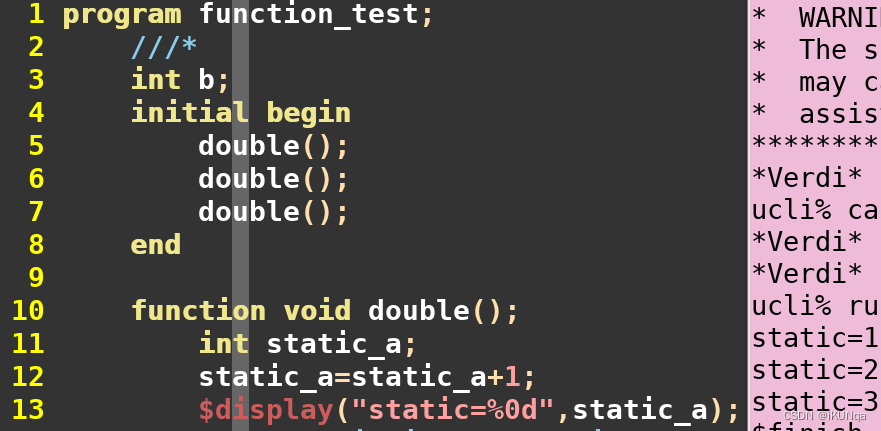

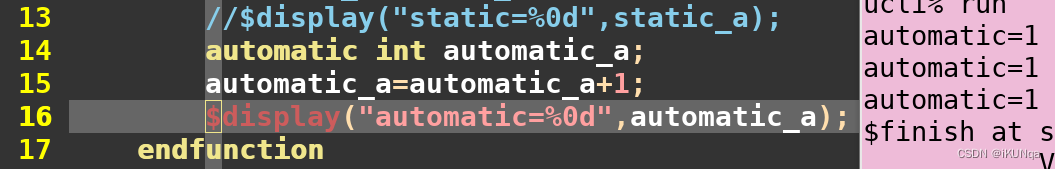

动态/静态子程序

static(不要显式出现):内存空间固定

automatic:调用时分配内存空间

在关键字task/function之后使用,不要混用

module,program默认静态,class默认动态,interface接口不定义方法

时间单位和精度/时间变量和舍入

$timeformat(-9,3,"ns",8);//3.141ns

//-9为ns,数据精度小数点后三位,时间值后的字符串,时间字符串字段的最小宽度

Time类型的变量不能保存小数时延,64位的整数,四舍五入

Real类型保存精确数值,只在用作时延量的时候才被舍入

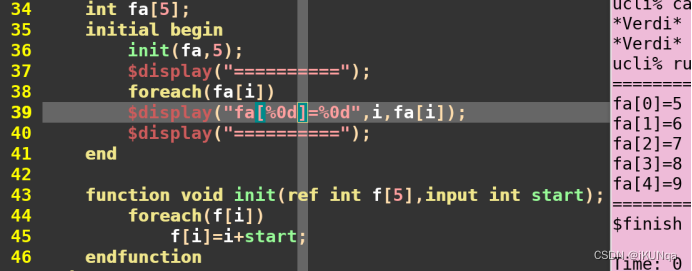

foreach和function的例子

foreach循环会遍历原始声明中的数组范围。

数组f[5]:f[0:4]foreach(f[i]) 等同于 for(int i=0;i<=4;i++)。

数组f[6:2]:foreach(f[i]) 等同于 for(int I=6;i>=2;i–)。

文章来源:https://blog.csdn.net/xiaotong121/article/details/135225410

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章