小梅哥Xilinx FPGA学习笔记19——IP 核使用之 ROM

发布时间:2023年12月29日

目录

一:章节导读

?????? ROM 是只读存储器(

Read-Only Memory

)的简称,是一种只能读出事先所存数据的固态半导体存储器。

其特性是一旦储存资料就无法再将之改变或删除,且资料不会因为电源关闭而消失。而事

实上在

FPGA

中通过

IP

核生成的

ROM

或

RAM

,调用的都是

FPGA

内部的

RAM

资源,掉电内容都会丢失(这也很容易解释,

FPGA

芯片内部本来

就没有掉电非易失存储器单元)。用

IP

核生成的

ROM

模块只是提前添加了数据文件

(

.coe

格式),在

FPGA

运行时通过数据文件给

ROM

模块初始化,才使得

ROM

模块像个

“真正”的掉电非易失存储器;也正是这个原因,

ROM

模块的内容必须提前在数据文件中

写死,无法在电路中修改。?

?????? Xilinx 推出的

ROM IP

核分为两种类型:单端口

ROM

(

Single-Port Rom

)和双端口

ROM

(

Dual-Port ROM

)。对于单端口

ROM

提供一个读地址端口和一个读数据端口,只能

进行读操作;双端口

ROM

与单端口

ROM

类似,区别是其提供两个读地址端口和两个读数

据端口,基本上可以看做两个单口

RAM

拼接而成。下面是

ROM

不同配置模式存储器的接

口信号图,如下图

所示。

?????? 在 FPGA 的开发过程中,片上存储器的灵活运用是一项非常重要的开发能力。FPGA 最常用的片上存储器控制器包括 ROM,RAM 和 FIFO。本章将实现一组固定的数据(三角波形表)存储在 FPGA 中使用 IP 核构建的 ROM 中,开发板上电后,系统开始从 ROM 中读出数据,并将数据直接通过并

口输出。

二:ROM IP 核配置

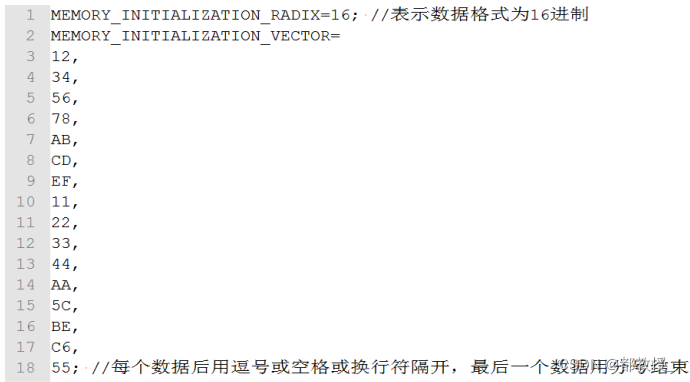

2.1 创建 ROM 初始化文件

?????? ROM

作为只读存储器,在进行

IP

核设置时需要指定初始化文件,即写入存储器中的

数据,数据要以规定的格式才能正确写入

ROM

,这种格式就是

coe

文件。

coe

是

Vivado

规

定的一种文件格式,文件格式示意图,具体见下图

。

?????? 如上图

所示,该文件的格式较为简单,第一行是定义数据的格式,其中

16

表示

数据格式为

16

进制,也可将数据格式定义为二进制和八进制,只需将

16

改为

2

或

8

即

可。其中第

3

到第

18

行是

16*8bit

大小

ROM

的初始化数据。

2.3 ROM IP 核配置步骤

?????? 首先点击1 箭头所指的

IP Catalog

,点击后会出现

IP Catalog

页面;我们在

IP

核的搜索

框中搜索

block

,根据筛序,我们双击箭头

3

所指的

RAM & ROM

核“

Block Memory

Generator

”。双击之后会出现如下图

所示的配置界面。

1

框中我们输入

IP

核的命名,后面实例化

IP

核的时候都是使用的该名字,这里所取

的名字最好是和该

IP

核相关,因为本节我们主要讲解

ROM

,所以给该

IP 核取名为

rom_256x8

(

rom

是我们调用的

IP

核,

256

是调用的

IP

核容量,

8

是调用的

IP

核数据位

宽。这里这样命名是为了方便识别我们创建的

IP

核类型及资源量)。

2

框我们按默认选中“

Native

”

3

框中选择存储器类型,可供选择的类型有:

Single Port RAM

(单端口

RAM

)、

Simple Dual Port RAM

(简单双口

RAM

)、

True Dual Port RAM

(真双口

RAM

)、

Singl

Port ROM

(单端口

ROM

)、

Doul Port ROM

(双端口

ROM

)。这里我们选择“

Single Port

Rom

”单端口

ROM

。

4

框在

Algorithm

一栏中可选择用于实现内存的算法,其中

Minimum Area

为最小面积

算法;

Low Power

为低功耗算法;

Fixed Primitives

为固定单元算法。这里我们按默认选择

Minimum Area

即可。

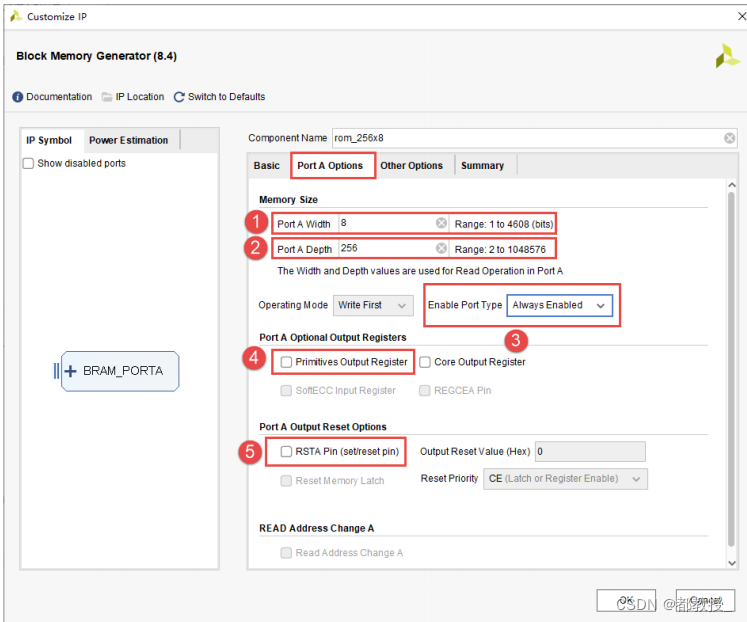

设置完之后切换到“

Potr A Options

”页面。

1

框中是设置存储数据的位宽,这里我们设置为

8

位;

2

框中是设置数据深度,所谓深度其实就是个数的选择,即设置的

ROM

可以存储多

少个

8

位宽的数据,这里我们设置为

256

;这样我们设置的

ROM

和最大能存储的数据即为

256 x 8bit

。(注意:设置的容量需大于我们需要写入的数据文件的数据量)

3

框中选择是否创建端口使能信号,这里我们不创建,选择“

Always Enabled

”始终

使能。

4

框是选择是否创建输出端口寄存器,若创建了择输出数据则会延后一个时钟输出这里我们不创建。

5

框是选择是否生产复位信号,这里我们不创建。

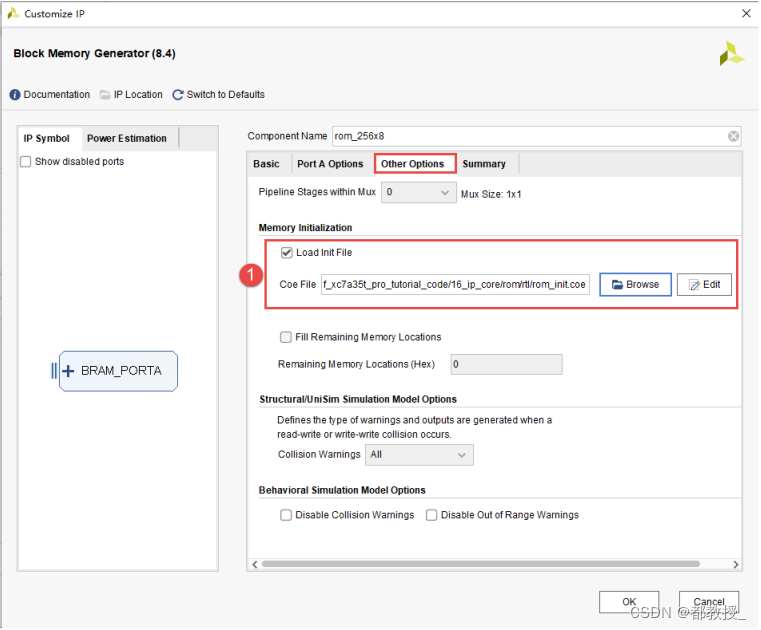

设置完之后切换到“

Other Options

”页面。

?????? 如下图所示,1

框中选项是加载数据文件,即我们前面讲到的

ROM

初始化文件,

由于

ROM

是只读存储器,所以我们必须添加

ROM

初始化文件才行。勾选上“

Load Init

File

”点击

Browse

进行添加

.coe

初始化文件,文件格式我们之前已经讲解,大家可根据自

己想存入的数据进行生成该文件。该页面其余按默认设置即可。

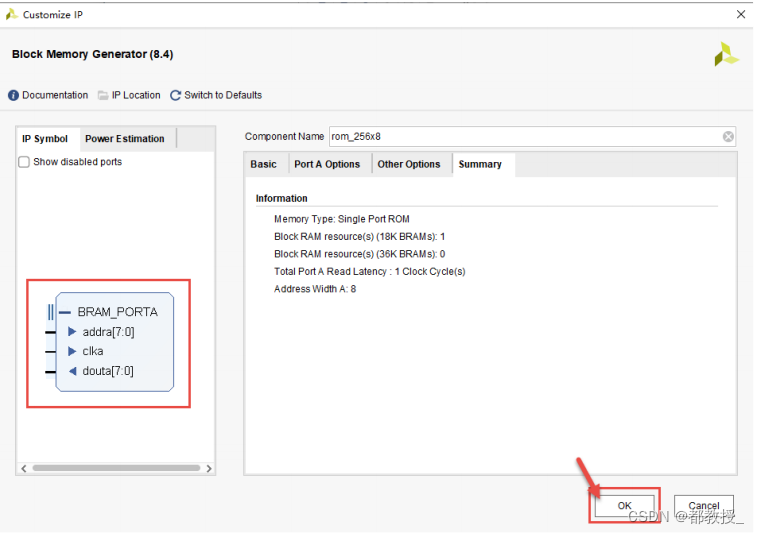

设置完之后切换到“

Summary

”页面。

?????? 如下图所示,在“

Summary

”页面,从“

IP Symbol

”窗口可以看到我们最终创建

的

ROM

核的端口信号。点击“

OK

”完成

ROM

的创建设置。

?????? 创建之后接下来跳出如下图所示界面,我们点击“

Generate

”。

?????? 接下来出现如下图所示界面,我们点击“

OK

”完成生成。

?????? 如下图所示,生成之后可以在工程中看到我们正常的

IP

核,双击

IP

核可进入配置

界面,对

IP

核的相关参数进行更改。

三: ROM核的仿真与调用

3.1 三角波的产生

使用小梅哥生成的三角波的.coe文件然后进行仿真验证,代码如下

`timescale 1ns / 1ps

module blk_mem_gen_0_tb();

`define CLK_PERIOD 20

reg clk;

reg [7:0]addr;

integer i = 0;

initial clk = 1;

always #(`CLK_PERIOD/2) clk = ~clk;

wire [7:0]dout;

blk_mem_gen_0 rom (

.clka(clk), // input wire clka

.addra(addr), // input wire [7 : 0] addra

.douta(dout) // output wire [7 : 0] douta

);

initial begin

addr = 0;

#21;

for(i=0;i<2560;i=i+1)begin

#`CLK_PERIOD;

addr = addr + 1'b1;

end

#(`CLK_PERIOD * 50);

$stop;

end

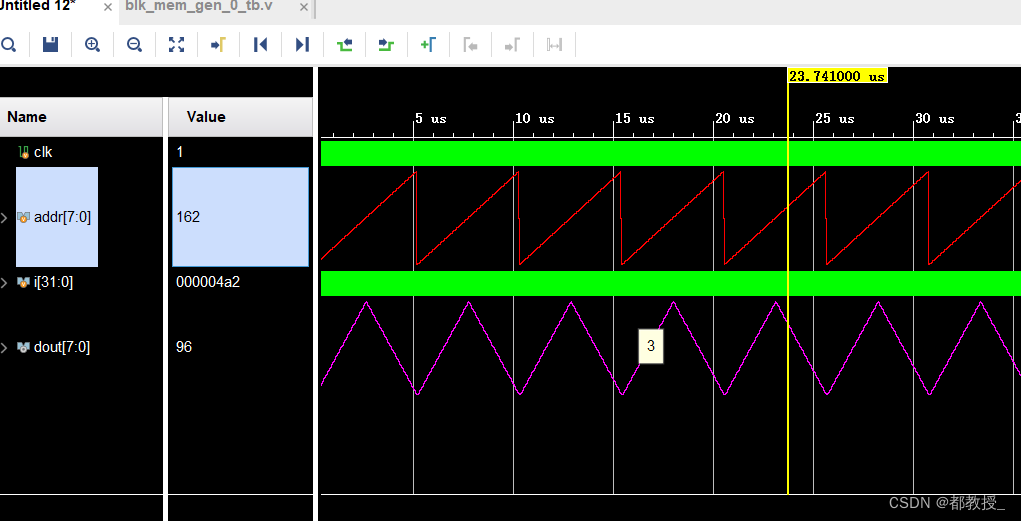

endmodule3.2 仿真验证结果

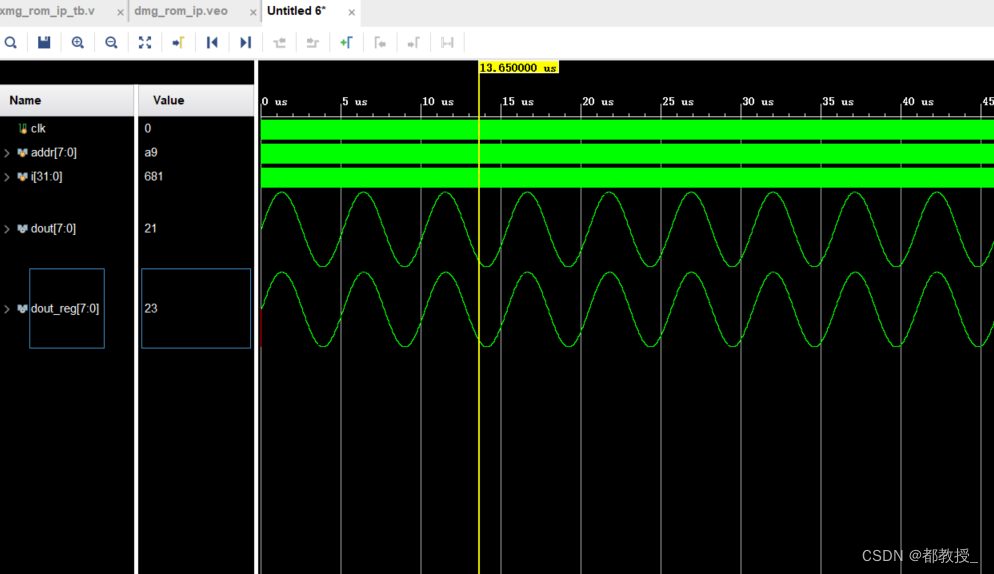

3.3 正弦波的产生

使用小梅哥的精灵软件生成的正弦波的.coe文件然后进行仿真验证。代码同

3.2节

3.4 仿真验证结果

?????

至此rom IP调用仿真完毕

。

文章来源:https://blog.csdn.net/m0_51430584/article/details/135274161

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【adb】--- win10 配置 adb环境 超详细 (持续更新中)

- ORB_SLAM3 LocalMapping中CreateNewMapPoints

- nginx配置

- JavaSE基础50题:25. 查找数组中指定元素(顺序查找)

- Android jks查看教程

- python 使用linux find命令引导用户定位和选择文档

- 柏曼、好视力、书客护眼台灯值得入手吗?热门台灯多方位测评对比

- 第五站:C++的内存解析

- openGauss学习笔记-203 openGauss 数据库运维-常见故障定位案例-修改索引时只调用索引名提示索引不存在

- 工程中的SOVD——从ECU到车辆