【FPGA & Modsim】序列检测

实验题目:??序列检测器设计 ?????????????????????????????????

实验目的:??掌握应用数字逻辑设计集成开发环境进行序列检测器设计的方法;掌握时序逻辑电路设计的过程。??????????????????????

实验内容:

1、设计一个序列检测器,用于检测输入数据中的特定序列“10010”。

2、实现一个电路,当检测到该序列时,输出为1,否则为0。

3、分析实验结果,验证电路的功能是否符合设计要求。

实验步骤:

1、在数字逻辑集成开发环境中新建一个序列检测器工程;

2、编写Verilog?HDL源程序;

3、编译和逻辑综合源程序;

4、编写Verilog?HDL仿真测试程序;

5、调用数字逻辑设计仿真环境对源程序进行仿真;

6、安装输入/输出端口建立约束文件;

7、下载到实验开发板,观察实践运行结果。

实验数据记录:

- 写出编写的Verilog?HDL源程序。

`timescale 1ns/1ps

module seq_tb();

reg [23:0] d;

reg clk;

reg rst_n;

wire y;

reg data;

seq_test uut (

????.clk(clk),

????.rst_n(rst_n),

????.data(data),

????.y(y)

);

initial begin

clk=0;

rst_n=0;

#10;

rst_n=1;

#20;d = 24'b0011_0100_1001_0110_1001_0101;

end

always #10 clk=~clk;

always@(negedge clk) begin

#10 ?data = d[23];

?d = {d[22 : 0], d[23]}; //Parallel to serial

end

endmodule

- 写出编写的Verilog?HDL仿真测试程序。

`timescale 1ns/1ps

module seq_test(clk,rst_n,data,y

???);

input clk;

input rst_n;

input data;//10010

output y;

reg [2:0] state;

reg [2:0] next_state;

wire y;

parameter s_idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,

????????????s4=3'b100,s5=3'b101,s6=3'b110,s7=3'b111;

always @(posedge clk or negedge rst_n)

begin

????????if (~rst_n)

????????????next_state <= 0;

????else

????????????next_state <= state;

end

always @(posedge clk or negedge rst_n)

begin

????????if (~rst_n)

????????????state <= s_idle;

????else begin

????case(state)

????????s_idle: begin if(data ==1)

????????????????????state <= s1;

????????????????else

????????????????????state <= s_idle; end

????????s1: ????begin ?if(data ==0)

????????????????????state <= s2;

????????????????else

????????????????????state <= s1;end

????????s2: ????begin ?if(data ==0)

????????????????????state <= s3;

????????????????else

????????????????????state <= s7; end

????????s3: ????begin ?if(data ==1)

????????????????????state <= s4;

????????????????else

????????????????????state <= s6; end

????????s4: ????begin ?if(data ==0)

????????????????????state <= s5;

????????????????else

????????????????????state <= s1; end

????????s5: ????begin ??if(data == 1)

?????????????????????state <= s1;

else

?????????????????????state <= s3;end

s6: begin ?if(data == 1)

????????????????????????????state <= s7;

???????????????????????????????else

????????????????????????????state <= s6;end

s7: begin ?if(data == 1)

???????????????????????????????state <= s1;

?????????????????else

?????????????????????????????state <= s2;end

default: state <= s_idle;

????endcase

??end

end

assign y = (state == s4 && data == 0)?1'd1:1'd0;

endmodule

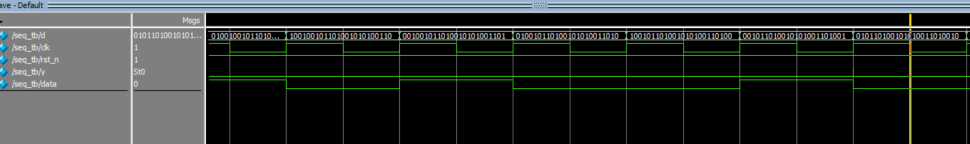

3、画出仿真环境中测试波形图。

问题讨论:

论述时序逻辑电路中有限状态机设计与实现方法。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 由浅入深走进Python异步编程【协程与yield】(含代码实例讲解 || 迭代器、生成器、协程、yield from)

- OpenCV-Python(25):Hough直线变换

- 【JAVA】Java 中什么叫单例设计模式?请用 Java 写出线程安全的单例模式

- 2022第十二届PostgreSQL中国技术大会-核心PPT资料下载

- LeetCode75| 哈希表/哈希集合

- Python代码注释详解(0基础入门

- 数据结构——顺序二叉树——堆

- 视频汇聚融合平台解决方案常见的接入方式及场景应用

- xtu oj 1169 最大子段和

- 十个查杀引擎免杀的PHP Webshell