数字IC实现途径

一、概述

二、全定制?

? ? ? ? 全定制的方式以人工设计为主,计算机软件作为辅助。其优点在于可以做到底层的最优化,但是设计成本高、自动化程度低。通常适用于:模拟电路(结构复杂而无规则)、可复用模块(标准单元、库单元、具有重复性结构之单元,如ROM、RAM等)、对性能要求极高的单元(加速器、乘法器、高速物理接口等)、产量极大的标准电路(存储器、通用逻辑电路等,成本~投片成本)、不计开发成本与时间的设计(如超级计算机、巨型计算机反向设计的芯片)。不适用于:大规模数字IC、规模大、批量不大的IC、要求设计周期短、设计成本低的电路。

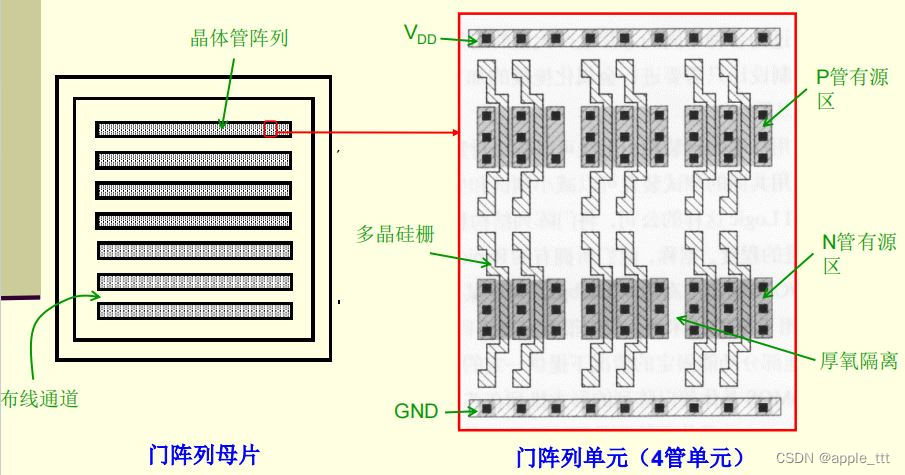

三、门阵列/门海

?????????对于多层布线的IC,可取消与晶体管同层的布线通道,称为门海(Sea of Gate)

????????相比于全定制而言,使用门阵列/门海有以下的优劣:

优势:

- 设计周期短:约为全定制的50%,因为只需设计连线,无需设计晶体管

- 投片成本低:母片通用,可大批量生产,只需追加与互连有关的掩模(金属化、接触孔、通孔等),成本降至全定制的1/4~1/8

- 易于实现设计自动化:结构规则,对单元库和EDA工具要求较低

劣势:

- 芯片面积大:母片门数>实际需要门数,布线通道面积>实际需要布线面积,单元中有冗余管(如6管单元做2输入与非门,就有2管冗余),单元晶体管面积固定(通常取所需最大面积)。总体面积利用率为60~80%

- 管脚数选择受限制:不适于内部单元少pad多以及内部单元多Pad少之电路

- 底层优化程度低:所有门都用同种尺寸(最大面积)的晶体管构成,尺寸无从优化,延迟、负载能力等无法达到最佳

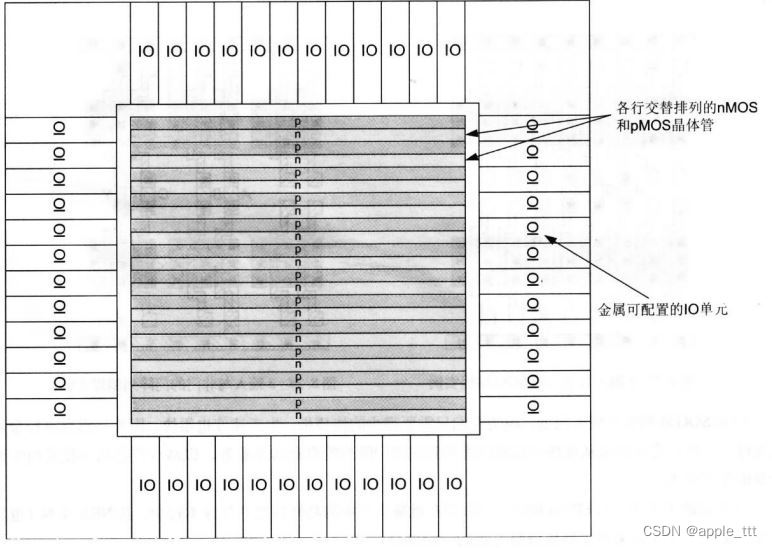

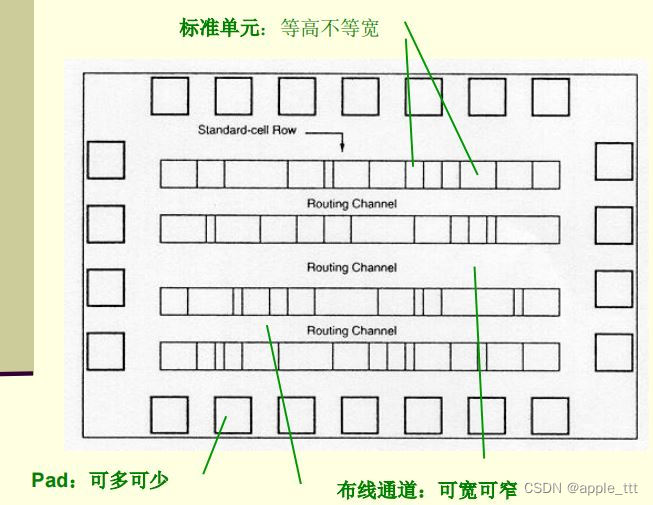

四、基于标准单元/宏单元?

4.1 标准单元

????????我们以一个无布线通道的标准单元为例

? ? ? ? 使用标准单元具有如下的特点:

优点:

- 面积利用率高于门阵列(可>90%),单元类型、数目、布线通道、Pad数按需选用,设计合理可基本无冗余

- 标准单元内部采用全定制设计,底层性能优化程度高

- 总体性能优化程度与经济性介于全定制和门阵列之间

缺点:

- 相对于门阵列而言,需全套掩模设计,故投片成本较高,生产周期较长

- 依赖于单元库,不如全定制灵活,单元类型数目有限,建库工作量大

- 依赖于EDA工具,能实现逻辑综合,但比门阵列相对难度大

- 对寄生参数(互连寄生参数、负载系数、串扰等)的估计不如门阵列准确4.

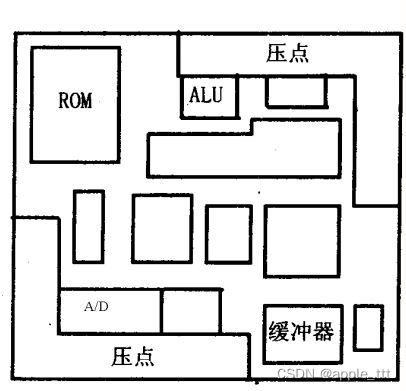

4.2 宏单元

? ? ? ? 相比于标准单元,宏单元最大的特点就是对单元的形状无限制。

?

?

优点

- 面积利用率较标准单元法高(~25%)

- 性能优化程度高

缺点

- 专用性强,通用性差

- 对单元库、EDA综合、布线工具要求更高

适用范围

- 嵌入式存储器(最常见)

- 模拟电路单元(运放、ADC/DAC、PLL、振荡器等)

- I/O单元

- SOC中的IP

- 标准单元难以甚至无法实现的其它电路单元

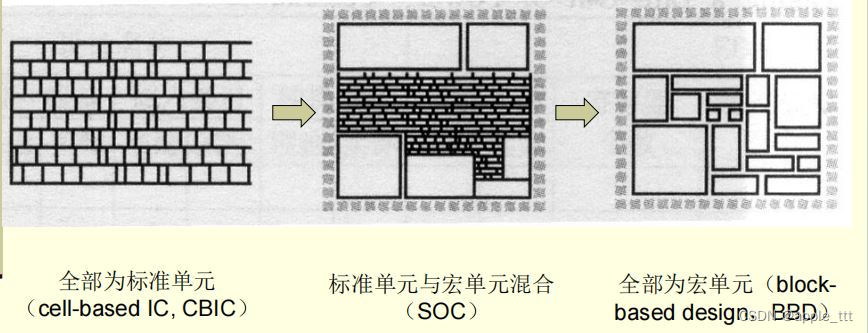

? ? ? ? ?在实际的使用过程中,我们可以单独使用标准单元或单独使用宏单元,也可以混用两者:

五、可编程器件

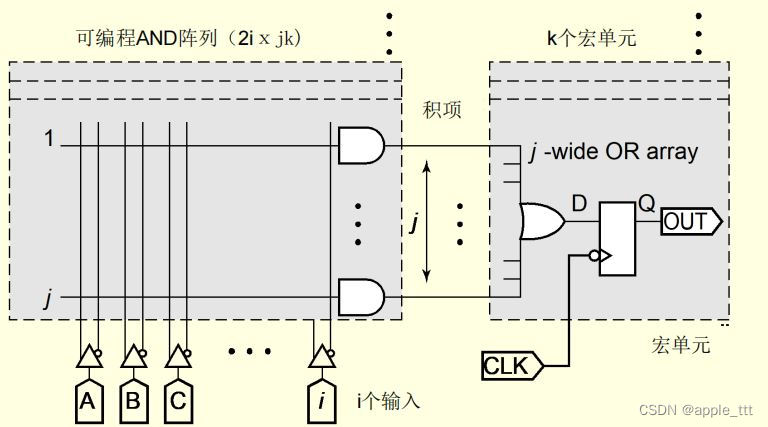

5.1 PLA(可编程逻辑阵列)

?

?

? ? ? ? 对于易失性编程,主要采用SRAM单元控制阵列中晶体管的通断,从而实现编程。其特点是采用标准CMOS工艺即可实现,但断电后无法保持(易失性),每次编程需读入数据,工作时需定时刷新,编程器件占用面积较大。

? ? ? ? 对于非易失性编程,通常基于浮栅晶体管实现的E2PROM或Flash编程。其特点是断电后仍然保持(非易失性),可多次编程(通常10万次),但浮栅晶体管需特殊工艺制造,擦存储单元需高电压(通常>10V)。

????????为了实现时序控制,必须在PLA阵列中加入时序控制元件(寄存器等)

优点:

- 结构非常规则,寄生参数乃至相关的面积、速度、功耗易于精确估计

- 实现能很好地映射为两层次逻辑的逻辑功能(如大扇入的有限状态机)时,效率很高

缺点:

- 用大阵列实现简单逻辑时会产生许多冗余项,造成面积的浪费,同时冗余节点的电容对电路的功耗、延迟有贡献

- 实现大扇出逻辑或多层逻辑(如加法和乘法运算)时,效率很低

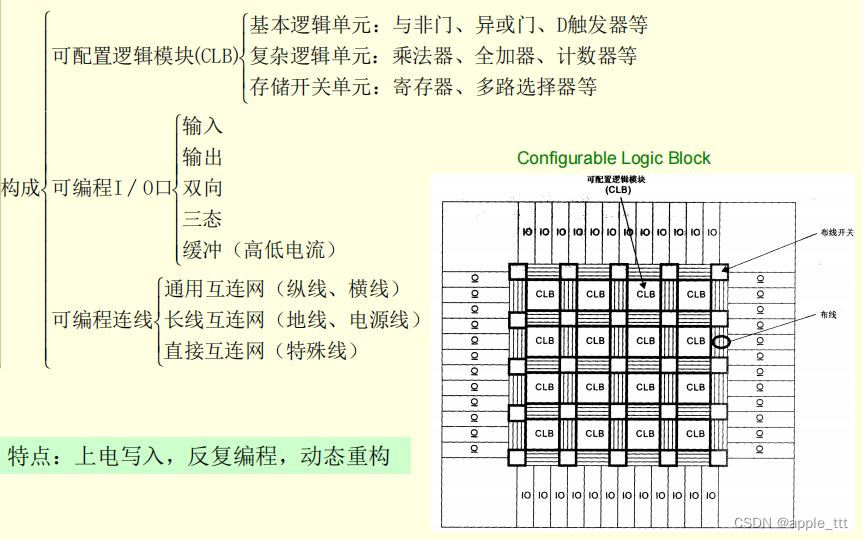

5.2 FPGA(现场可编程逻辑门阵列)

? ? ? ? 我们先来拆解下这个术语:现场可编程逻辑门阵列(FPGA,Field Programmable Gate Array)

- 现场:在芯片应用现场,通过外部施加控制信号来改变芯片内部的编程关系

- 可编程:用浮栅晶体管等方法控制阵列中晶体管的通断或连接

- 门阵列:用与门阵列类似的晶体管阵列来实现逻辑运算

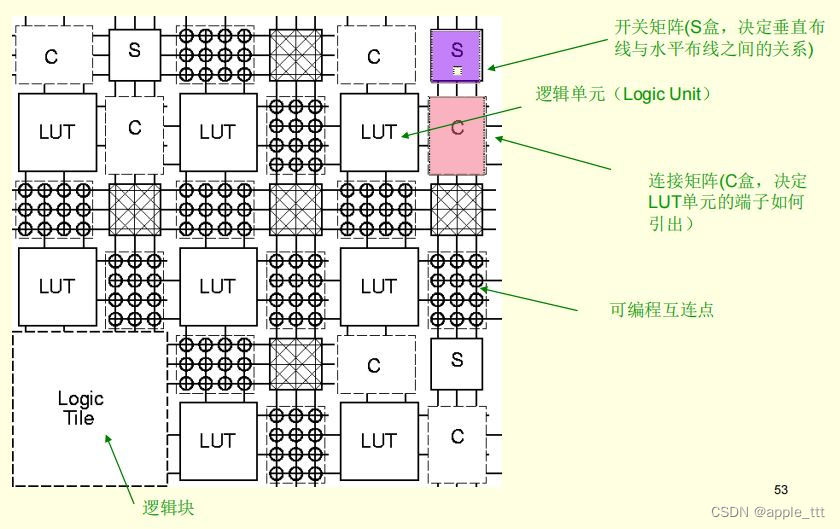

5.1.1 FPGA的结构特征

与传统PLA的区别

- 总体结构:基于单元,而非基于阵列

- 实现逻辑:基于存储器,而非“与”、“非”阵列

- 实现互连:基于可编程互连网格,而非阵列

? ? ? ? 目前主流的编程方式是采用SRAM型,其特点在于:易失,靠外加Flash保存编程信息。

5.1.2?FPGA的基本构成?

? ? ? ? 关于CLB的细节内容就不在本文展开了,感兴趣的读者可以阅读:

FPGA原理与结构(1)——可配置逻辑块CLB(Configurable Logic Block)![]() https://ztzhang.blog.csdn.net/article/details/132102065? ? ? ? ?这里补充说明一下CLB的外部接口

https://ztzhang.blog.csdn.net/article/details/132102065? ? ? ? ?这里补充说明一下CLB的外部接口

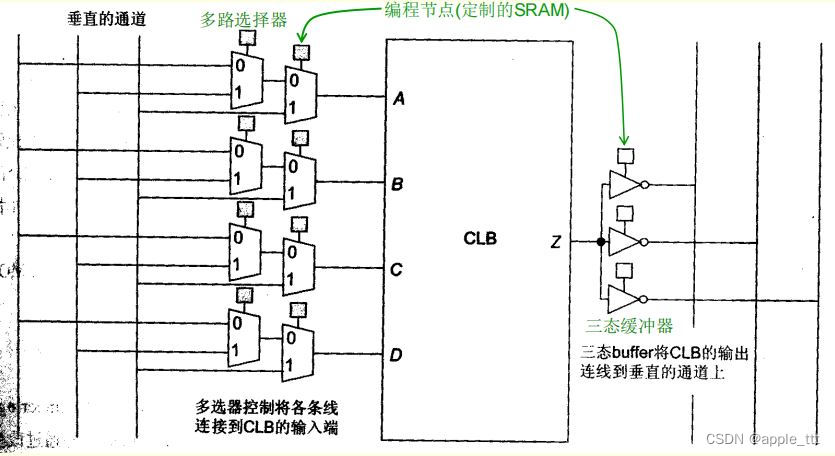

5.1.3 可编程互连线

? ? ? ? 首先介绍一下在PLA中使用广泛的阵列型可编程互联:

? ? ? ? 电路实现如下:

5.1.4 特点

优点

- 现场可编程,与芯片制造过程无关

- 研发费用低,设计周期短,设计验证容易,大大降低了开发风险,因为无需制造掩膜和工艺投片

- 一个芯片可实现多个功能,灵活性大

- 版图规则,适合自动化设计,且非微电子人员易于设计

缺点

- 单个芯片价格高,批量供货时成本高

- 性能难以充分优化,因为可编程消耗了资源,牺牲了面积、速度和功耗,在可比的条件下,性能与功耗比ASIC差10倍左右

适用

- 多品种、小批量、规模不大的集成电路,譬如航空航天、国防军工装备中使用的集成电路

- 要求快速上市,但对成本不计较的集成电路

- ASIC的设计验证

- 可维修集成电路

六、微处理器

微处理器的类型

- 中央处理器(CPU):兼具控制与处理

- 数字信号处理器(DSP) :擅长媒体(声音、图像、视频等)处理

- 微控制器(MCU):主要用于控制

- 专用处理器(ASSP):针对特定用途开发,如GPU、NPU等

- 嵌入式处理器:与其他IP一起构成SoC

微处理器用做数字控制与处理的特点

- 基于软件,具有最高的自由度,可自由定义、修改和扩充功能

- 具有相对最差的速度、功耗、面积和成本指标

七、SoC

7.1 IP

- 软核(softcore):用RTL级的HDL代码方式表征,用于定义模块的逻辑功能,与具体实现工艺无关,灵活性高,用户可修改,但也因此缺乏对时序、面积和功耗的预见性。

- 硬核(hardcore):以物理版图形式(GDS II)表征,针对特定工艺,具有固定的布局、尺寸和完全明确的时序参量,但灵活性差,用户不可修改。嵌入式处理器、嵌入式存储器和专用加速单元等多以硬核的方式呈现。

- 固核(firmcore):以门级网表形式表征,用于描述实现逻辑的每个门和寄存器,功能上可以面向多个工艺,性能上与工艺有关,比软核的可靠性高,比硬核的灵活性强。

7.2?嵌入式处理器

- 与Intel和AMD的通用处理器不同,嵌入式处理器要求在较小电路规模和较低功耗的条件下实现高性能,多采用简化指令集(RISC,Reduced Instruction Set Computer)而非复杂指令集(CISC)、多级(3-8)流水线结构、专用高速乘法器单元等,位数从4位到64位都有。

- 嵌入式CPU以ARM (Advanced RISC Machines)的使用最为广泛,继ARM7~11 的通用系列之后,2004年后发布的有面向消费应用的32位Cortex-M系列、面向虚拟内存操作系统的64位Cortex-A系列和面向实时系统及安全应用。

7.3 NoC

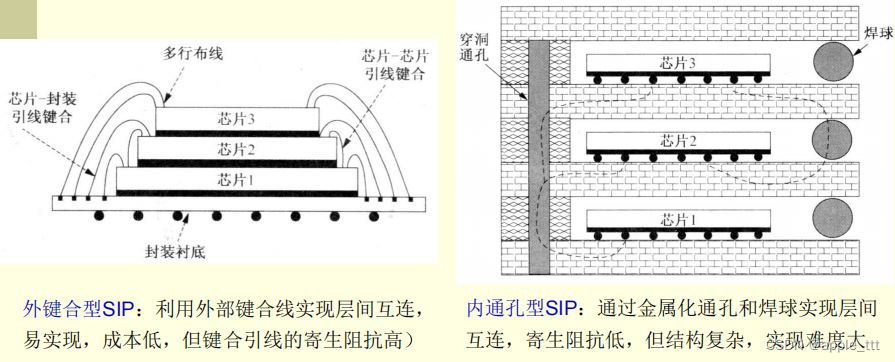

7.4 SIP

- 与SoC相比:可集成非硅CMOS基的元器件(高性能无源元件、MEMS、光元件、传感器、 生物元件等),实现异质集成(HI,Heterogeneous Integration),设计周期,研发成本 ,技术难度,但速度、功耗和集成密度不如SoC

- 与PCB相比:速度、功耗、集成密度明显改善

7.5?Chiplet

- 与SoC相比:裸芯粒可用不同工艺和材料制备,可涵盖CPU/GPU/NPU、存储器堆栈、RF收 发芯片、GaN/SiC宽带隙功率器件、微纳机电系统(MEMS/NEMS)等,可只购买裸芯粒而非IP,从而降低了研发成本

- ?与SIP相比:制作在硅基衬底而非PCB衬底上,采用硅通孔和铜通孔而非封装键合线互连,从 而提高了集成密度

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!