总线协议:GPIO模拟SMI(MDIO)协议:SMI协议介绍

0 工具准备

TN1305 Technical note

IEEE802.3-2018

STM32F4xx中文参考手册

1 SMI介绍

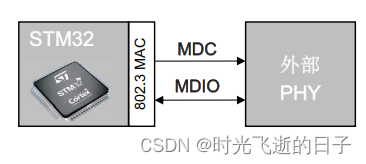

1.1 SMI总体框图

站管理接口SMI(Serial Management Interface),也可以称为MDIO接口(Management Data Input/Output Interface)。它允许应用程序通过时钟线(MDC)和数据线(MDIO)访问PHY寄存器,支持寻址最多32个PHY,也就是SMI总线上最多可以挂载32片PHY地址不一样的PHY设备。

SMI接口信号框图如下:

MDC:周期性时钟,提供最大2.5MHz的时钟频率。 MDC的最短高电平时间和最短低电平时间必须为160ns。MDC的最小周期必须为400ns。在空闲状态下,SMI管理接口将MDC时钟信号驱动为低电平。

MDIO:数据输入/输出,用于通过MDC时钟信号向/从PHY设备同步传输状态信息。

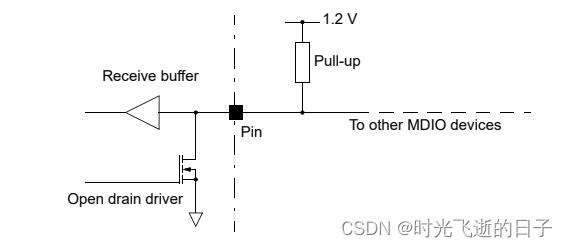

1.2 SMI硬件设计

通常主机MDC被配置为推挽输出,MDIO被配置为开漏输出,同时外接上拉电阻。在《IEEE802.3-2018》中MDIO接线的原理图如下:

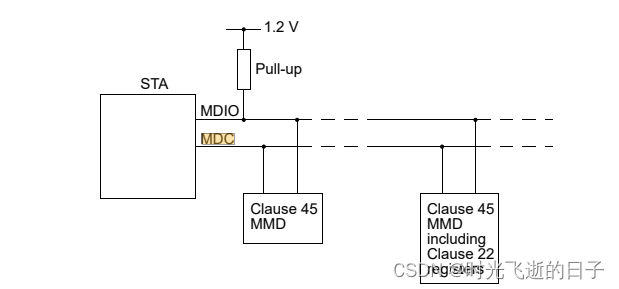

MDC和MDIO接线示意图:

其实,在很多时候PHY设备的MDIO并没有硬件上拉,我们可以在需要读取数据时将MDIO端口配置为上拉输入模式,发送数据时将MDIO配置为推挽输出模式。

1.3 SMI时序

下图为《TN1305 Technical note》中关于MDIO和MDC的时序示意图:

上图提取出来几个关键信息:

(1)MDC空闲电平为低电平

(2)MDIO数据在MDC上升沿采样,下降沿切换数据

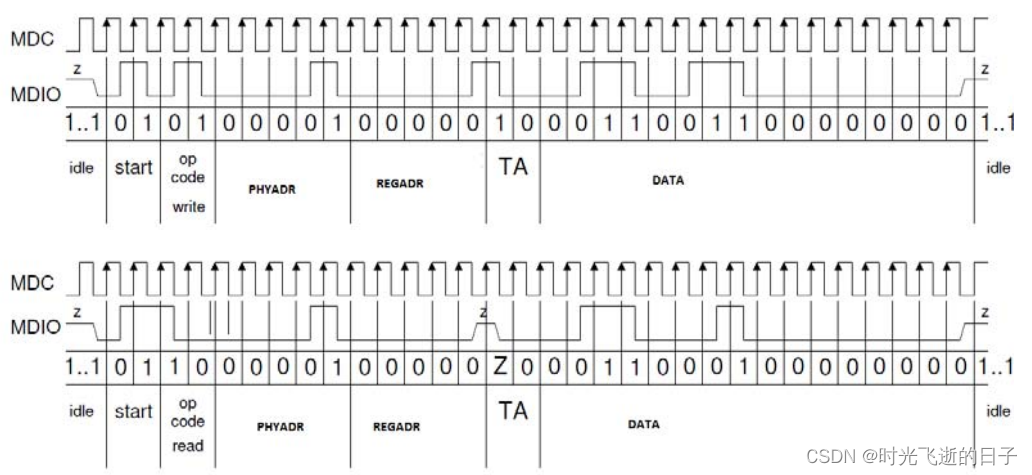

1.4 SMI帧格式

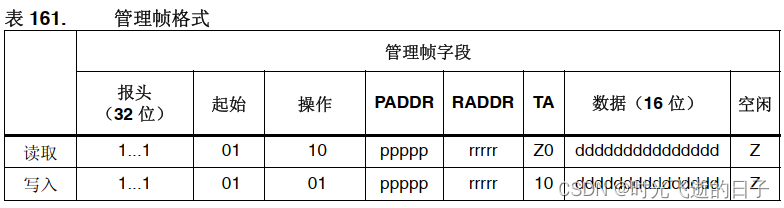

在《STM32F4XX中文参考手册》中给出的SMI帧格式如下:

SMI帧包括8个字段:

(1)前导码(Preamble):每次读写或写入PHY设备均需要先发送前导码,报头字段对应于MDIO线上32个连续的逻辑“1”位以及MDC上的32个周期。该字段用于和PHY设备建立同步。

(2)帧起始(ST):帧起始共2bit,值为01b。用于验证线路从默认逻辑“1”状态变为逻辑“0”状态,然后再从逻辑“0”状态变为逻辑“1”状态。

(3)操作(OP):定义正在进行的事件(读取或写入)的类型。01b表示写入,10b表示读取。

(4)PHY地址(PADDR):PHY地址一共有5位,因此可以寻址最多32个PHY设备。最先发送和接收地址的MSB位。

(5)寄存器地址(RADDR):寄存器地址一共有5位,因此可以最多对所选PHY设备的32个不同寄存器进行寻址。最先发送和接收地址的MSB位。

(6)周转(TA):周转字段一共有2位,它被定义在RADDR和DATA字段之间,避免在读取事件出现竞争现象。读取PHY设备时,主机将TA的2个位驱动为MDIO线上的高阻态。PHY设备必须将TA的第一位驱动为高阻态,将TA的第二位驱动为逻辑“0”。

写入PHY设备时,主机必须将TA字段设置为10b,PHY设备必须将TA的2个字段驱动为高阻态。

(7)数据(DATA):数据字段为16位。发送和接收的均是寄存器的MSB位。

(8)空闲:MDIO被驱动为高阻态。三态驱动器必须被禁止,PHY的上拉电阻使线路保持逻辑“1”状态。

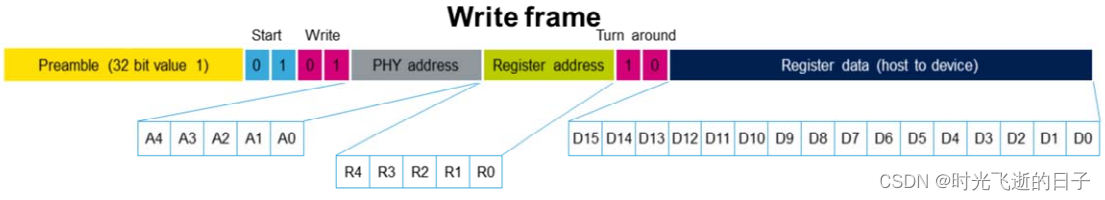

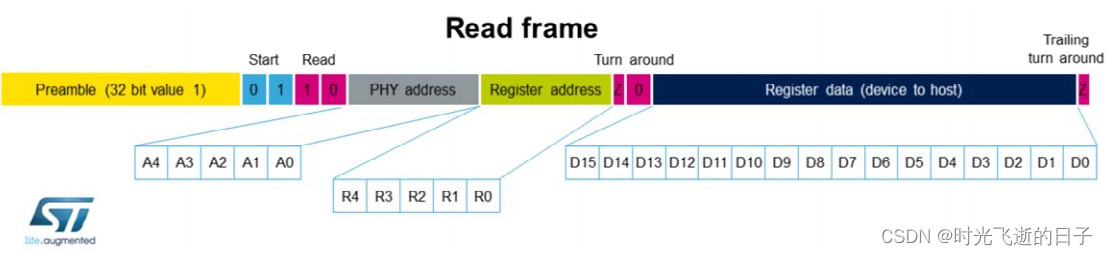

最后,可以用以下2个图片表示SMI的写入和读取PHY设备寄存器报文格式:

写入报文:

读取报文:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- JMeter 接口测试,一文详细讲解如何使用

- 从理论到实践:Dubbo 的 `<dubbo:service>` 与 `<dubbo:reference>` 全面指南

- JAVA8常用stream处理方法

- 一些意外的bug

- Python学习之路-函数进阶

- spring data mongo 在事务中,无法自动创建collection

- 逆天纪游戏搬砖游戏开发

- 校园一卡通平台:技术架构全解析

- 【优化】XXLJOB修改为使用虚拟线程

- 嵌入式-stm32-江科大-OLED调试工具