RH850P1X芯片学习笔记-Flash Memory

文章目录

Features

?代码flash容量:高达10兆字节的用户区域

编程方法:

- 通过串行接口与专用闪存编程器通信编程(串行编程)。

- 用户程序编程Flash(自编程)。

支持安全功能,以防止非法篡改或读取闪存中的数据。

支持保护功能,防止flash错误覆盖。

在Code Flash上支持OTP(一次性编程)

支持检测和纠正闪存中的错误。

支持BGO(后台操作)功能

- Code flash可以读取,而data flash正在编程。

- 当一个bank的flash被擦除/编程/读取时,另一个bank的flash可以被擦除/编程/读取。

Option Bytes寄存器值(设备的某些设置)可以在flash的扩展区域中配置

Code Flash上的最小可写单元是256bytes,Data Flash上的最小可写单元是4bytes

最小的可擦除单位是块。在Code Flash上8 kb或32 kb,在数据Flash上64bytes。

Clock Supply

下表列出了Flash控制逻辑(FACI)的时钟供应。

Block Diagram

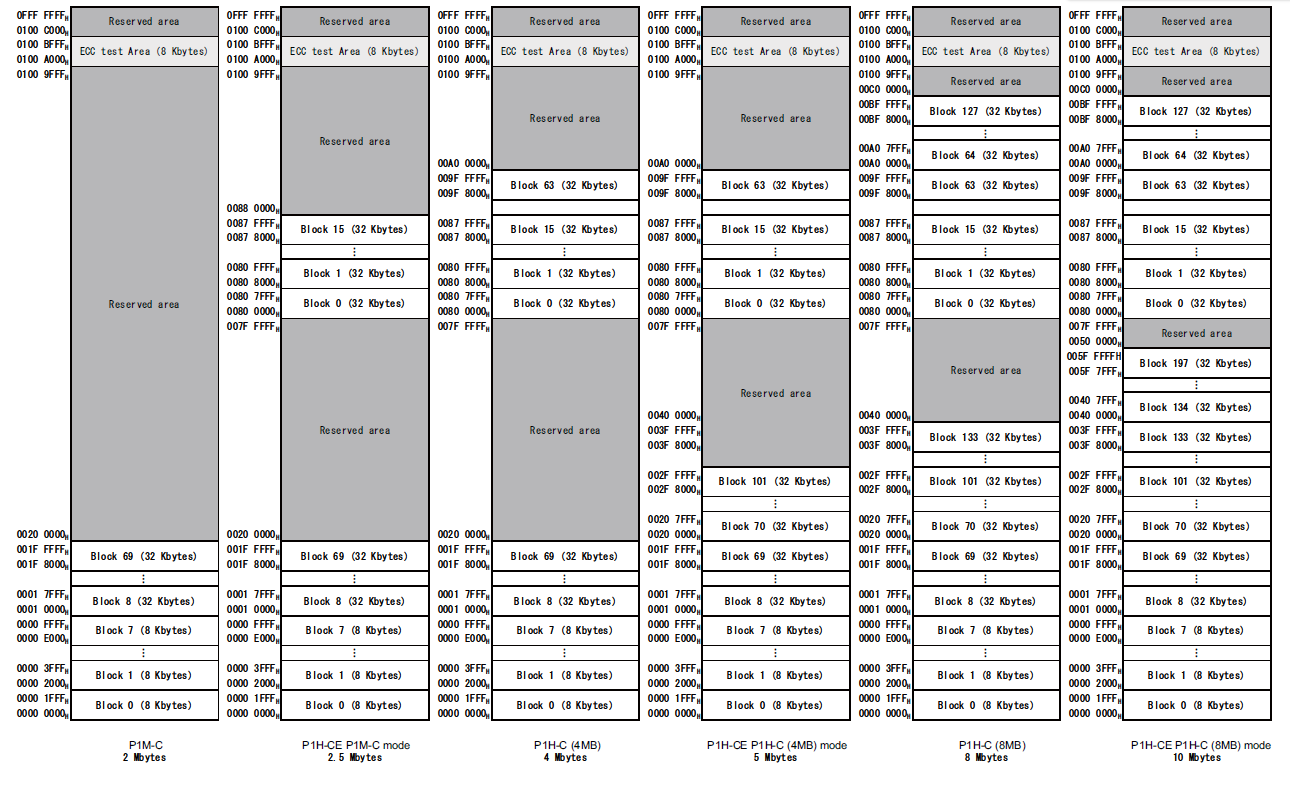

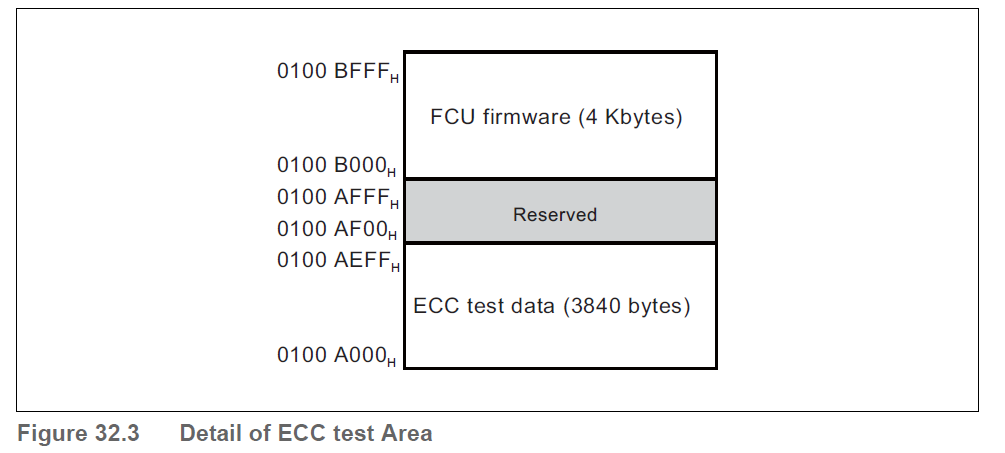

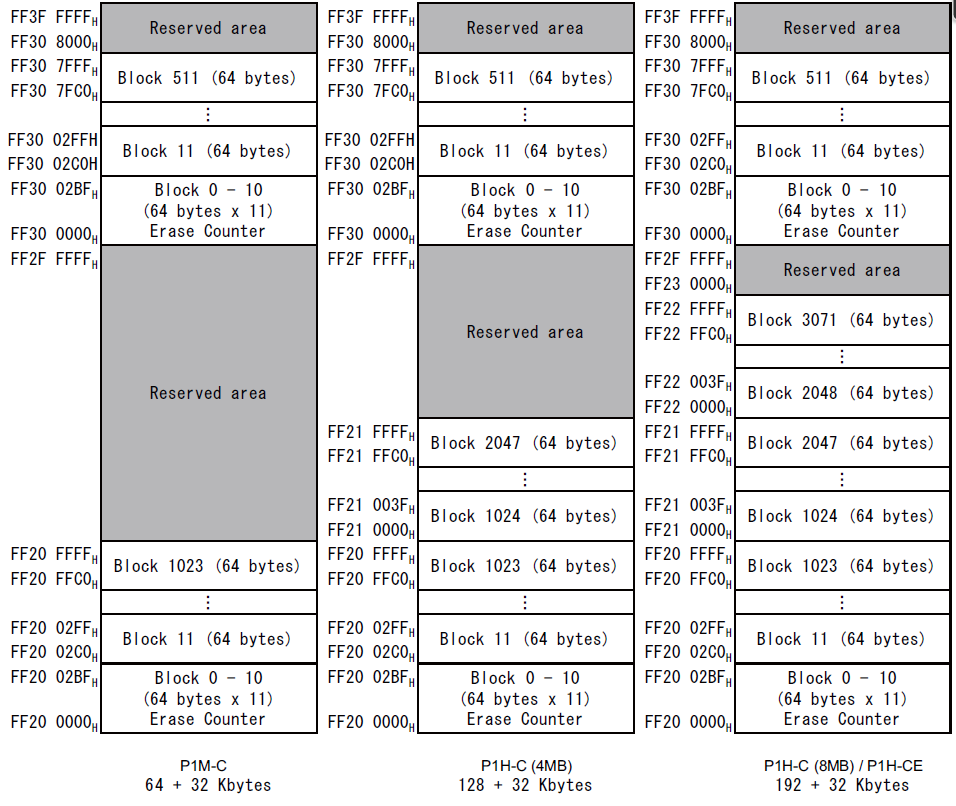

Flash Size

Memory Configuration

RH850/P1x-C代码闪存中的用户区分为8kbytes或32kbytes块,可单独擦除

RH850/P1x-C数据闪存中的数据区被划分为64字节的块,可以单独擦除。

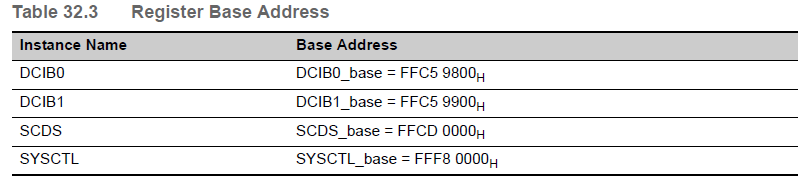

Registers

Register Base Address

List of Registers

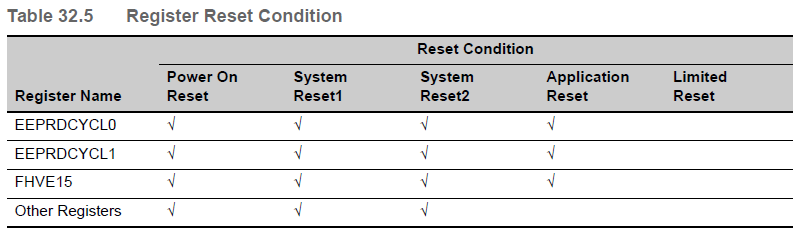

Register Reset Condition

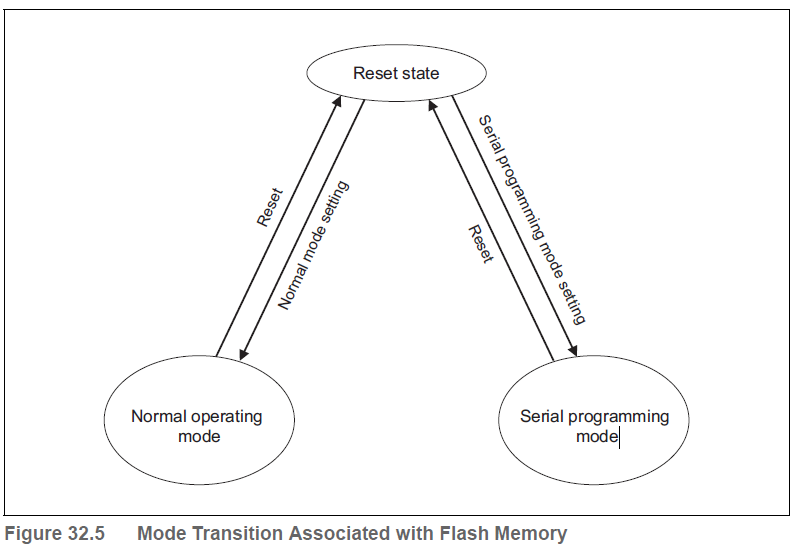

与Flash Memory相关的操作模式

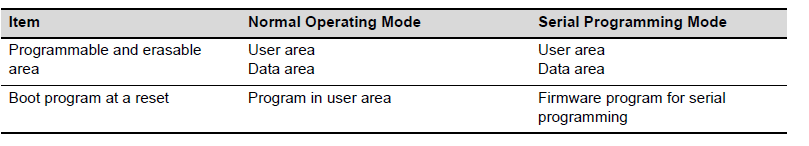

可编程和可擦除的flash区域以及复位后的启动程序取决于所选模式。模式之间的差异如表32.6所示

Functional Overview

RH850/P1x-C的片上闪存可以在安装到目标系统之前和之后进行编程,其编程功能采用专用的闪存编程器(串行编程)。

此外,还支持禁止在片上闪存中编写用户程序的安全功能,以防止程序被外部人员伪造

使用用户程序的编程功能(自编程)是适用于预期在目标系统的生产或装运之后修改程序的应用的方法。还支持对闪存区域进行安全编程的保护功能。

此外,通过在自编程期间利用对中断处理的支持,可以在各种条件下进行编程,例如与外部通信并行。

表32.7概述了编程方法和相应的操作模式。

Option Bytes

flash memory具有扩展区域(可选字节)来存储用户为各种目的指定的数据。设置的更改,例如使用选项字节的外设功能的初始设置,在从复位状态释放后生效。

OPBT0 — Option Byte 0

OPWDRUN0:该位启用或禁用WDTA0的自动启动。

0:禁用WDTA0自动启动。

1:启用WDTA0自动启动

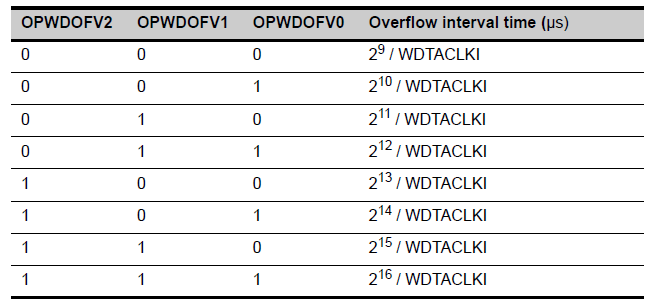

OPWDOFV2 to OPWDOFV0:这些位选择WDTA0、WDTA1的溢出时间

OPWD0MD:该位选择WDTA0、WDTA1的模式

0:慢速模式(WDTACLKI = 1/32 of CLK_IOSC)

1:快速模式(WDTACLKI = CLK_IOSC的1/1)

OPWDVAC:选择WDTA0、WDTA1变量启动代码)

该位指定触发寄存器,用于生成计数器重启触发器以避免计数器溢出。

0: WDTAnWDTE(固定)

1: WDTAnEVAC(变量)

注意:有关WDTA启动选项的详细信息,请参见第23节,窗口看门狗定时器A (WDTA)。

OPWDRUN1:该位启用或禁用WDTA1的自动启动(P1M-C除外)。

[p1h-c (4mb), p1h-c (8mb), p1h-ce]

0:关闭WDTA1自动启动。

1:启用WDTA1自动启动。

(P1M-C)

1:写值必须为1。

ETHDISABLE:以太网控制

0:表示以太网模块未启用。

1:以太网模块使能。

OPAUDR:选择AUD RAM监视器启用/禁用(仅限P1H-CE)

(P1H-CE)

0:禁用AUDR

1:启用AUDR

[P1M-C, P1H-C]

1:写值必须为1。

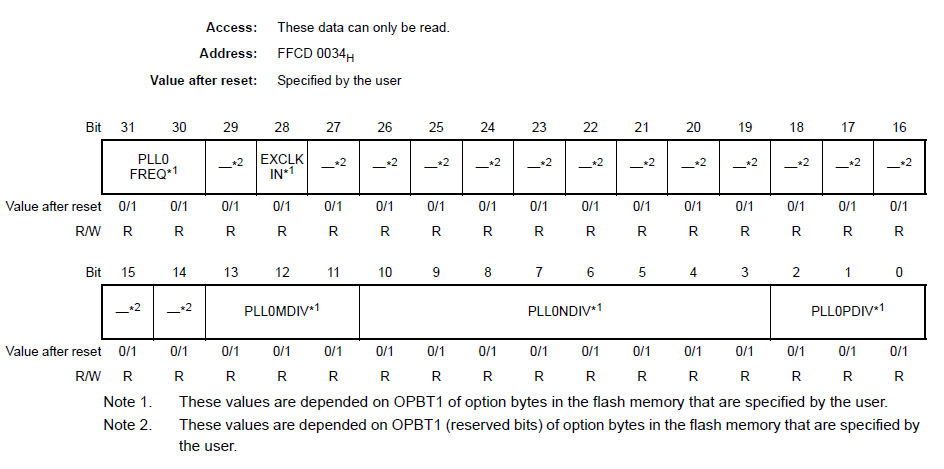

OPBT1 — Option Byte 1

OPBT1与时钟频率相关,如下图所示

PLL0FREQ:CLKD0DIV和CLKD1DIV的分频器配置以及SWDT时钟分频器。

位必须根据锁相环频率设置(由PLL0MDIVPLL0NDIV和PLL0PDIV设置)和所需的最大值。CPU频率(CLK_CPU)。

[P1M-C, P1H-CE]

00: PLL0 = 480MHz, CLK_CPU = 120MHz

01: PLL0 = 320MHz, CLK_CPU = 160MHz

10: PLL0 = 480MHz, CLK_CPU = 240MHz

11:禁止设置

(P1H-C)

00:禁止设置

01: PLL0 = 320MHz, CLK_CPU = 160MHz

10: PLL0 = 480MHz, CLK_CPU = 240MHz

11:禁止设置

一般设置为10b,即PLL0设置为480MHz,CLK_CPU设置为240MHz

EXCLKIN:选择外部时钟代替MOSC

0:选择外部时钟输入

1:选择晶振

一般设置为1

PLL0MDIV:PLL0 m分压器设置

001: 1/2 (mr = 2)

010: 1/3 (mr = 3)

other:禁止设置

一般设置为001

PLL0NDIV:PLL0 n分频器设置

0001_1111: 1/32 (nr = 32)

0010_0111: 1/40 (nr = 40)

0010_1111: 1/48 (nr = 48)

0011_1011: 1/60 (nr = 60)

other:禁止设置

一般设置为0011_1011

PLL0PDIV:PLL0 P分频器设置

000: 1/1 (pr = 1)

001: 1/2 (pr = 2)

other:禁止设置

一般设置为0

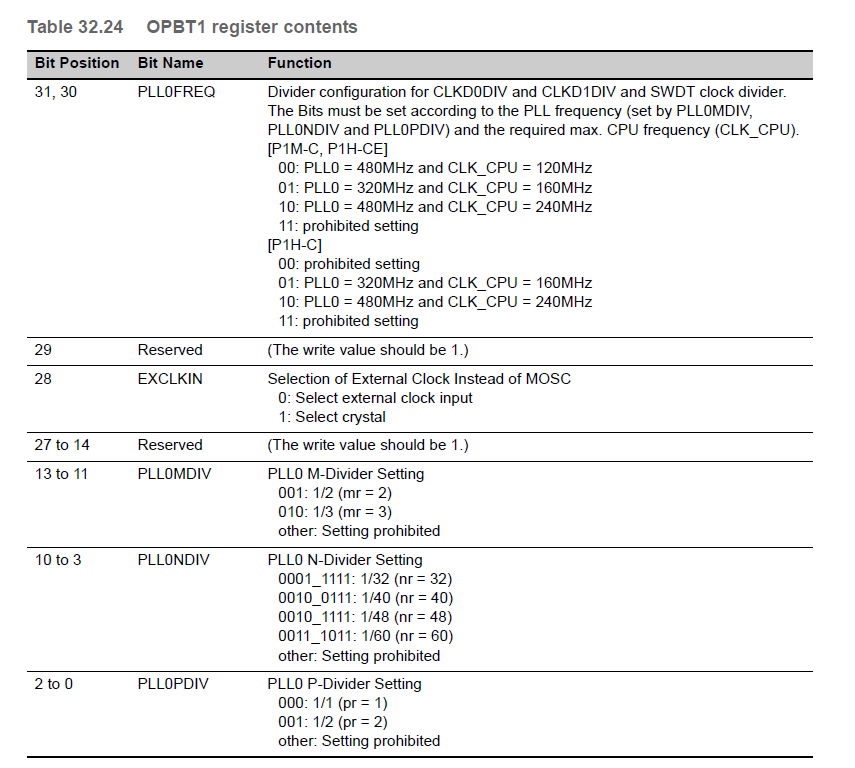

OPBT2 — Option Byte 2

OPJTAG1,OPJTAG0:选择调试接口

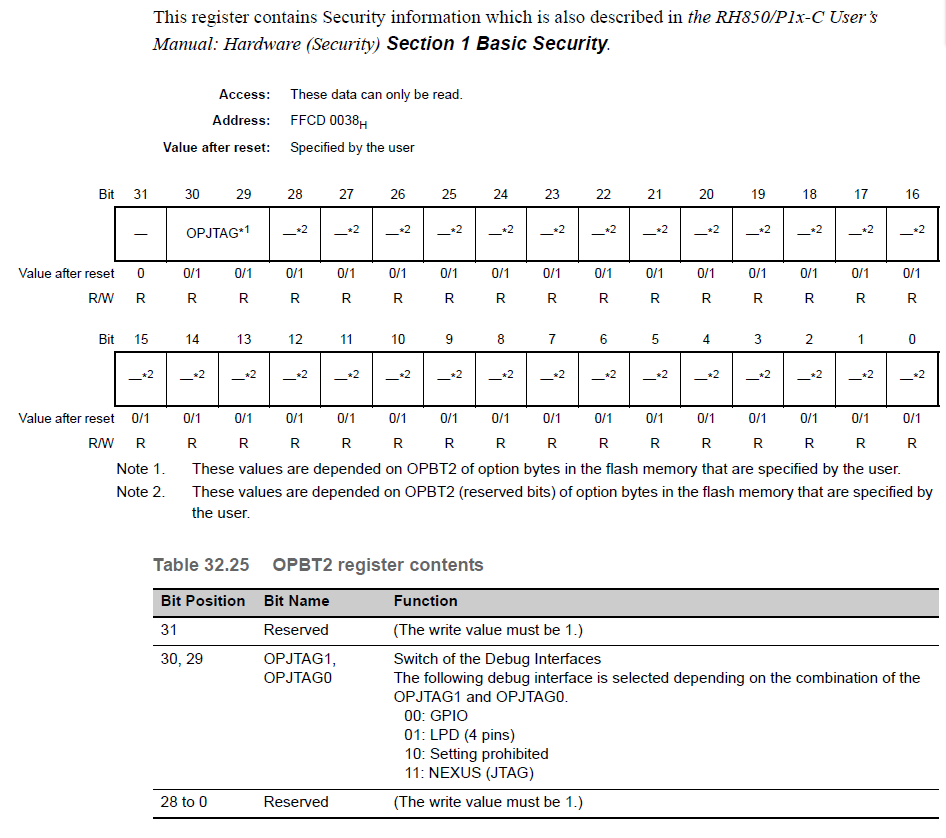

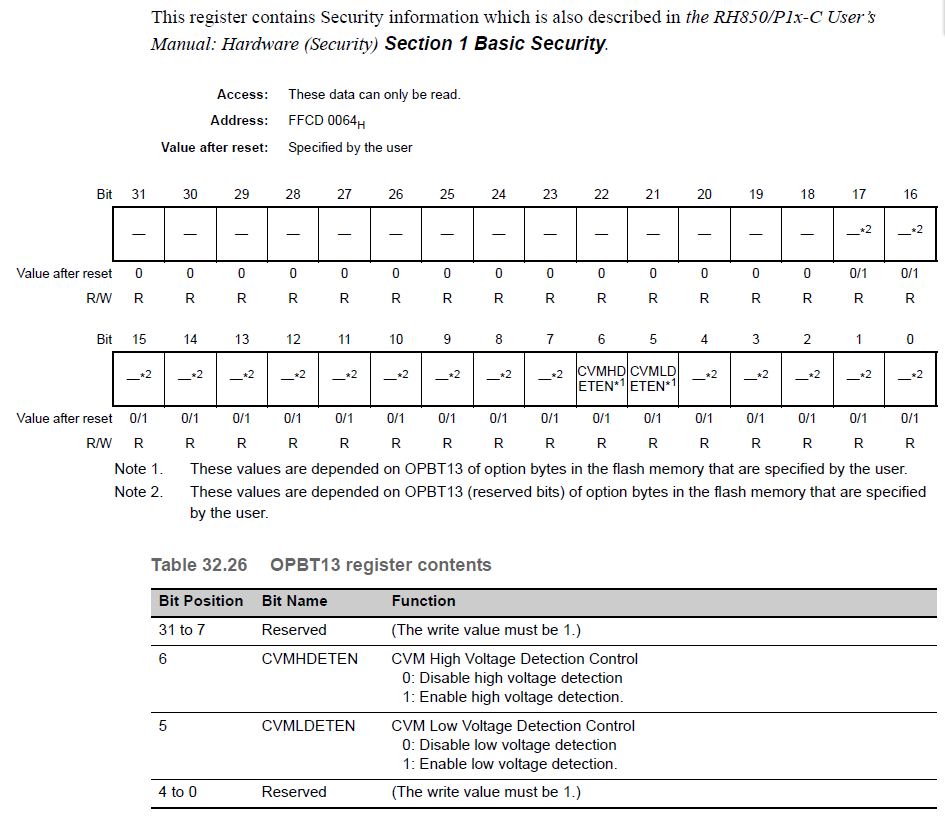

OPBT13 — Option Byte 13

CVMHDETEN:CVM过压检测控制,1使能

CVMLDETEN:CVM欠压检测控制,1使能

OPBT14 — Option Byte 14

EMF:仿真模式选择,只有P1H-CE可以用,P1M-C,P1H-C都需要写1

PE2PB:PE2校验位是否启用,1启用

RD_SEL:阻尼电阻配置

PE2DIS:是否使能PE2,0使能

STARTUPPE:选择Start up PE使能控制

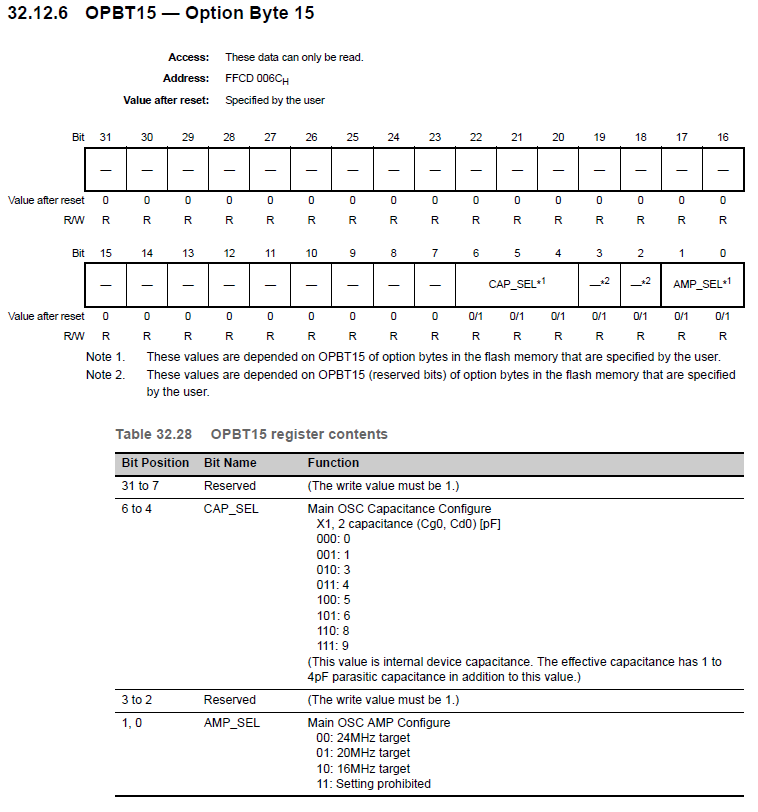

OPBT15 — Option Byte 15

CAP_SEL:主OSC电容配置

AMP_SEL:主OSC AMP配置

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 12.26 stm32mp157按键中断

- 混淆技术概论

- 使用BurpSuite测试访问控制

- Win10电脑蓝牙默认音量100的设置教程

- C语言常用库函数

- JVM-3-OutOfMemoryErrory内存溢出

- c++ vector 赋值 只能用push_back()赋值 ?使用下标赋值出错,不能使用标赋值吗?

- 神经网络:激活函数层知识点

- 我在阿里巴巴是是这样做架构师的

- 【HDFS-Client】FSOutputSummer#write1方法的细节