「Verilog学习笔记」并串转换

发布时间:2023年12月24日

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

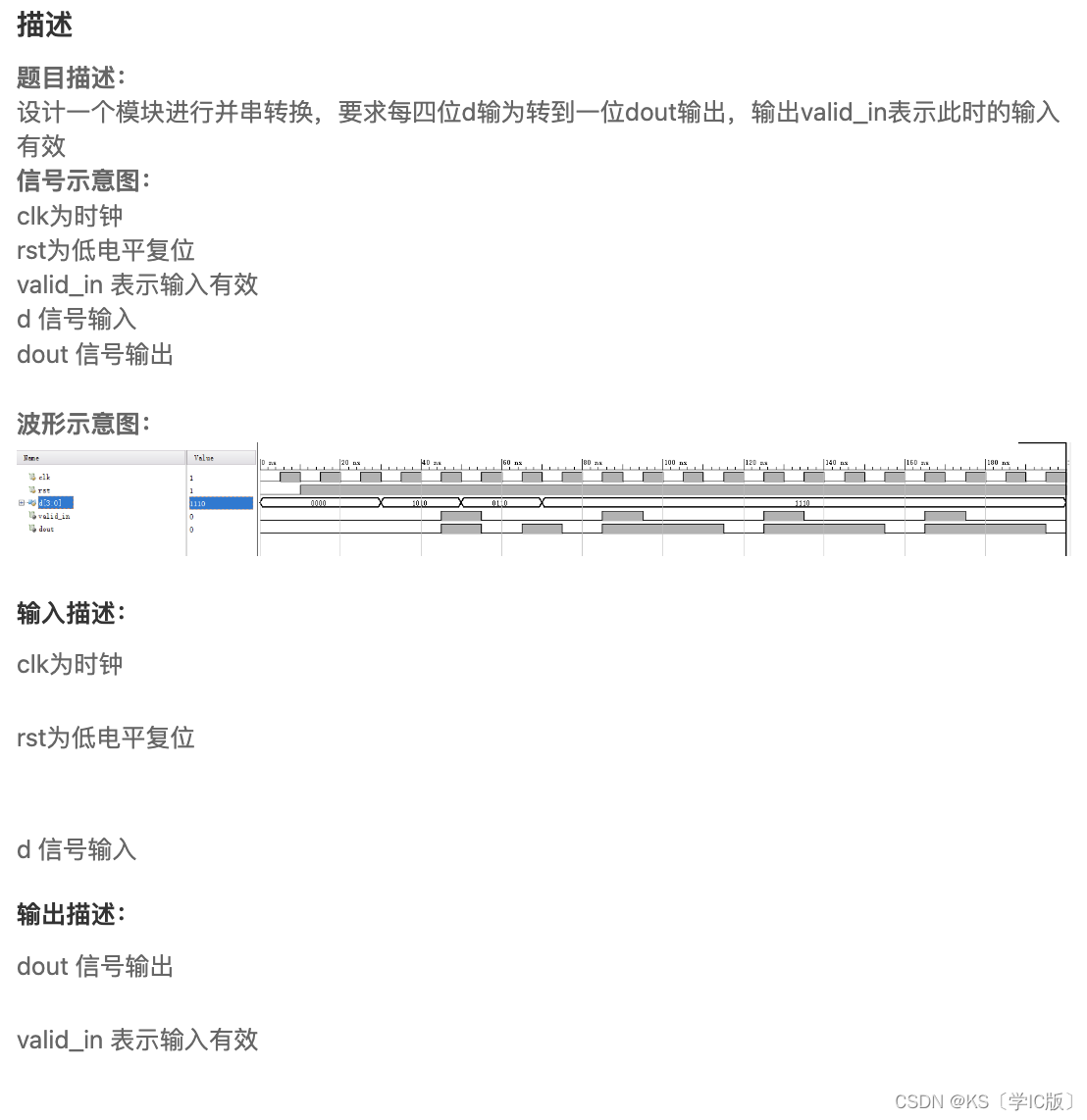

串并转换操作是非常灵活的操作,核心思想就是移位。串转并就是把1位的输入放到N位reg的最低位,然后N位reg左移一位,在把1位输入放到左移后的reg的最低位,这样循环,就可以得到,以最高位开始传输,最低位传输完成的N位数据了,最后将这N位数据同时输出,即为串行输入并行输出;并转串就是把并行的N位数据的最高位给1位输出,然后类似的循环左移就可以了。

串并转换操作是非常灵活的操作,核心思想就是移位。串转并就是把1位的输入放到N位reg的最低位,然后N位reg左移一位,在把1位输入放到左移后的reg的最低位,这样循环,就可以得到,以最高位开始传输,最低位传输完成的N位数据了,最后将这N位数据同时输出,即为串行输入并行输出;并转串就是把并行的N位数据的最高位给1位输出,然后类似的循环左移就可以了。

`timescale 1ns/1ns

module huawei5(

input wire clk ,

input wire rst ,

input wire [3:0]d ,

output wire valid_in ,

output wire dout

);

//*************code***********//

reg [3:0] data ;

reg [1:0] cnt ;

reg valid ;

always @ (posedge clk or negedge rst) begin

if (!rst) begin

data <= 0 ;

cnt <= 0 ;

valid <= 0 ;

end

else begin

if (cnt == 3) begin

data <= d ; // 并行输入

cnt <= 0 ;

valid <= 1 ;

end

else begin

cnt <= cnt + 1 ;

valid <= 0 ;

data <= {data[2:0], data[3]} ; // 每个时钟将数据左移,保证每位数据都能出现在最高位

end

end

end

assign dout = data[3] ; // 每个时钟上升沿读取当前数据的最高位,四个时钟读完

assign valid_in = valid ;

//*************code***********//

endmodule

文章来源:https://blog.csdn.net/m0_54689021/article/details/135179478

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 48V转5V降压IC:一款高效、外置MOS的SSOP-10降压IC

- shiro1.13认证流程核心-非框架整合版本

- k8s报错处理

- 基于数据挖掘机器学习的心脏病患者分类建模与分析

- 微信小程序长按图片识别二维码

- SSM医院管理系统----计算机毕业设计

- 爬虫之牛刀小试(五):爬取B站的用户评论

- Python 开发笔记

- Python编程基础:顺序结构、循环结构、程序跳转语句、pass空语句

- Web3:B站chainlink课程Lesson5:安装ganache