procise纯PL流程点灯记录

procise纯PL流程点灯记录

一、概述

此篇记录使用procise工具构造JFMQL15T 纯PL工程,显示PL_LED闪烁;

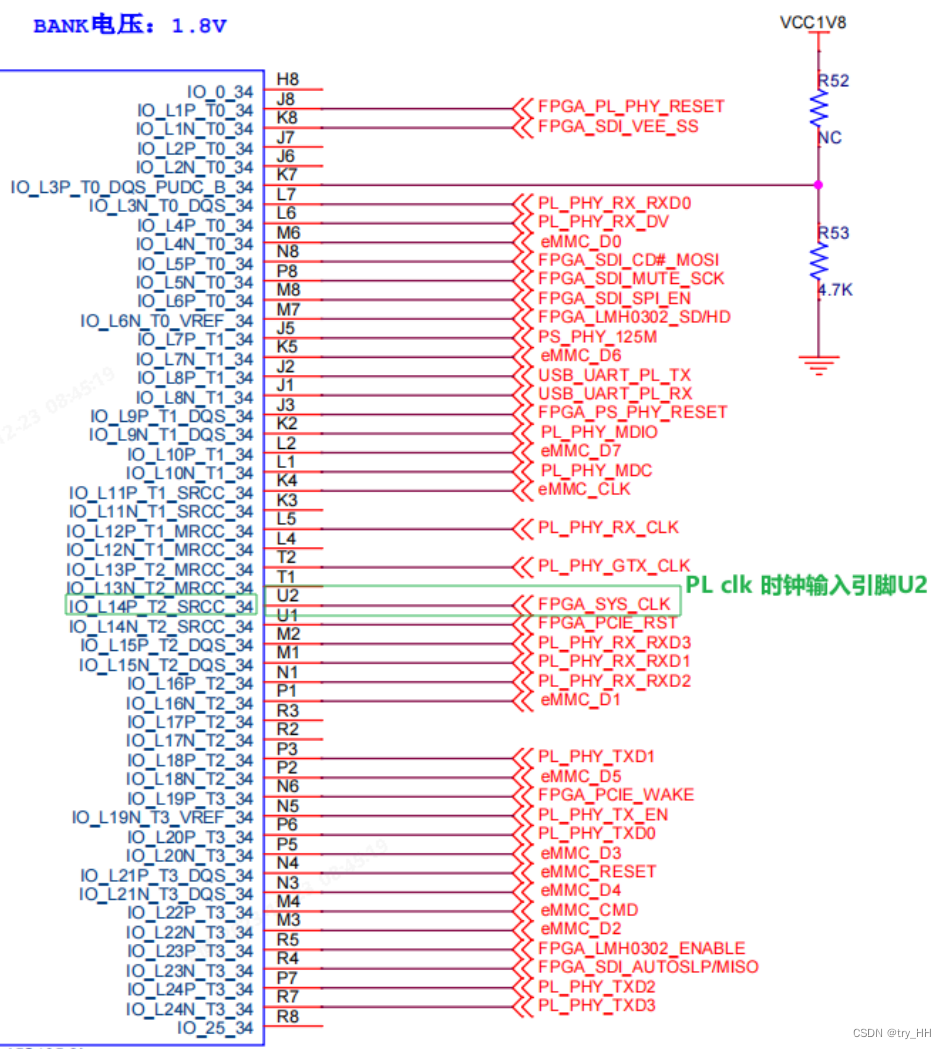

硬件说明如下:

时钟引脚 Pl_CLK: U2 ,IO_L14P_T2_SRCC_34

PL_LED1 : E2, IO_L17P_T2_AD5P_35 PL_LED2: D6, IO_L2N_T0_AD8N_35

PL_LED3 : F5, IO_L5P_T0_AD9P_35 PL_LED4: E3, IO_L21N_T3_DQS_AD14N_35

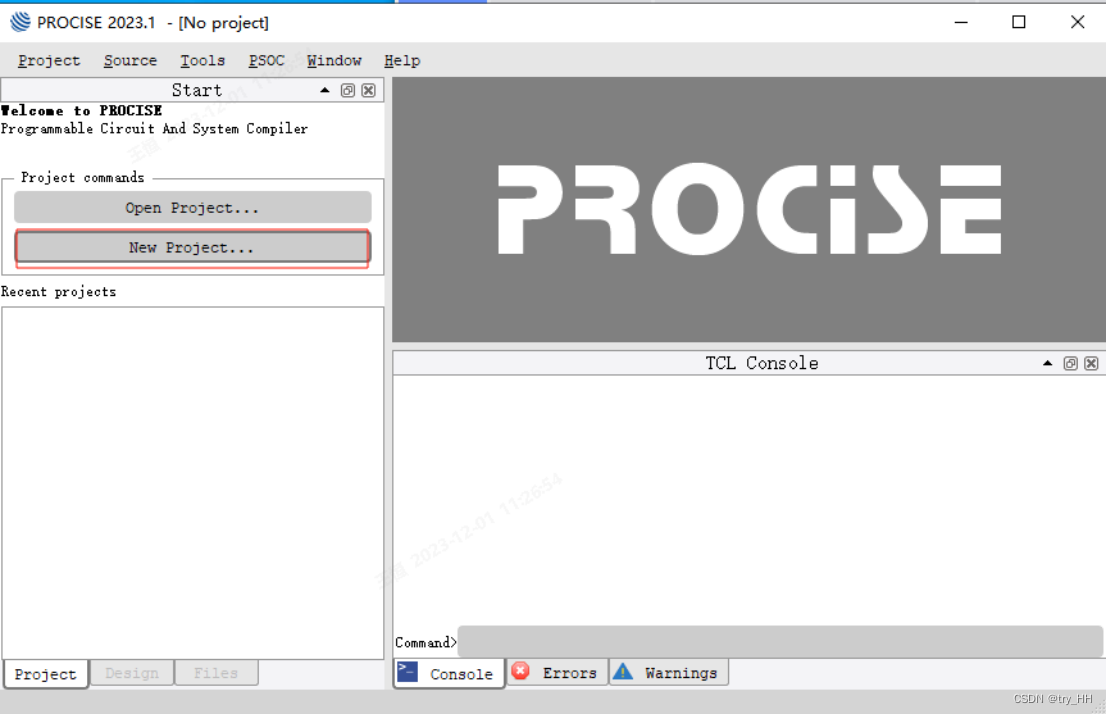

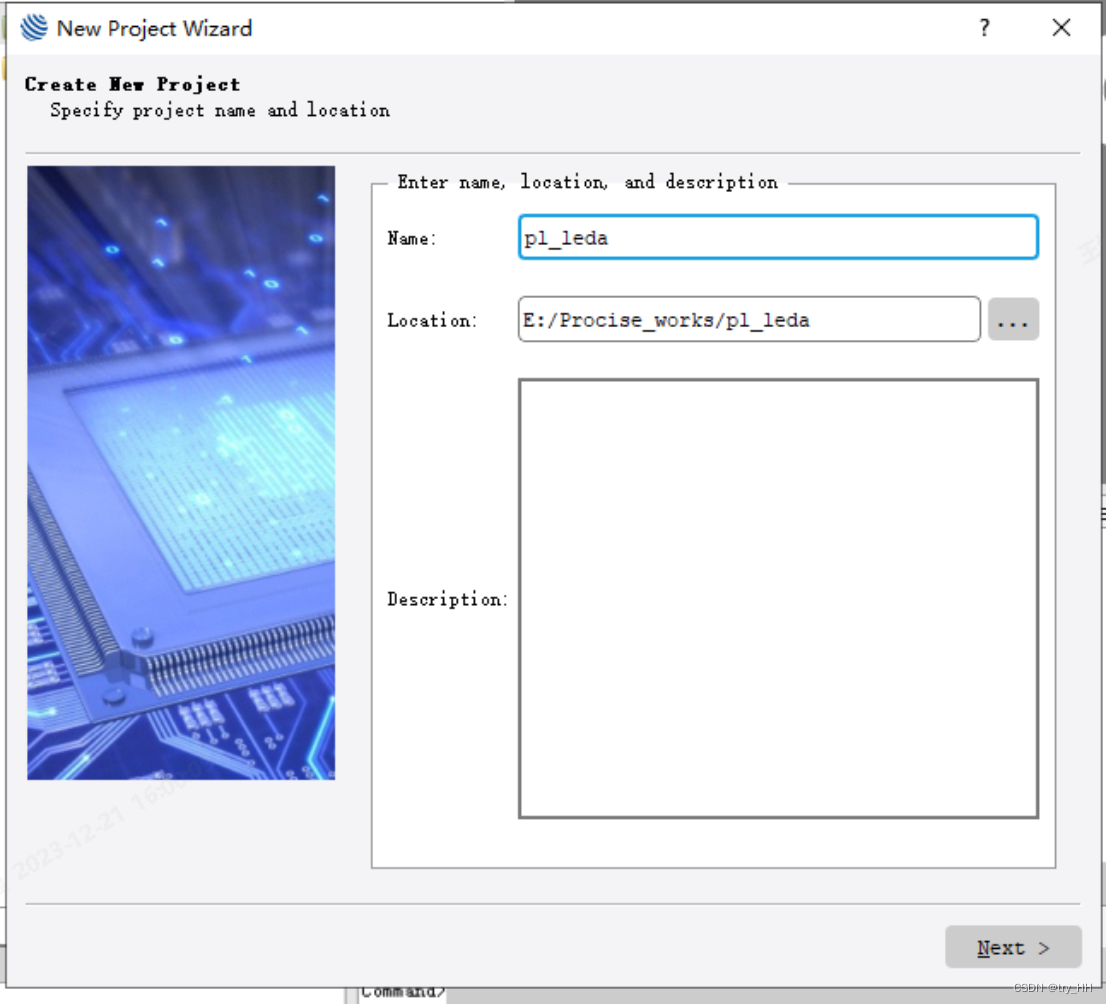

二、新建procise工程

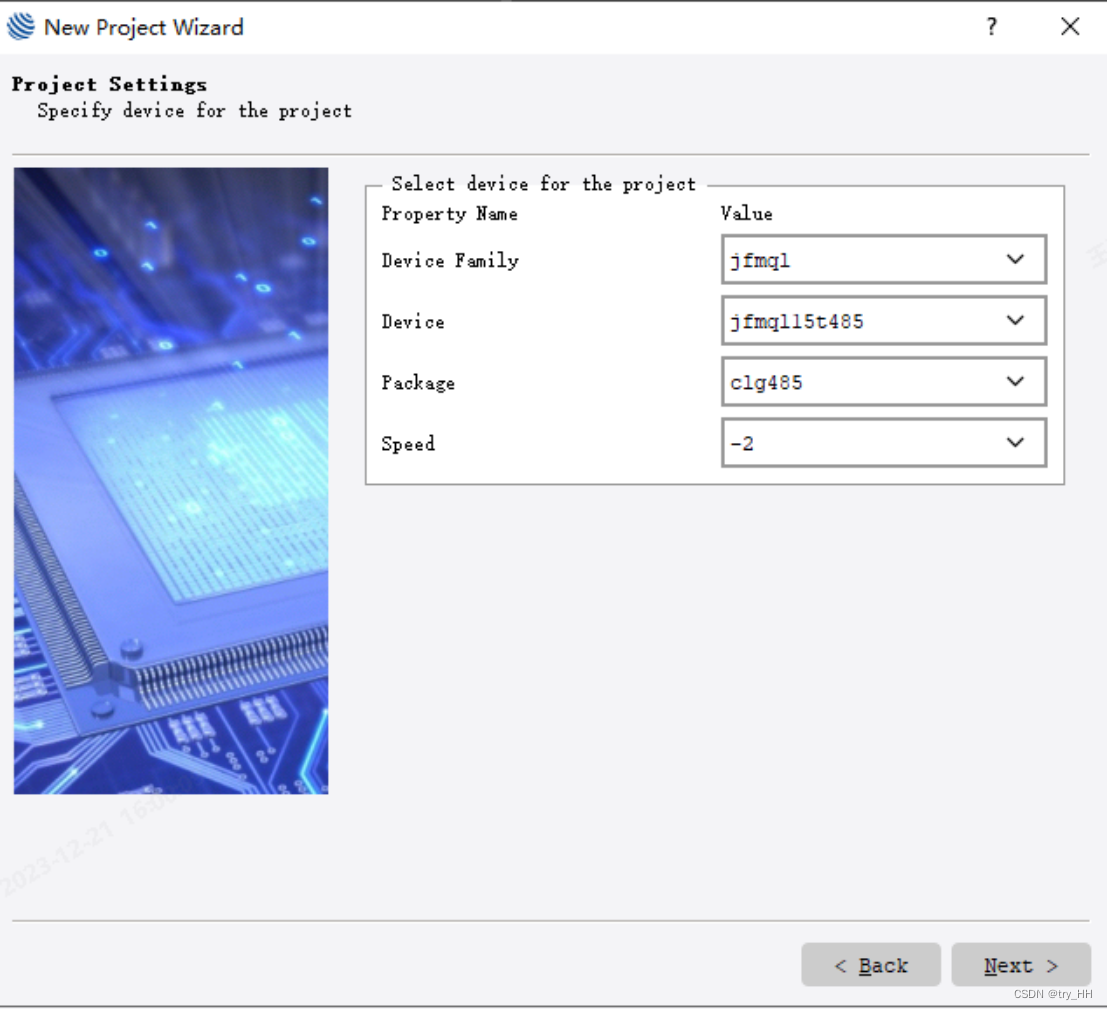

三、选择对应的Device

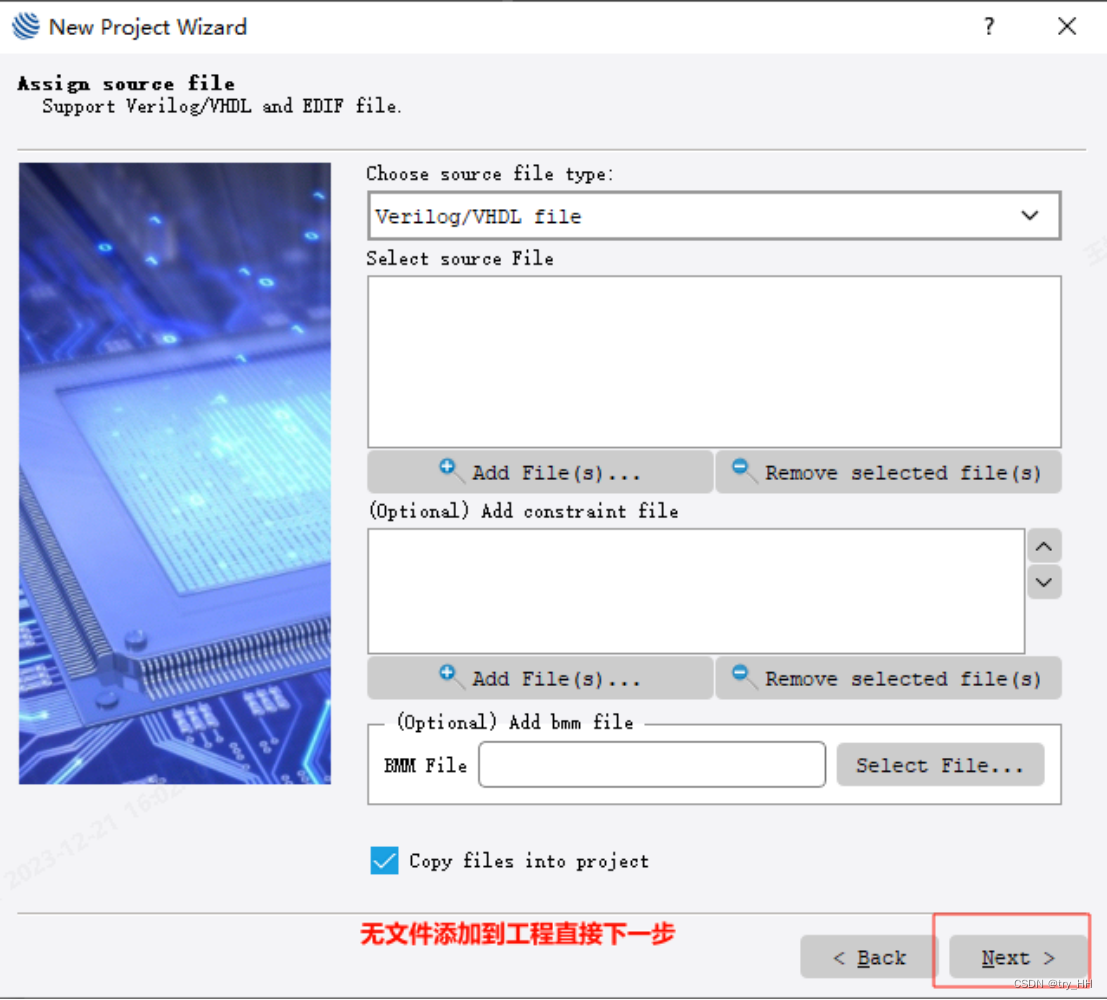

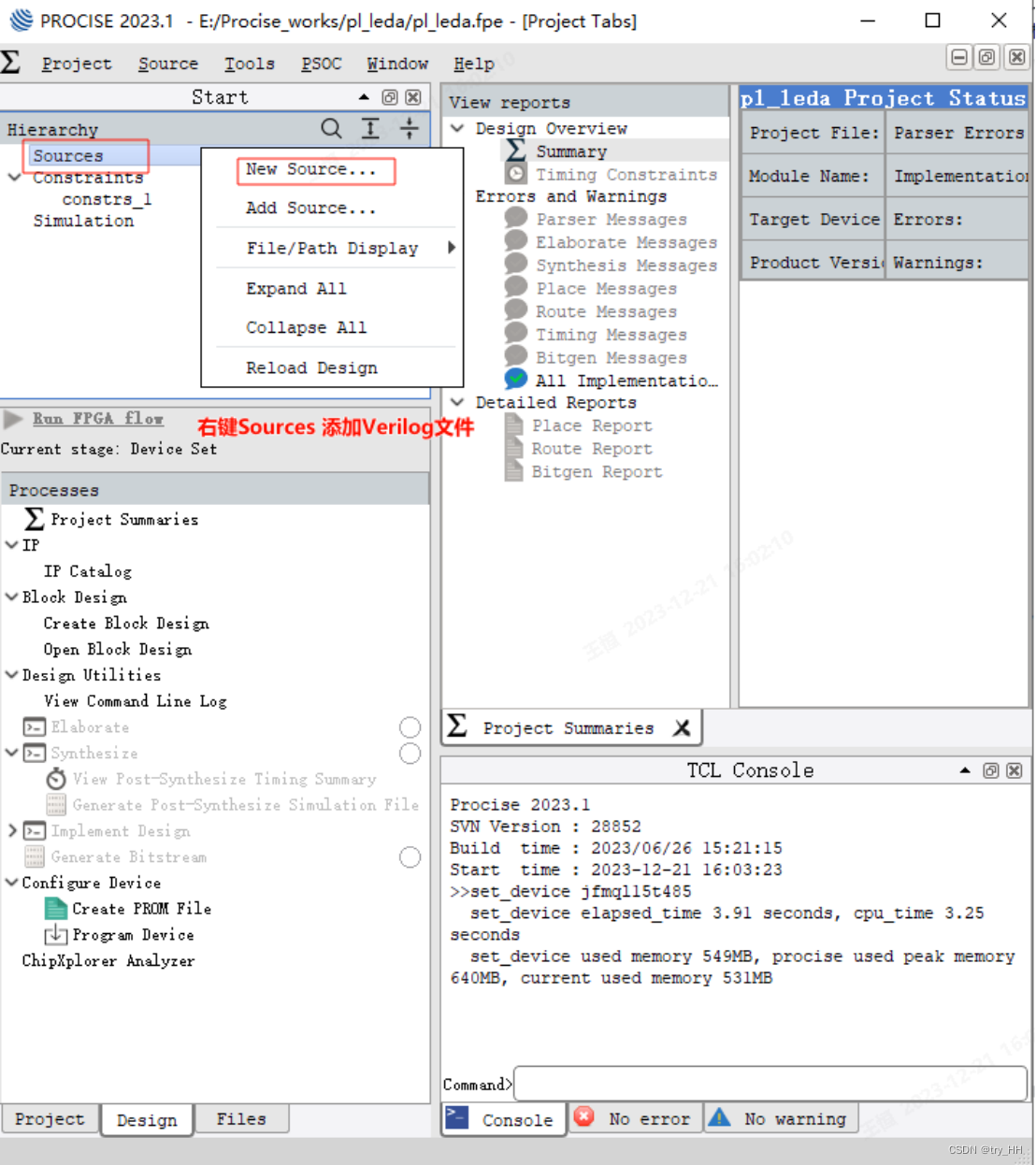

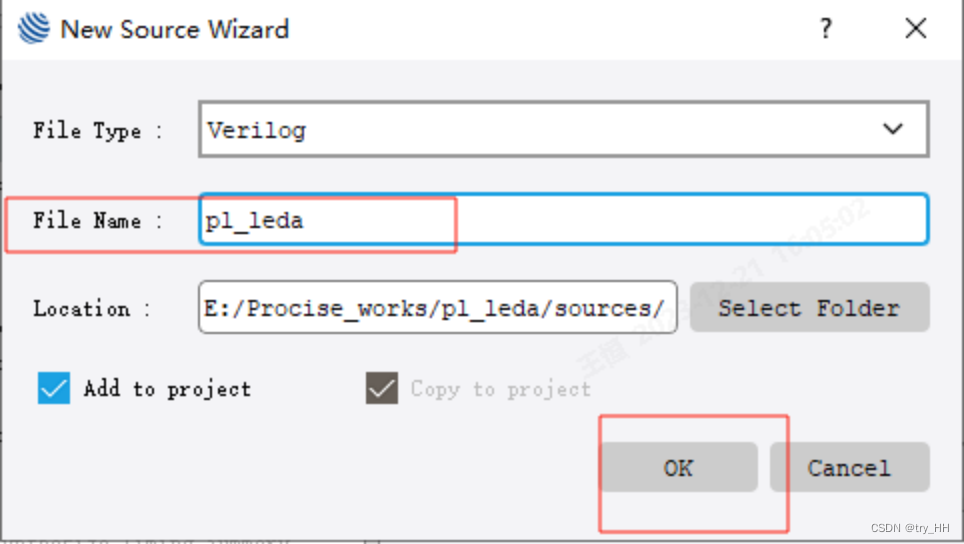

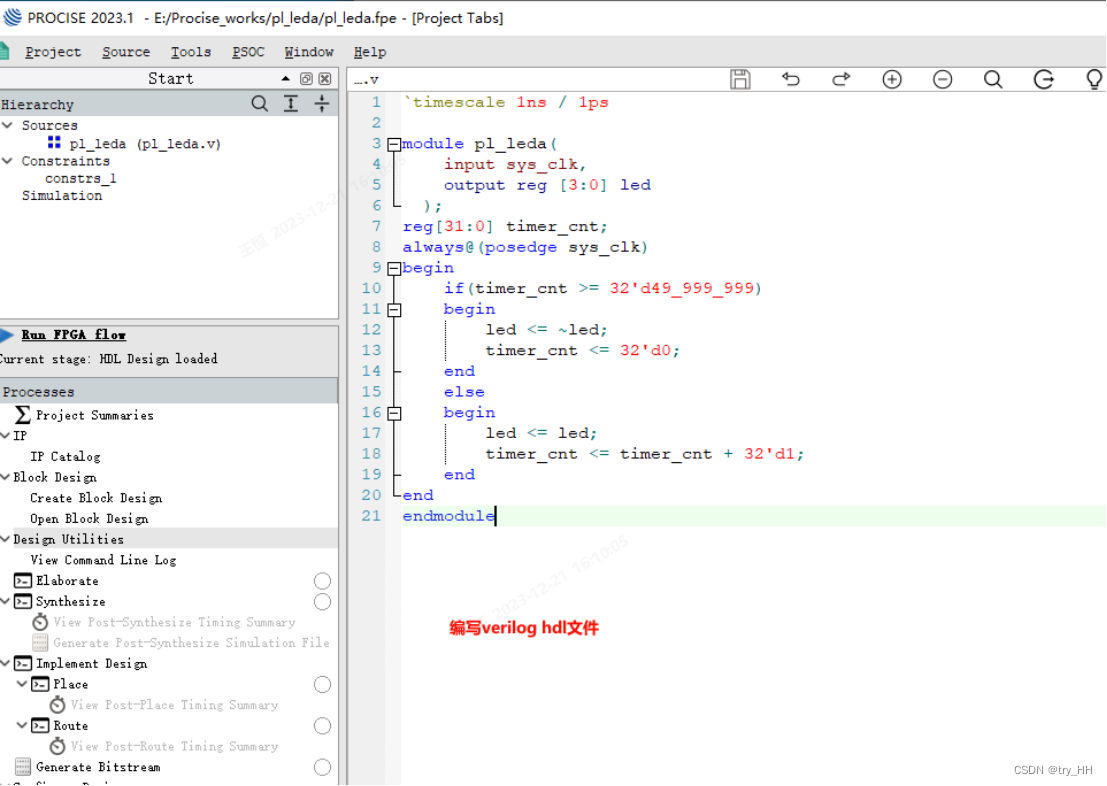

四、添加source Verilog文件

`timescale 1ns / 1ps

module pl_leda(

input sys_clk,

output reg [3:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk)

begin

if(timer_cnt >= 32’d49_999_999)

begin

led <= ~led;

timer_cnt <= 32’d0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32’d1;

end

end

endmodule

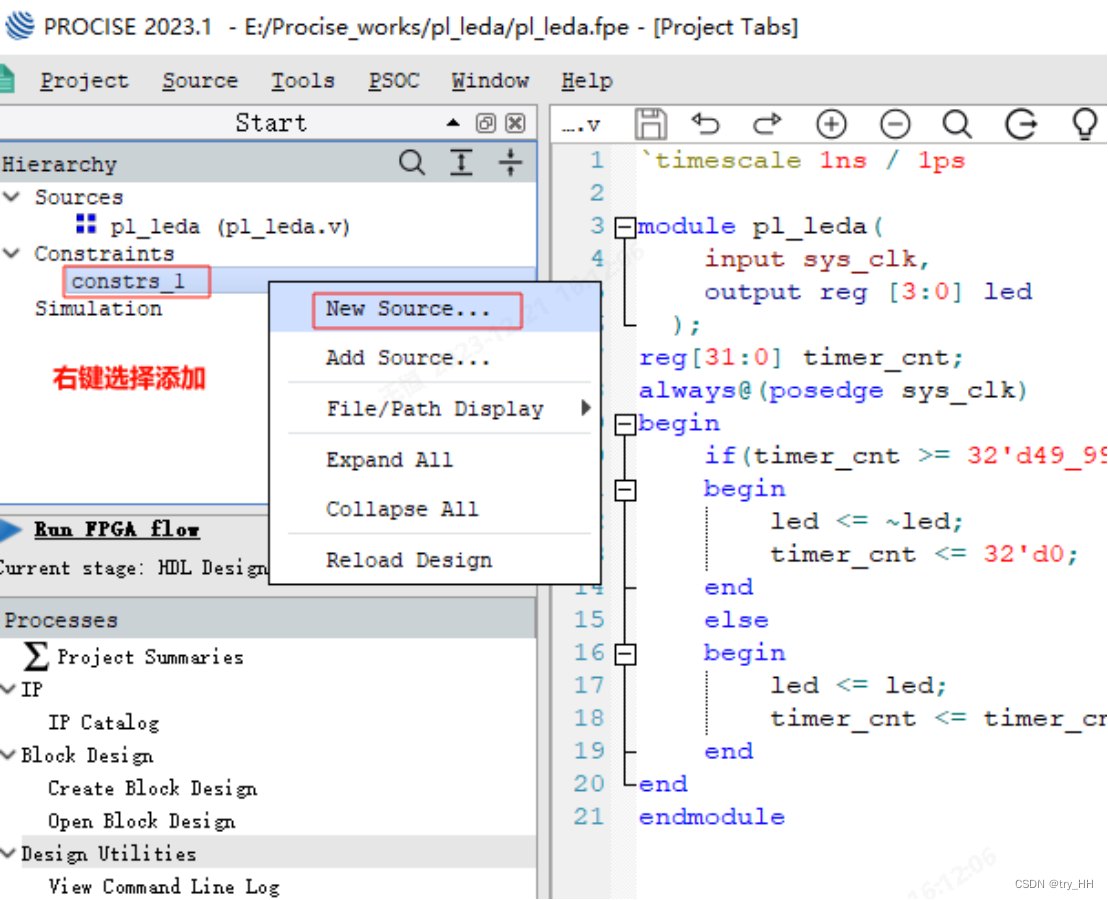

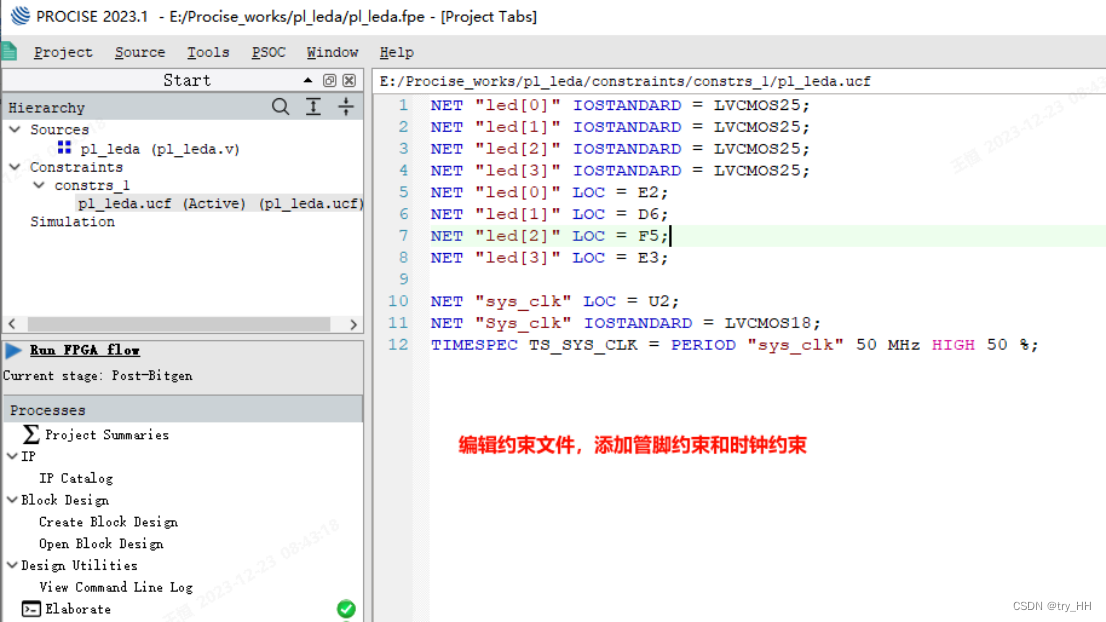

五、添加约束文件

编辑约束文件,添加管脚约束和时钟约束

NET “led[0]” IOSTANDARD = LVCMOS25;

NET “led[1]” IOSTANDARD = LVCMOS25;

NET “led[2]” IOSTANDARD = LVCMOS25;

NET “led[3]” IOSTANDARD = LVCMOS25;

NET “led[0]” LOC = E2;

NET “led[1]” LOC = D6;

NET “led[2]” LOC = F5;

NET “led[3]” LOC = E3;

NET “sys_clk” LOC = U2;

NET “Sys_clk” IOSTANDARD = LVCMOS18;

TIMESPEC TS_SYS_CLK = PERIOD “sys_clk” 50 MHz HIGH 50 %;

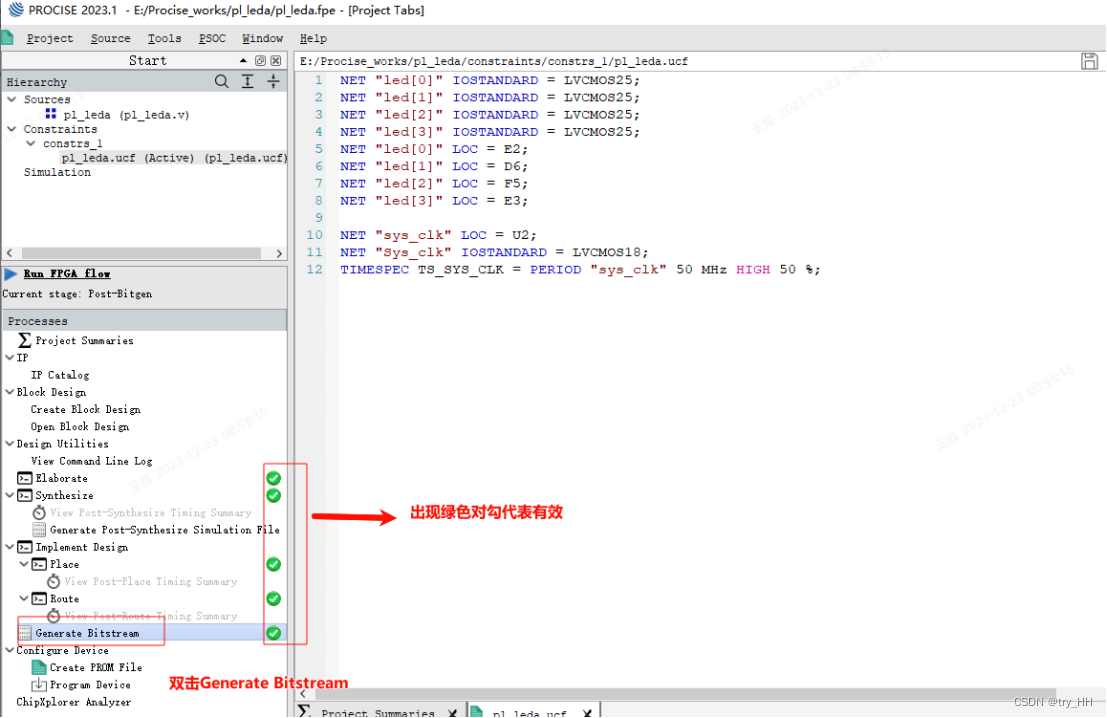

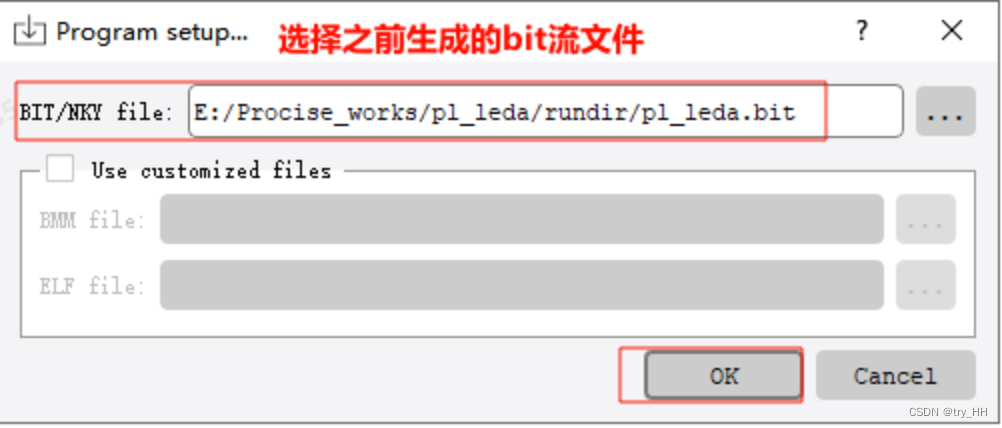

六、生成bitstream文件

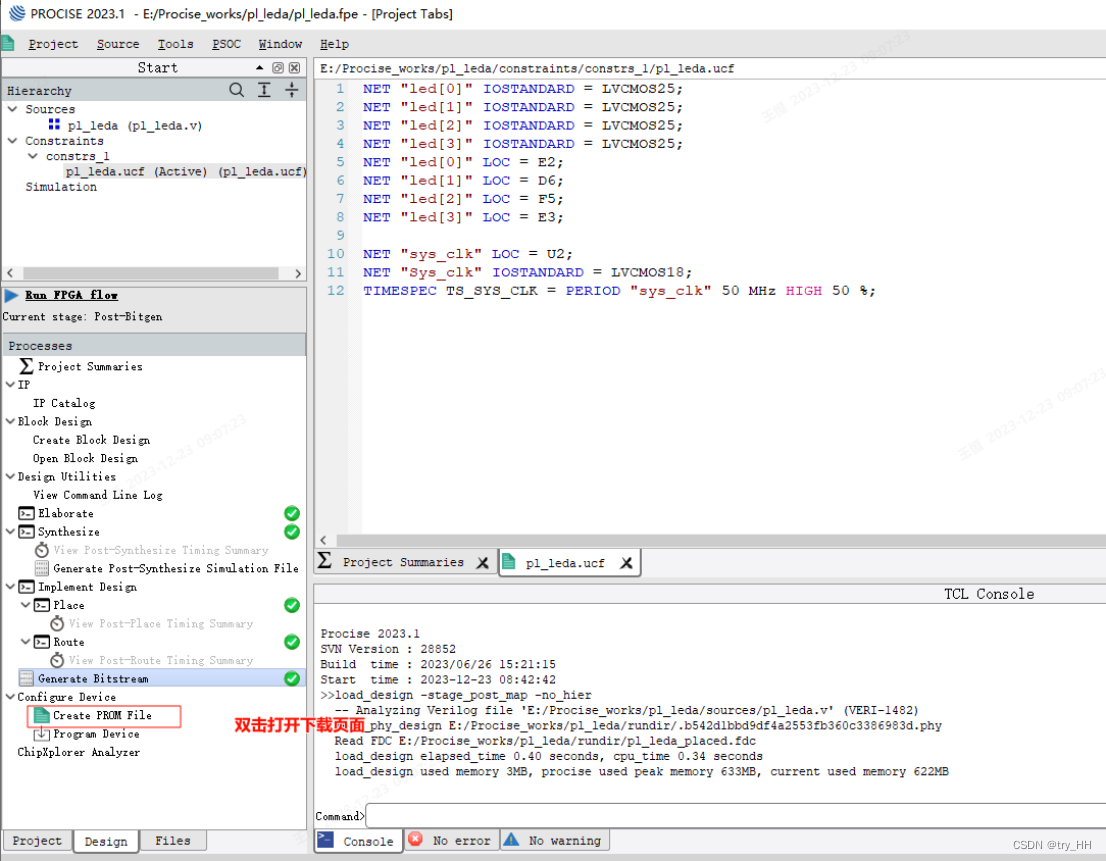

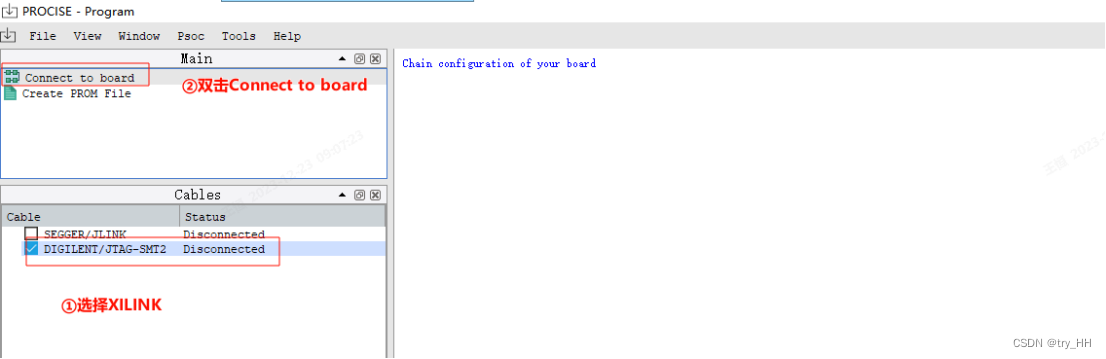

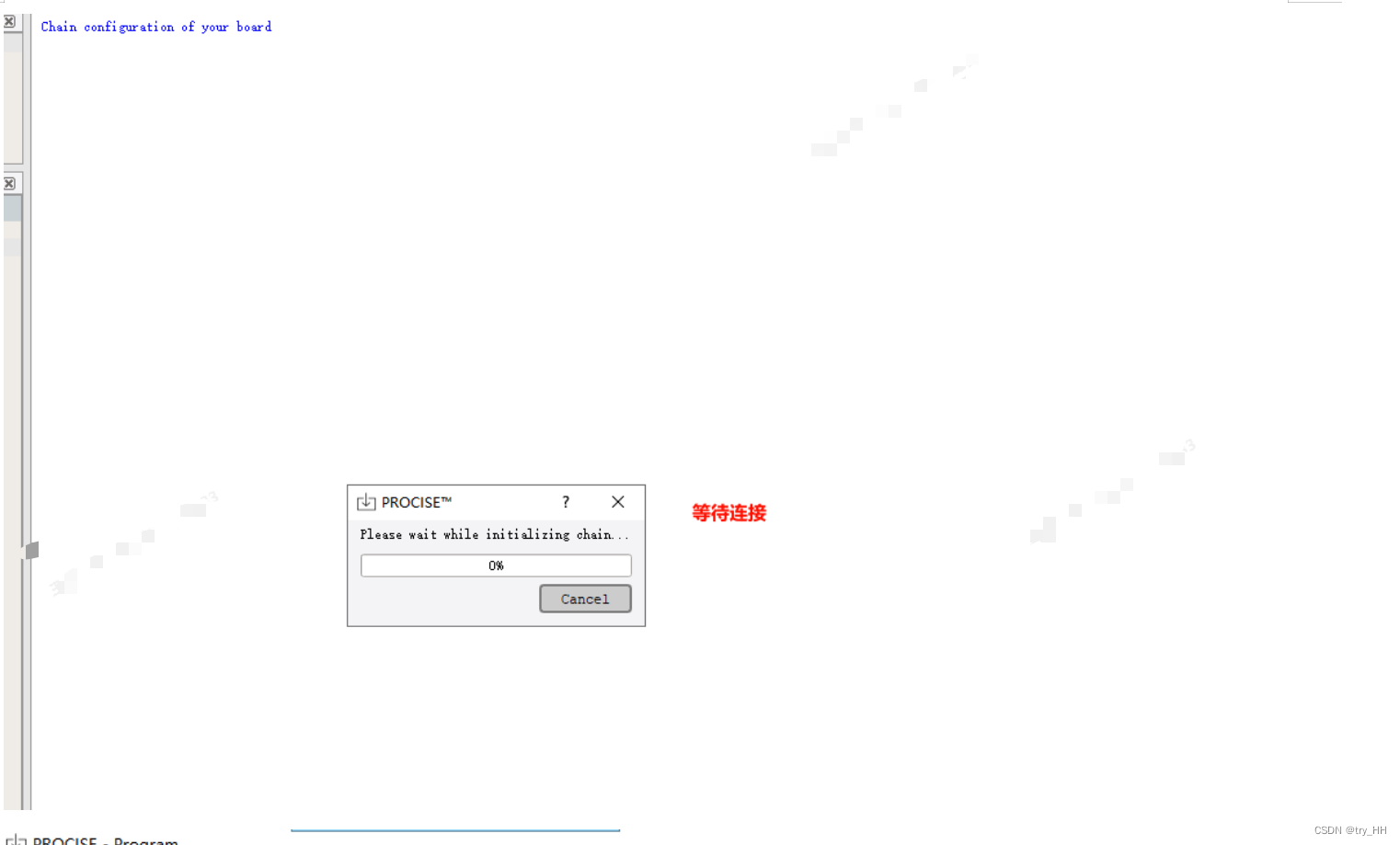

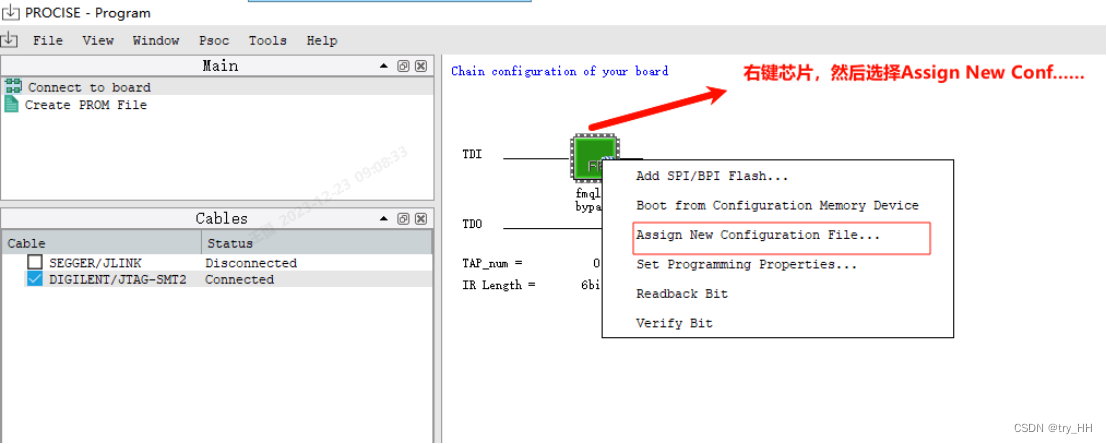

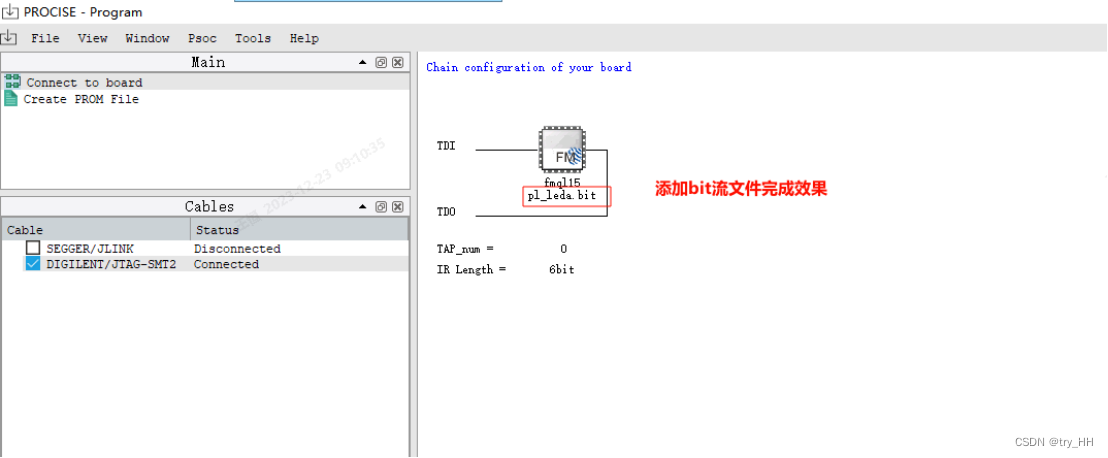

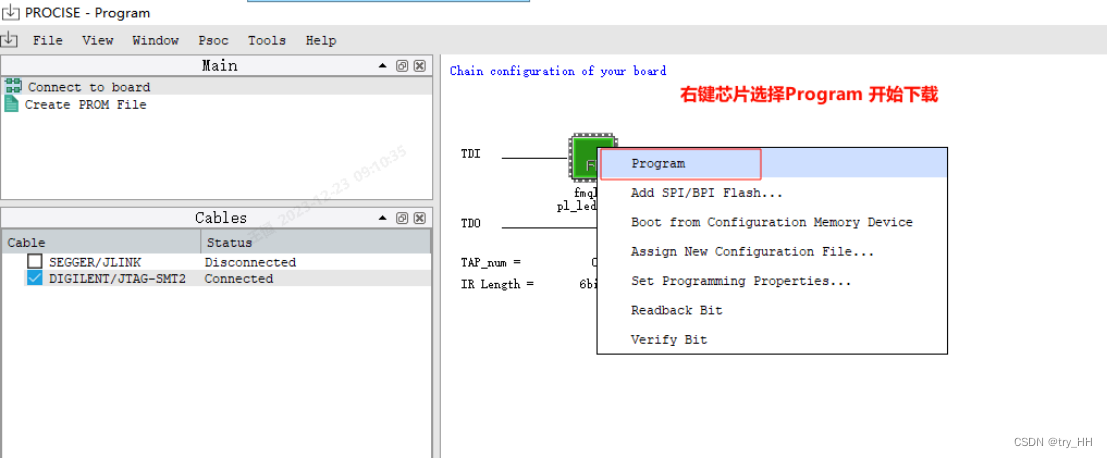

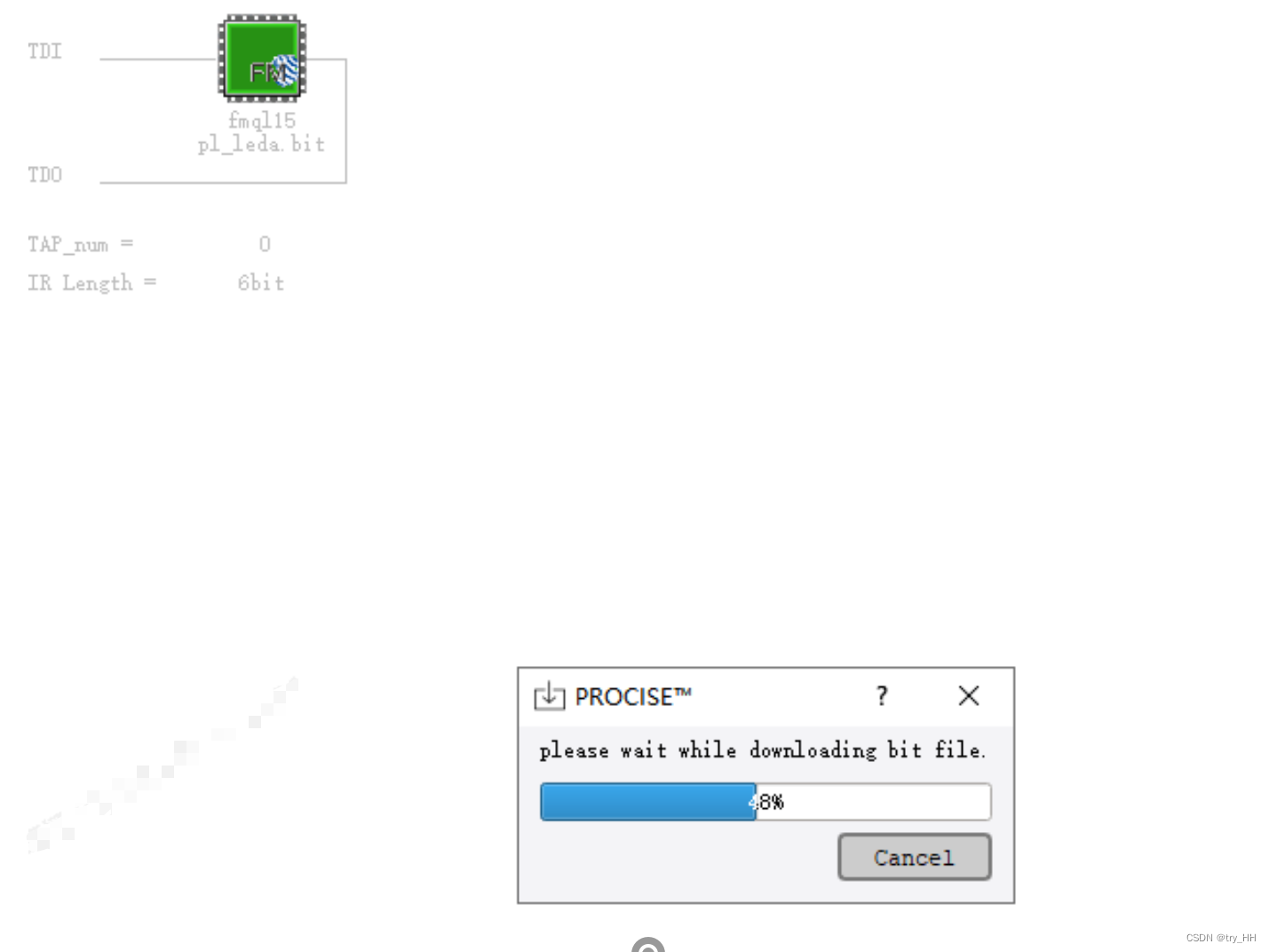

七、下载调试

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 外包干了3个月,技术退步明显。。。。。

- 你准备好迎接人形机器人时代了吗?

- 第1关:python数据库编程之创建数据库

- AMEYA360分享:太阳诱电导电性高分子混合铝电解电容器

- Ecology-编写代码批量实现自动创建员工账号

- RocketMQ 消费重试

- 基于联发科MT6761三防平板方案_三防手持终端PDA定制开发

- Linux上iPortal 配置80端口的http

- 代码随想录 Leetcode150. 逆波兰表达式求值

- 金三银四来了,助你一臂之力,10个专家级技巧助你优化React应用性能