FPGA之分布式RAM(2)

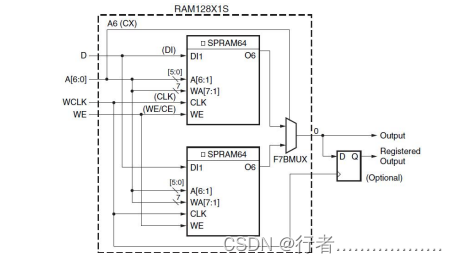

1) 128 X1 Single Port Distributed RAM

下图中可以看出来,通过2个LUT的组合使用可以串联实现更大深度的分布式RAM.下图中出现了F7BMUX的加入, F7BMUX可以用于LUT输出的选通.

原语调用:

RAM128XIS#(INIT(128'h00000000000000000000000000000000) // Initial contents of RAM)RAM128XIS_inst (

.O(O),// 1-bit data output

.A0(A0),

.Al(AI),// Address[1]

.A(A2),

.A3(A3),

.A4(A4),

.A5(A5),//

Α6(A6),// Address[6] input bit

D(D),//1-bit data input

.WCLK(WCLK), //Write clock input

.WE(WE)//Write enable input);?

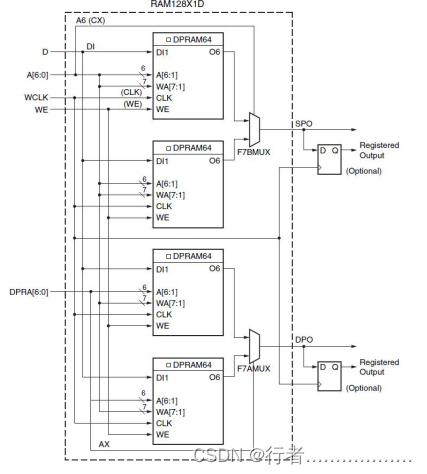

2) 128 X 1 Dual Port Distributed RAM

128x1的双口RAM需要4个LUT实现,正好是一个SLICEM,并且分别使用了F7BMUX和F7AMUX.?

?

原语调用:

RAM128XID#(INIT(128'h000000))

RAM128XID_inst (

.DPO(DPO),// Read port 1-bit output

.SPO(SPO)// Read/write port I-bit output

.A(A).//Read/write port 7-bit address input

.D(D),//RAM data input

.DPRA(DPRA), // Read port 7-bit address input

.WCLK(WCLK),//Write clock input

.WE(WE)// Write enable input);?

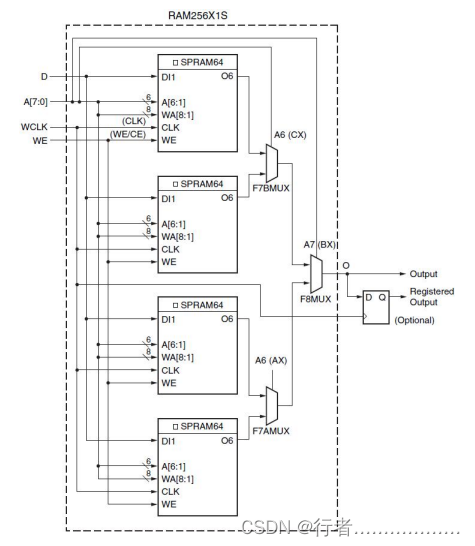

3)256 X1 Single Port Distributed RAM

256x1 的单口 RAM 需要 4个 LUT 实现,也正好是一个 SLICEM,并且分别使用了 F7BMUX 和 F7AMUX以及一个 F8MUX.

原语调用:

RAM256XIS #(INIT(256'h00000))

RAM256XIS_inst (

.O(O)// Read/write port 1-bit output

.A(A),// Read/write port 8-bit address input

.WE(WE)// Write enable input

.WCLK(WCLK), // Write clock input

.D(D)//RAM data input );

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- hive聚合函数之排序

- MongoDB vs MySQL:项目选择哪一个数据库系统?

- 智能销售助手:电话机器人与回拨系统的超强组合

- Pointnet++改进注意力机制系列:全网首发TripletAttention轻量且有效注意力机制 |即插即用,实现有效涨点

- pinia 给 state 指定变量类型

- springboot(ssm校园便利平台 校园跑腿管理系统Java系统

- 欢乐钓鱼^^

- 如何用GPT进行论文润色与改写?

- elementui+ <el-date-picker type=“datetime“/>时间组件的当前时间的180天之内的禁止选择处理

- 【SSM项目】云平台资源管理系统