FPGA硬件架构——具体型号是xc7k325tffg676-2为例

发布时间:2024年01月24日

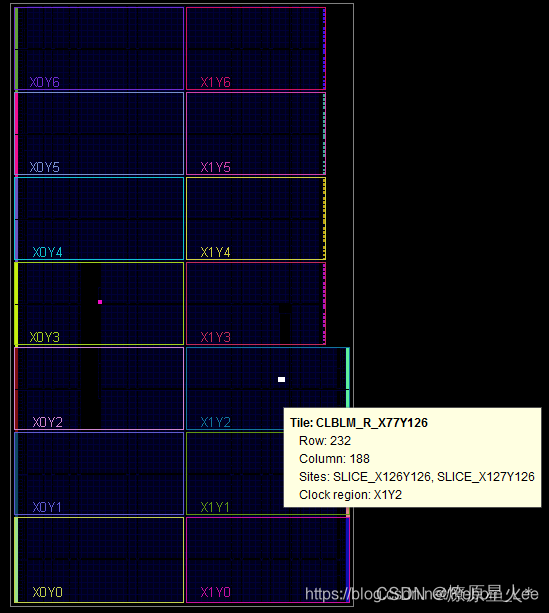

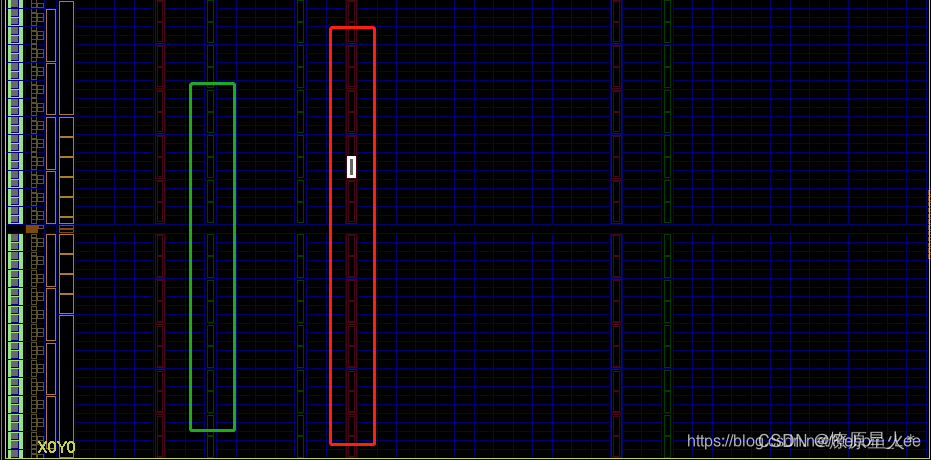

1.共如下图14个时钟域,XmYn(按坐标理解)

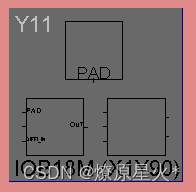

2.IOB(IOB为可编程输入输出单元,当然在普通Bank上的IOB附近还有很多时钟资源,例如PLL,MMCM资源。),

2.1 FPGA的Bank分为HP Bank和HR Bank,二者对电压的要求范围不同,HR支持更大的电压范围。一个只能同时接一组电压。

2.2?如下为单个IO的结构

可见一个IOB里面不仅包含PAD(因该是引脚在意思),还有IBUF以及OBUF

2.3.基本可编程逻辑单元(CLB),每个CLB包含两个SLICE(SLICE包含两种类型分别为SLICEL和SLICEM)

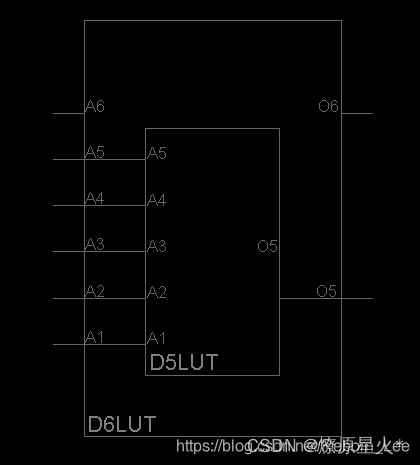

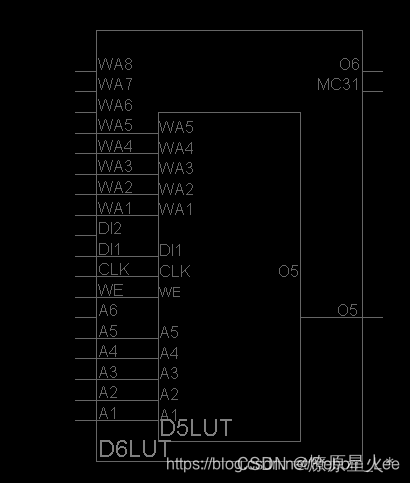

2.4SLICEL和SLICEM的区别在于LUT的不同,下图1边为SLICEL的LUT,下图2为SLICEM的LUT:

可见,SLICEM的LUT更加的强大,可以配置为LUT,RAM,ROM或移位寄存器,因此可以实现LUT的逻辑功能,也能作为存储单元和移位寄存器。

3.BLOCK RAM——(当我们要实现一个SRAM,FIFO以及ROM等,我们需要选择是使用LUT资源呢还是BLOCK RAM资源。)

4.DSP48绿色框内

(

可用使用这一资源进行加法,乘法运算,这样会节省LUT资源。例如我做FFT的时候,其中的复乘法就用了大量的DSP资源。)

5.GTX固核——GTX固核位于MGT Bank上,在IOB附近,

文章来源:https://blog.csdn.net/Pual_Georg/article/details/135813891

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 基于 Haar 特征的人脸检测

- 数字化转型之路为何道阻且长?

- JAVA设计模式(三)-原型

- el-select与treeselect下拉框重叠、兼容性问题

- 企业面临的典型网络安全风险及其防范策略

- Java Web程序设计任务教程第2版课后题答案

- 个人开发常用的eslint规则,适用vue、react

- VMvare虚拟机之文件夹共享&防火墙设置

- MATLAB读取图片并转换为二进制数据格式

- 【Java进阶篇】深拷贝和浅拷贝的理解(保姆级文献)