Verilog HDL数据类型

发布时间:2023年12月18日

1 网络型(net型)数据

????????两种驱动方式:在结构描述中将其连接到一个门元件或模块的输出端;或用assign语句对其赋值。

????????【例】分别调用Verilog HDL提供的门元件和采用assign语句设计一个二输入与非门 ? ? ?????????input?? ?a,b; ? ? ?

????????output?? ?y; ? ? ?

????????wire ? ? y; ? ? ?

????????nand?? ?my_nand(y,a,b); ? ?//调用门元件nand ? ? ?

????????assign?? ?y=!(a&&b); ?//或采用assign语句 ? ? ?

????????常用的net型数据

????????wire,tri:连线类型,可综合

????????wor,trior:具有线或特性的多重驱动连线

????????wand,triand:具有线与特性的多重驱动连线

????????tri1,tri0:上拉电阻和下拉电阻

????????supply1,supply0:电源(逻辑1)和地(逻辑0),可综合

????????trireg:具有电荷保持作用的连线,可用于电容的建模

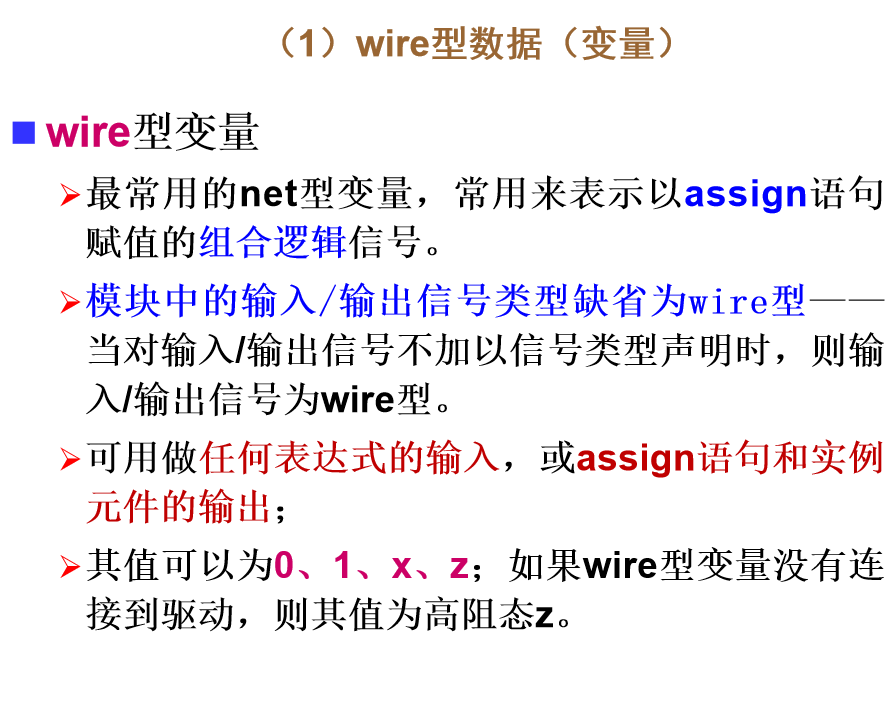

? ? ? ? (1)wire型数据(变量)

????????

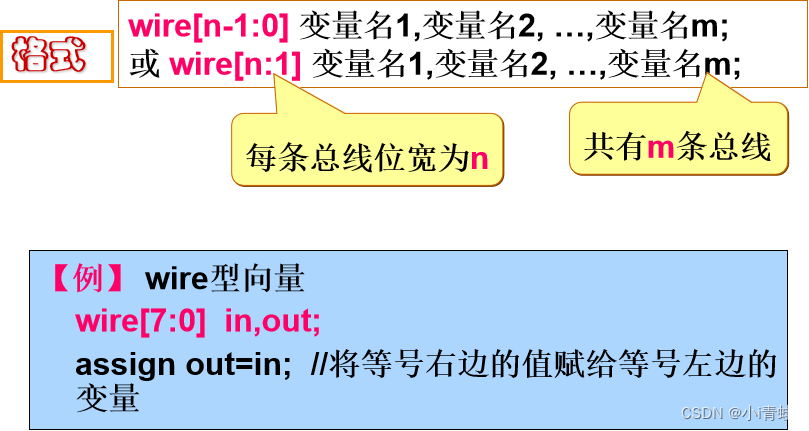

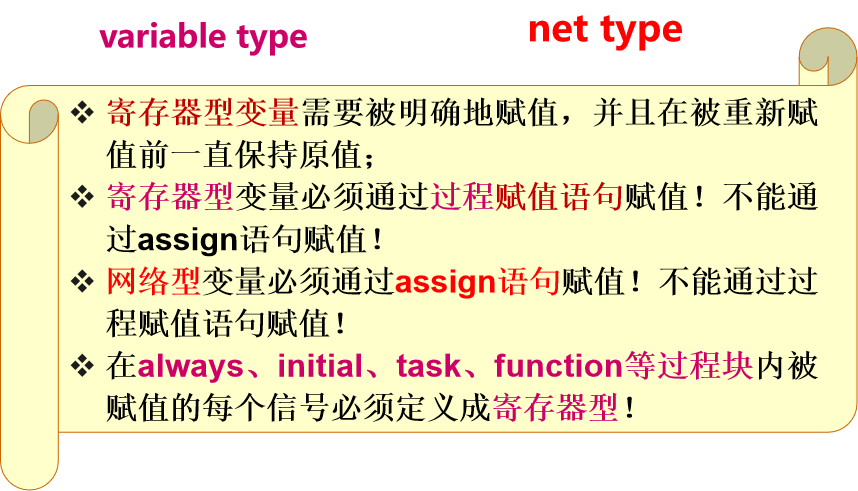

2 寄存器型

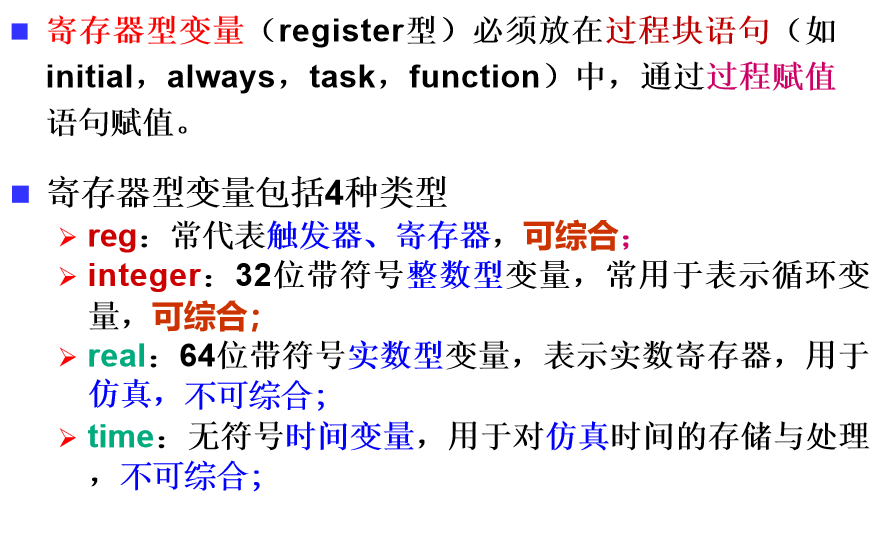

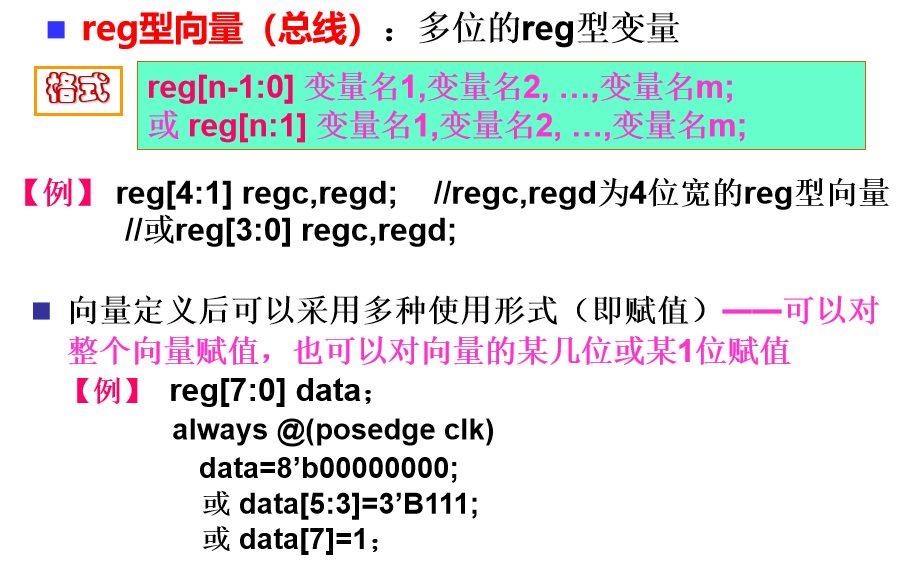

????????(1)reg型变量

????????reg型变量是最常用的寄存器型变量,常用于具体的硬件描述。是数字系统中存储元件的抽象,或者是普通的连线 。

????????(2)interger型变量

?

?

文章来源:https://blog.csdn.net/axxdxzz/article/details/134970800

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Vue3学习与实践

- C++学习笔记——友元、嵌套类、异常

- iview表格固定列横向滚动条无法拖动问题

- Clickhouse SQL字符串相关

- Wpf 使用 Prism 实战开发Day10

- Linux 强大的网络命令:nc命令操作方法

- Android Studio 分别运行flutter 的debug和release版本

- 高性能CMOS模拟多路复用器(DG408DQ-T1-E3)

- Spring5深入浅出篇:Spring与工厂设计模式简介

- Django开发3