Demystifying CXL Memory with Genuine CXL-Ready Systems and Devices——论文阅读

MICRO 2023 Paper?CXL论文阅读汇总

问题

对更大容量和更高带宽的内存的不断增长的需求推动了基于Compute eXpress Link(CXL)的内存扩展和分离技术的创新。特别是,基于CXL的内存扩展技术不仅能够经济地扩展内存容量和带宽,还能够将内存技术从特定的CPU内存接口解耦出来。由于CXL内存设备尚未广泛推出,大多数研究使用位于远程NUMA节点中的DDR内存进行模拟。

背景

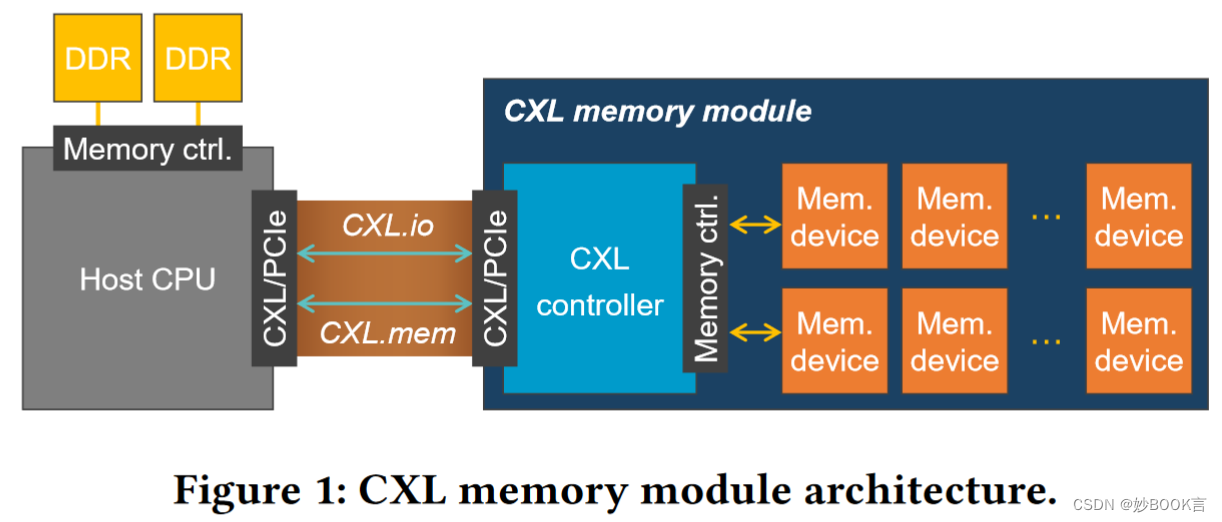

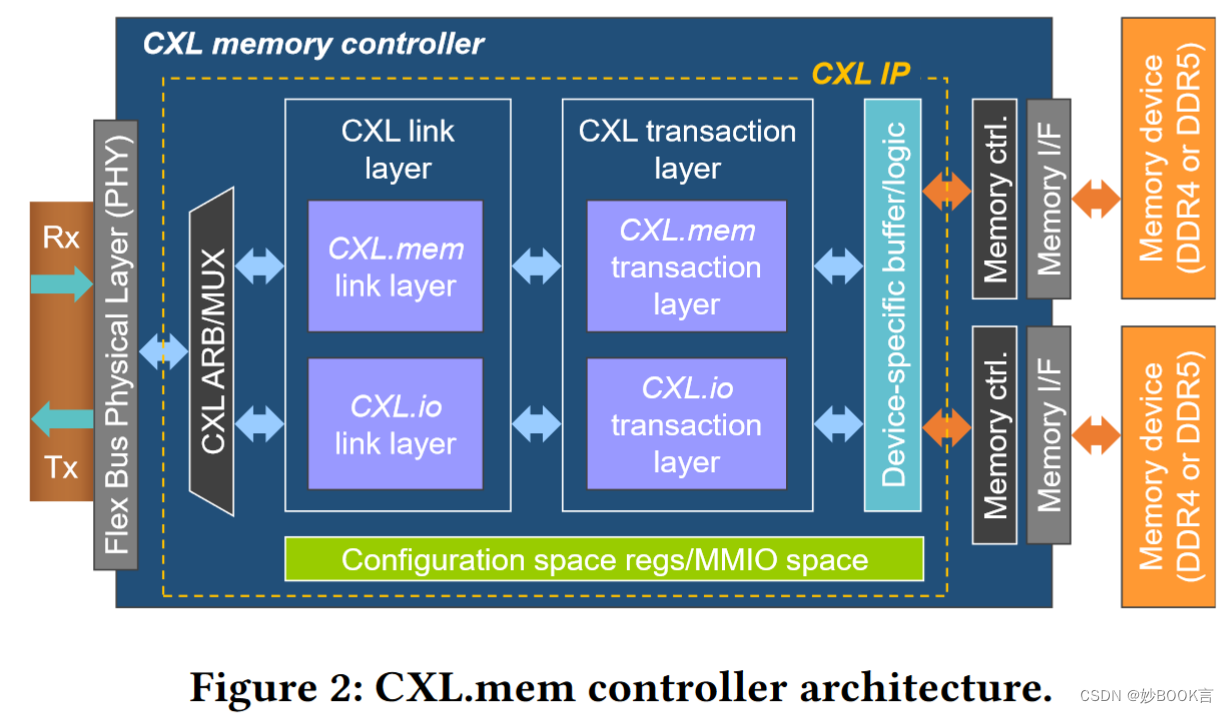

CXL[73]已经成为最有前景的内存接口技术之一。CXL是主要硬件制造商和超大规模计算供应商的联合努力开发的开放标准。由于CXL建立在标准PCIe上,而PCIe是一种串行接口技术,因此它可以提供每个引脚更高的比特传输速率(例如,PCIe 4.0:16 Gbps/lane vs. DDR4-3200:3.2 Gbps/pin),并且每比特传输的能量消耗更低(例如,PCIe 4.0:6 pJ/bit [75] vs. DDR4:22 pJ/bit [56]),但代价是更长的链路延迟(例如,PCIe 4.0:~40 ns [73] vs. DDR4:<1 ns [15])。与PCIe相比,CXL实现了额外的功能,使CPU能够使用加载/存储指令,以缓存一致的方式与设备及其连接的内存进行通信。基于PCIe 5.0 ×8的CXL内存设备消耗的引脚数比DDR5少约3倍,可以以经济的方式扩展系统的内存容量和带宽。通过在CPU和内存设备之间使用CXL控制器,CXL将内存技术与CPU支持的特定内存接口技术解耦,这为内存制造商提供了设计和优化其内存设备的灵活性。通过使用重新定时器和交换机,具有CXL支持的CPU可以以比传统网络接口技术(如RDMA)更低的延迟访问远程节点中的内存,有效促进了内存分离。这些优势使内存相关的扩展成为CXL的主要目标用例之一[25, 32, 65, 67],并且主要硬件制造商已经在其产品路线图中宣布了对CXL的支持[4, 25, 35, 65, 67]。

本文方法

我们全面评估了基于最新的第四代Intel Xeon CPU和来自不同制造商的三个CXL内存设备的真实的CXL系统。得到三个结论:

-

CXL内存 ≠ 远程NUMA内存。

-

根据CXL控制器的设计和内存技术,真实的CXL内存设备提供了不同的内存访问延迟和带宽值。

-

真实的CXL内存可以比模拟的CXL内存提供高达26%的较低延迟和3-66%的更高带宽效率,这取决于内存访问指令类型和CXL内存设备。

-

子NUMA聚类(SNC)模式将SNC节点内的CPU核心指向将其L2缓存行,从本地内存独占地驱逐到同一SNC节点内的LLC切片,为SNC节点提供LLC隔离。然而,当CPU核心访问CXL内存时,会破坏LLC隔离,因为来自CXL内存的L2缓存行可以被驱逐到任何SNC节点内的LLC切片。因此,访问CXL内存比访问本地DDR内存从LLC容量中收益大2-4,特别是对于对缓存友好的应用程序,明显弥补了访问CXL内存的较长延迟。

-

-

天真地使用CXL内存是有害的。

-

对于微秒级延迟的简单应用程序(例如键值存储),对内存访问延迟非常敏感。将页面分配给CXL内存会使这些应用程序的尾延迟比本地DDR内存增加10-82%。针对分层内存系统的最新CXL内存感知页面放置策略[64]实际上会进一步增加尾延迟,与在DDR内存和CXL内存之间静态分配页面相比。这是由于页面迁移的开销。

-

对于毫秒级延迟的复杂应用程序(例如社交网络微服务),即使大多数页面分配给CXL内存,尾延迟也只会略微增加。这是因为访问CXL内存的较长延迟对这类应用程序的端到端延迟贡献较小。

-

对于内存带宽密集型应用程序,根据默认操作系统策略天真地将50%的页面分配给CXL内存可能导致较低的吞吐量,尽管使用DDR内存和CXL内存可以提供更高的总体带宽。

-

-

CXL内存感知动态页面分配策略

-

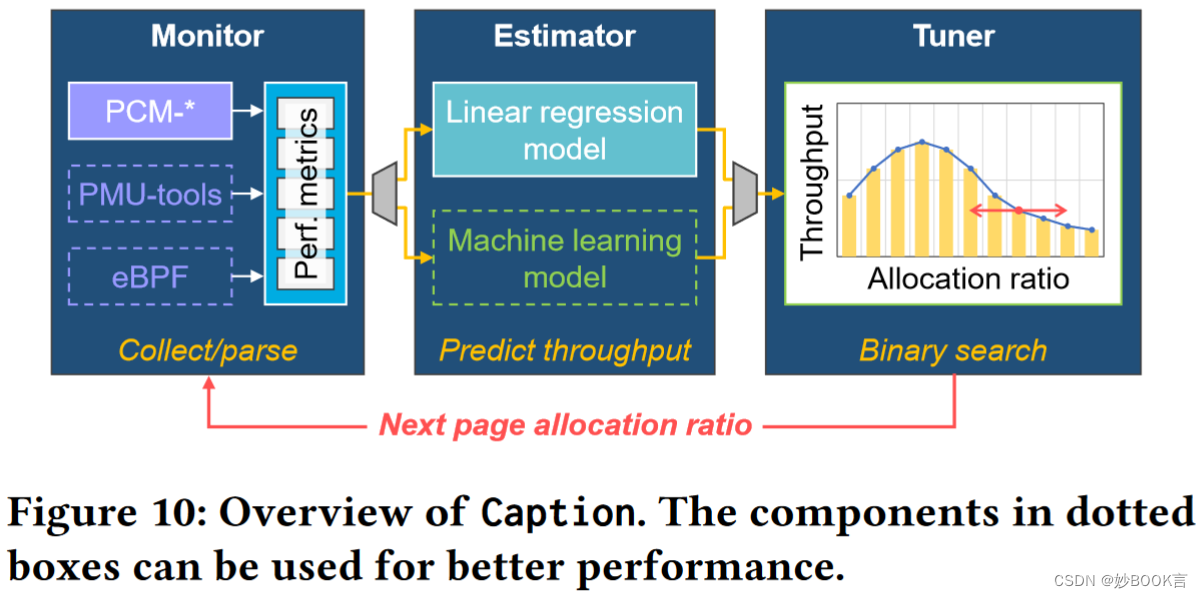

提出了Caption,面向操作系统的CXL内存感知的动态页面分配策略。Caption首先确定制造商特定的CXL内存设备的带宽。随后,Caption定期监视各种CPU计数器,如(共同运行的)应用程序经历的内存访问延迟,并在运行时评估它们所消耗的带宽。最后,基于监视的CPU计数器值,Caption估算一段时间内的内存子系统性能。当某个应用程序需要分配新页面时,Caption考虑了内存子系统性能的历史记录以及过去分配给CXL内存的页面百分比。使用简单的贪婪算法调整分配给CXL内存的页面的百分比,以提高整个系统的吞吐量。

-

评估结果显示,与操作系统默认的静态页面分配策略相比,Caption提高了共运行一组内存带宽密集型SPEC CPU2017基准测试的系统吞吐量24%。

-

实验环境

系统和设备

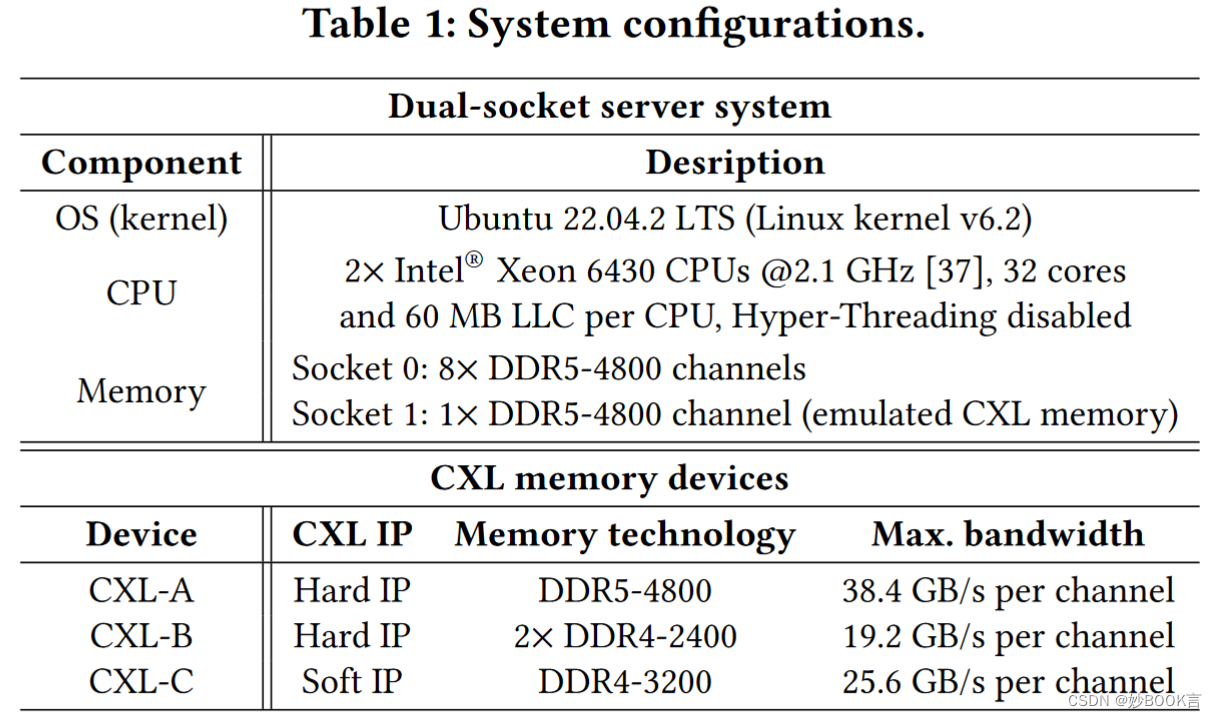

系统。我们使用一台服务器评估支持CXL内存的最新商用硬件(表1)。该服务器包含两个英特尔Sapphire Rapids(SPR)CPU插槽。一个插槽中填充了八个4800 MT/s DDR5 DRAM DIMM(128 GB),分布在八个内存通道上。另一个插槽中只填充了一个4800 MT/s DDR5 DRAM DIMM,以模拟CXL内存的带宽和容量。Intel SPR CPU集成了四个CPU芯片组,每个芯片组最多有15个核心和两个DDR5 DRAM通道。用户可以选择将4个芯片组作为统一的CPU,或将每个芯片组(或两个芯片组)作为SNC模式下的NUMA节点。这种灵活性是为了让用户在应用程序之间实现LLC等共享资源的强隔离。我们关闭超线程功能,并将CPU核心时钟频率设置为2.1 GHz,以获得更可预测的性能。

CXL内存设备。我们使用了三种CXL内存设备(表1),每种都具有不同的CXL IP(基于ASIC的硬IP和基于FPGA的软IP)和DRAM技术(DDR5-4800、DDR4-2400和DDR4-3200)。由于CXL协议本身并未规定底层内存技术,因此它可以无缝透明地适应DRAM、持久内存、闪存[72]和其他新兴内存技术。因此,不同的CXL内存设备可能表现出不同的延迟和带宽特性。

微基准测试

为了表征CXL内存的性能,我们使用了两个微基准测试。首先,我们使用Intel Memory Latency Checker(MLC)[42],这是一个用于测量各种使用场景下内存延迟和带宽的工具。其次,我们使用了一个名为memo(测量内存子系统效率)的微基准测试。它与Intel MLC有一些相似之处,但我们开发它以更灵活地表征不同方式的内存子系统性能。例如,它可以测量特定内存访问指令的延迟和带宽(例如AVX-512非时序加载和存储指令)。

基准测试

延迟敏感应用

Redis [69],一个流行的高性能内存键值存储,使用YCSB [19]进行测试。我们使用均匀分布的键,确保最大程度地对内存子系统施加压力,除非我们明确指定使用其他分布。

DeathStarBench(DSB)[28],用于评估微服务性能的开源基准套件。它使用Docker启动微服务的组件,包括机器学习(ML)推理逻辑、Web后端、负载均衡器、缓存和存储。我们评估了三个DSB工作负载:(1)发布帖子,(2)读取用户时间轴,(3)混合工作负载(10%的发布帖子,30%的读取用户时间轴和60%的读取主页时间轴),作为社交网络框架。

FIO [7],用于对存储设备和文件系统进行基准测试的开源工具,以评估在OS页面缓存中使用CXL内存的延迟影响。页面缓存由标准的Linux存储子系统支持,它将最近访问的存储数据(例如文件)保存在未使用的主内存空间中,以减少对慢速存储设备的访问次数。

吞吐量应用

使用与MERCI [58]相同的设置运行基于深度学习推荐模型(DLRM)的推理应用。已知DLRM推理中的嵌入缩减步骤具有较大的内存占用,并且占推理延迟的50-70% [58]。

SPECrate CPU2017基准套件 [13],这是常用于评估数据中心系统吞吐量的基准。

我们评估每个基准的每千条指令的缺失(MPKI),并运行具有最高MPKI的四个基准:(1)fotonik3d,(2)mcf,(3)roms和(4)cactuBSSN。我们运行单个基准的多个实例或两个不同的基准。

内存延迟和带宽特性

我们首先评估访问不同内存设备的延迟和带宽:基于远程NUMA节点(DDR5-R)中的DDR5内存的模拟CXL内存设备,以及三个真正的CXL存储设备(CXL-A、CXL-B和CXL-C)。我们进行此评估是为了了解不同内存访问指令类型的各种CXL内存设备的性能特征。接下来,我们将研究Intel SPR CPU的缓存层次结构与CXL内存设备之间的相互作用。

延迟

-

全双工的 CXL 和 UPI 接口降低了内存访问延迟。

-

访问真实的 CXL 内存设备的延迟高度依赖于特定的 CXL 控制器设计。

-

模拟的 CXL 内存可能比真实的 CXL 内存具有更长的内存访问延迟。

带宽

-

带宽强烈依赖于 CXL 控制器的效率。

-

与模拟的 CXL 内存相比,真实的 CXL 内存对于存储操作能够提供具有竞争力的带宽效率。

与缓存层次结构的交互

-

与本地DDR内存相比,CXL内存与CPU的缓存层次结构的交互方式有所不同。

使用CXL内存对应用程序性能的影响

延迟

-

对𝜇s级延迟敏感的内存密集型应用,将页面分配给CXL内存,会显著增加p99延迟。

-

即使使用智能的页面迁移策略,也可能会进一步增加这些对延迟敏感的应用的p99延迟,因为迁移页面的开销。

-

对𝑚s级延迟敏感的复杂应用,将页面分配给CXL内存,不会显著增加p99延迟。因为访问CXL内存的延迟在这类应用的端到端延迟中的贡献是相对较小的,并且在对CXL内存的访问之间通过中间操作进行了摊销。

吞吐

-

对于内存带宽密集型应用,根据操作系统默认策略将50%的页面分配给CXL内存,可能导致比将100%的页面分配给DDR内存时更低的吞吐量,即使使用DDR内存和CXL内存的总带宽更高。

CXL内存感知的动态页面分配策略

分3个模块:

-

周期性的监控与内存子系统性能相关的CPU计数器。

-

基于监控估算系统吞吐量。

-

调整分配给CXL内存的页面百分比。

总结

使用CXL模拟器和真实CXL硬件,比较其性能。发现不同CXL控制器的设计会显著影响延迟的带宽,使用模拟器相对来说延迟更高带宽更小;使用CXL内存时使用页面迁移策略,需要考虑迁移带来的开销,否则会带来负优化;使用CXL内存会增加延迟,对𝜇s级延迟敏感的内存密集型应用,会显著增加p99延迟,对𝑚s级延迟敏感的复杂应用,增加的延迟可忽略不计;使用CXL内存会增加总带宽,但数据分布不合理时,带宽反而下降,需要有效的设计算法来优化吞吐和带宽。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Navisworks各版本安装指南

- 基于VUE框架的旅游平台-随心-计算机毕业设计源码82070

- leetcode:2717. 半有序排列(python3解法)

- 视频编辑与制作,视频尺寸修改器

- lodash源码分析每日一练 - 数组 - fromPairs

- 在Spring Cloud中使用Gateway 网关

- 网络安全专家常用的12个操作系统

- 基于 Spring Boot+MySQL实现的在线考试系统源码+数据库,基于不同类型的客观题,进行自动组卷、批卷等功能的考试系统

- 完美调试android-goldfish(linux kernel) aarch64的方法

- Linux 第三章:实验案例:MySQL服务器的构建与维护