[Verilog] Verilog 操作符与表达式

主页: 元存储博客

前言

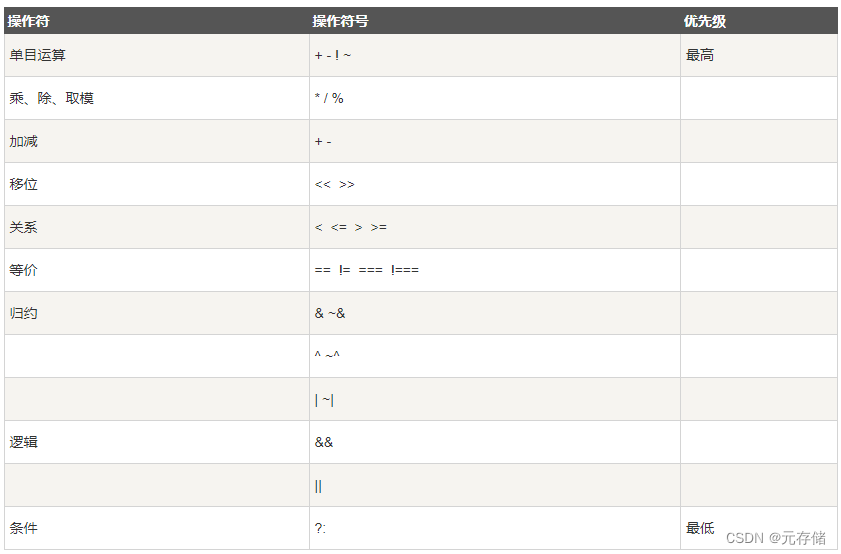

1. 操作符

图片来源: https://www.runoob.com/

Verilog语言中使用的操作符包括:

-

算术操作符:加法(+)、减法(-)、乘法(*)、除法(/)、取模(%)、自增(++)、自减(–)等。

-

逻辑操作符:与(&)、或(|)、非(!)、异或()、与非(~&)、或非(~|)、异或非(~)等。

-

位操作操作符:按位与(&)、按位或(|)、按位异或(^)、按位非(~)、左移(<<)、右移(>>)等。

-

关系操作符:等于(==)、不等于(!=)、大于(>)、小于(<)、大于等于(>=)、小于等于(<=)等。

-

条件操作符:三目运算符(?😃。

-

赋值操作符:赋值(=)、加等(+=)、减等(-=)、乘等(*=)、除等(/=)、模等(%=)、与等(&=)、或等(|=)、异或等(^=)、左移等(<<=)、右移等(>>=)等。

结构化操作符:括号(())、方括号([])、点号(.)等。

- 归约操作符 [文献1]

归约操作符包括:归约与(&),归约与非(&),归约或(|),归约或非(|),归约异或(),归约同或(~)。

归约操作符只有一个操作数,它对这个向量操作数逐位进行操作,最终产生一个 1bit 结果。

逻辑操作符、按位操作符和归约操作符都使用相同的符号表示,因此有时候容易混淆。区分这些操作符的关键是分清操作数的数目,和计算结果的规则。

A = 4'b1010 ;

&A ; //结果为 1 & 0 & 1 & 0 = 1'b0,可用来判断变量A是否全1

~|A ; //结果为 ~(1 | 0 | 1 | 0) = 1'b0, 可用来判断变量A是否为全0

^A ; //结果为 1 ^ 0 ^ 1 ^ 0 = 1'b0

**位宽操作符([])

等号(=)操作符:用于将一个位宽较小的信号赋值给一个位宽较大的信号

reg [7:0] a;

reg [3:0] b;

assign a = b;

将位宽为4位的信号b赋值给位宽为8位的信号a。Verilog会自动将b的值复制到a的低4位上。

等号(=)操作符加括号:用于将一个位宽较大的信号赋值给一个位宽较小的信号,并执行截断操作。例如:

reg [7:0] a;

reg [3:0] b;

assign b = a[3:0];

上面将位宽为8位的信号a的低4位赋值给位宽为4位的信号b。Verilog会自动对a的低4位进行截断

重复操作符({})**

用于复制一个信号的多个副本

reg [3:0] a;

reg [7:0] b;

assign b = {4{a}};

拼接操作符({})

拼接操作符用大括号 {,} 来表示,用于将多个操作数(向量)拼接成新的操作数(向量),信号间用逗号隔开。

拼接符操作数必须指定位宽,常数的话也需要指定位宽。例如:

实例

A = 4'b1010 ;

B = 1'b1 ;

Y1 = {B, A[3:2], A[0], 4'h3 }; //结果为Y1='b1100_0011

Y2 = {4{B}, 3'd4}; //结果为 Y2=7'b111_1100

Y3 = {32{1'b0}}; //结果为 Y3=32h0,常用作寄存器初始化时匹配位宽的赋初值

2. 操作数

位操作数:表示单个位的值,可以是0或1。

寄存器操作数:表示存储在寄存器中的值。

端口操作数:表示输入/输出端口的值。

参数操作数:表示参数值。

固定操作数:表示常量值,如整数、浮点数或字符串。

立即操作数:表示在运行时计算得到的值。

3 表达式

表达式由操作符和操作数构成,其目的是根据操作符的意义得到一个计算结果。

常见的Verilog表达式:

-

算术运算符:使用"+“、”-“、”*“、”/"等运算符执行加法、减法、乘法和除法操作。例如:a = b + c;

-

逻辑运算符:使用"&&“、”||“、”!"等运算符执行与、或和非逻辑操作。例如:y = a && b;

-

比较运算符:使用"==“、”!=“、”>“、”<"等运算符执行比较操作。例如:is_equal = a == b;

-

位运算符:使用"&“、”|“、”~"等运算符执行位操作。例如:result = a & b;

-

移位运算符:使用">>“、”<<"等运算符执行位移操作。例如:result = a >> 2;

-

条件运算符:使用"?“和”:"运算符执行条件操作。例如:result = (a > b) ? a : b;

-

乘方运算符:使用"**"运算符计算乘方。例如:result = a ** 2;

-

括号:使用括号将表达式进行分组。例如:result = (a + b) * c;

总结

参考文献

- https://www.runoob.com/w3cnote/verilog-expression.html

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 解锁新角色:售前方案工程师 - 女性程序员的新挑战与机遇

- VSCode 安装 Copilot 详细过程和实例

- Javascript 地狱级的if else / switch case该如何优化?

- 大津法(OTSU)点云强度信息分割

- 推荐三个非常好用的视频转文字工具

- MDBootstrap Joins ComponentSource

- git merge和git rebase区别

- Spring Boot 和 Spring 有什么区别

- 基于YOLOv7算法的高精度实时行人打电话检测系统(PyTorch+Pyside6+YOLOv7)

- springboot定时器注解和cron表达式如何使用