petalinux

基于网络参考,运行一个xilinx pcie rc的参考,选择vcu118平台(基于microblaze):该参考通过pcie rc对挂在的外部ssd进行读写测试

Zynq PCI Express Root Complex design in Vivado - FPGA Developer

1,安装的是2022.1版本

下载地址:PetaLinux Tools

只能使用普通用户安装(使用的ubuntu)

sudo apt-get -y install gcc-multilib

sudo apt-get install zlib1g:i386

./petalinux-v2022.1-04191534-installer.run --dir ~/petalinux/v2022.1 --platform "microblaze"

#将目录/opt 及其下面的所有文件、子目录的文件主改成 usera

#chown -R usera:usera /opt

#cat /proc/version

#Linux version 5.4.0-135-generic (buildd@lcy02-amd64-053) (gcc version 7.5.0 (Ubuntu 7.5.0-3ubuntu1~18.04)) #152~18.04.2-Ubuntu SMP Tue Nov 29 08:23:49 UTC 2022

##

apt-get install -y flex bison build-essential libssh-dev gcc git make net-tools libncurses5-dev tftpd zlib1g-dev libssl-dev bison libselinux1 gnupg wget diffstat chrpath socat xterm autoconf libtool tar unzip texinfo zlib1g-dev gcc-multilib zlib1g:i386 screen pax gzip gawkAMD Adaptive Computing Documentation Portal

注意microblaze只能使用32bit

2,编译内核

source /<your-petalinux-install-dir>/settings.sh

petalinux-create --type project --template microblaze --name petalinux_prj

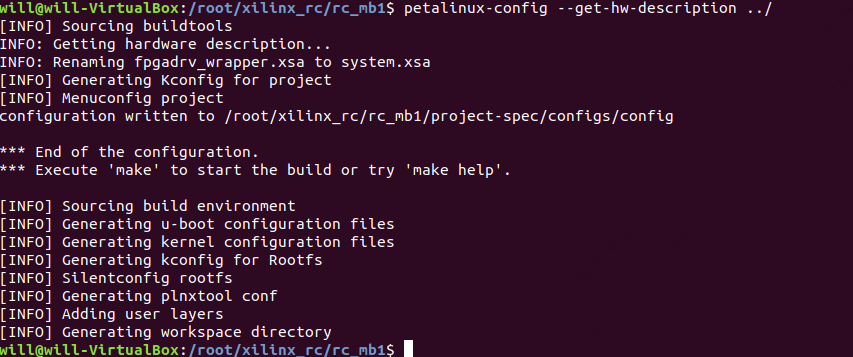

petalinux-config --get-hw-description ../kc705_aximm_pcie/kc705_aximm_pcie.sdk/不做修改直接exit & save:

配置linux内核,使能PCI相关库

petalinux-config -c kernel

#

Enable: Bus options->PCI support

Enable: Bus options->PCI support->Message Signaled Interrupts (MSI and MSI-X)

Enable: Bus options->PCI support->Enable PCI resource re-allocation detection

Enable: Bus options->PCI support->PCI host controller drivers->Xilinx AXI PCIe host bridge support

Enable: Device Drivers->Block devices->NVM Express block device这条命令需要很多在线文件,执行时间较长:

配置根文件系统,即应用程序

petalinux-config -c rootfs

#

Enable PCI utils (for lspci): Filesystem Packages->console/utils->pciutils->pciutils

Enable required packages for lsblk, fdisk, mkfs, blkid:

Filesystem Packages->base->util-linux->util-linux

Filesystem Packages->base->util-linux->util-linux-blkid

Filesystem Packages->base->util-linux->util-linux-fdisk

Filesystem Packages->base->util-linux->util-linux-mkfs

Filesystem Packages->base->util-linux->util-linux-mount

Filesystem Packages->base->e2fsprogs->e2fsprogs

Filesystem Packages->base->e2fsprogs->e2fsprogs-mke2fs

编译系统:时间也较长

petalinux-buildpcie dts信息:

默认生成的设备树路径

components/plnx_workspace/device-tree/device-tree

修改:

1、将 system-user.dtsi复制到\components\plnx_workspace\device-tree\ 目录下

2、执行petalinux-build -c device-tree -x cleansstate清理设备树编译状态

3、执行petalinux-build -c device-tree编译设备树https://www.cnblogs.com/YYFaGe/p/14453608.html

dts的基本信息:

https://www.cnblogs.com/fortunely/p/16405592.html

designware pcie dts:

Linux Kernel Documentation / devicetree / bindings / pci / designware-pcie.txt

Release v0.4 · devicetree-org/devicetree-specification · GitHub

示例:

/include/ "system-conf.dtsi"

/ { pcie: pcie@40000000 {

compatible = "snps,dw-pcie";

reg = <0x40000000 0x0001000>, /* IP registers */

<0x40000000 0x0002000>; /* Configuration space */

reg-names = "dbi", "config";

#address-cells = <3>;

#size-cells = <2>;

device_type = "pci";

ranges = <0x81000000 0 0x00000000 0x50000000 0 0x00010000

0x82000000 0 0x51000000 0x51000000 0 0x08000000>;

interrupts = <25>, <24>;

#interrupt-cells = <1>;

num-lanes = <1>;

};

pcie: pcie@40000000 {

compatible = "snps,dw-pcie";

reg = <0x40000000 0x04000>, //PCIE控制器基地址

<0x01f00000 0x80000>; //PCIE配置空间基地址

reg-names = "dbi", "config";

#address-cells = <3>;

#size-cells = <2>;

device_type = "pci";

bus-range = <0x00 0xff>;

ranges = <0x81000000 0 0 0x01f80000 0 0x00010000 /* downstream I/O */ //BAR空间地址

0x82000000 0 0x01000000 0x01000000 0 0x00f00000>; /* non-prefetchable memory */ //BAR空间地址

num-lanes = <1>;

interrupts = <GIC_SPI 120 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "msi";

#interrupt-cells = <1>;

interrupt-map-mask = <0 0 0 0x7>;

interrupt-map = <0 0 0 1 &gpc GIC_SPI 123 IRQ_TYPE_LEVEL_HIGH>,

<0 0 0 2 &gpc GIC_SPI 122 IRQ_TYPE_LEVEL_HIGH>,

<0 0 0 3 &gpc GIC_SPI 121 IRQ_TYPE_LEVEL_HIGH>,

<0 0 0 4 &gpc GIC_SPI 120 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX6QDL_CLK_PCIE_AXI>,

<&clks IMX6QDL_CLK_LVDS1_GATE>,

<&clks IMX6QDL_CLK_PCIE_REF_125M>;

clock-names = "pcie", "pcie_bus", "pcie_phy";

status = "disabled";

};

};

//

Zynq:

pci_express: axi-pcie@50000000 {

#address-cells = <3>;

#size-cells = <2>;

#interrupt-cells = <1>;

compatible = "xlnx,axi-pcie-host-1.00.a";

reg = < 0x50000000 0x1000000 >;

device_type = "pci";

interrupts = < 0 52 4 >;

interrupt-map-mask = <0 0 0 7>;

interrupt-map = <0 0 0 1 &pcie_intc 1>,

<0 0 0 2 &pcie_intc 2>,

<0 0 0 3 &pcie_intc 3>,

<0 0 0 4 &pcie_intc 4>;

ranges = < 0x02000000 0 0x60000000 0x60000000 0 0x10000000 >;

pcie_intc: interrupt-controller {

interrupt-controller;

#address-cells = <0>;

#interrupt-cells = <1>;

};

};

//

pcie2x1: pcie@fe260000 {

compatible = "rockchip,rk3568-pcie", "snps,dw-pcie";

reg = <0x3 0xc0000000 0x0 0x400000>,

<0x0 0xfe260000 0x0 0x10000>;

reg-names = "pcie-dbi", "pcie-apb";

interrupts = <GIC_SPI 75 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 74 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 73 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 72 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 71 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "sys", "pmc", "msg", "legacy", "err";

bus-range = <0x0 0xf>;

clocks = <&cru ACLK_PCIE20_MST>, <&cru ACLK_PCIE20_SLV>,

<&cru ACLK_PCIE20_DBI>, <&cru PCLK_PCIE20>,

<&cru CLK_PCIE20_AUX_NDFT>;

clock-names = "aclk_mst", "aclk_slv",

"aclk_dbi", "pclk", "aux";

device_type = "pci";

linux,pci-domain = <0>;

num-ib-windows = <6>;

num-ob-windows = <2>;

max-link-speed = <2>;

msi-map = <0x0 &its 0x0 0x1000>;

num-lanes = <1>;

phys = <&combphy2_psq PHY_TYPE_PCIE>;

phy-names = "pcie-phy";

power-domains = <&power RK3568_PD_PIPE>;

ranges = <0x00000800 0x0 0x00000000 0x3 0x00000000 0x0 0x800000

0x81000000 0x0 0x00800000 0x3 0x00800000 0x0 0x100000

0x83000000 0x0 0x00900000 0x3 0x00900000 0x0 0x3f700000>;

resets = <&cru SRST_PCIE20_POWERUP>;

reset-names = "pipe";

#address-cells = <3>;

#size-cells = <2>;

status = "disabled";

};

pcie3x1: pcie@fe270000 {

compatible = "rockchip,rk3568-pcie", "snps,dw-pcie";

reg = <0x3 0xc0400000 0x0 0x400000>,

<0x0 0xfe270000 0x0 0x10000>;

reg-names = "pcie-dbi", "pcie-apb";

interrupts = <GIC_SPI 160 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 159 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 158 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 157 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 156 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "sys", "pmc", "msg", "legacy", "err";

bus-range = <0x10 0x1f>;

clocks = <&cru ACLK_PCIE30X1_MST>, <&cru ACLK_PCIE30X1_SLV>,

<&cru ACLK_PCIE30X1_DBI>, <&cru PCLK_PCIE30X1>,

<&cru CLK_PCIE30X1_AUX_NDFT>;

clock-names = "aclk_mst", "aclk_slv",

"aclk_dbi", "pclk", "aux";

device_type = "pci";

linux,pci-domain = <1>;

num-ib-windows = <6>;

num-ob-windows = <2>;

max-link-speed = <3>;

msi-map = <0x1000 &its 0x1000 0x1000>;

num-lanes = <1>;

phys = <&pcie30phy>;

phy-names = "pcie-phy";

power-domains = <&power RK3568_PD_PIPE>;

ranges = <0x00000800 0x0 0x40000000 0x3 0x40000000 0x0 0x800000

0x81000000 0x0 0x40800000 0x3 0x40800000 0x0 0x100000

0x83000000 0x0 0x40900000 0x3 0x40900000 0x0 0x3f700000>;

resets = <&cru SRST_PCIE30X1_POWERUP>;

reset-names = "pipe";

#address-cells = <3>;

#size-cells = <2>;

status = "disabled";

};

pcie3x2: pcie@fe280000 {

compatible = "rockchip,rk3568-pcie", "snps,dw-pcie";

reg = <0x3 0xc0800000 0x0 0x400000>,

<0x0 0xfe280000 0x0 0x10000>;

reg-names = "pcie-dbi", "pcie-apb";

interrupts = <GIC_SPI 165 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 164 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 163 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 162 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 161 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "sys", "pmc", "msg", "legacy", "err";

bus-range = <0x20 0x2f>;

clocks = <&cru ACLK_PCIE30X2_MST>, <&cru ACLK_PCIE30X2_SLV>,

<&cru ACLK_PCIE30X2_DBI>, <&cru PCLK_PCIE30X2>,

<&cru CLK_PCIE30X2_AUX_NDFT>;

clock-names = "aclk_mst", "aclk_slv",

"aclk_dbi", "pclk", "aux";

device_type = "pci";

linux,pci-domain = <2>;

num-ib-windows = <6>;

num-ob-windows = <2>;

max-link-speed = <3>;

msi-map = <0x2000 &its 0x2000 0x1000>;

num-lanes = <2>;

phys = <&pcie30phy>;

phy-names = "pcie-phy";

power-domains = <&power RK3568_PD_PIPE>;

ranges = <0x00000800 0x0 0x80000000 0x3 0x80000000 0x0 0x800000

0x81000000 0x0 0x80800000 0x3 0x80800000 0x0 0x100000

0x83000000 0x0 0x80900000 0x3 0x80900000 0x0 0x3f700000>;

resets = <&cru SRST_PCIE30X2_POWERUP>;

reset-names = "pipe";

#address-cells = <3>;

#size-cells = <2>;

status = "disabled";

};

[v2,1/2] dt-bindings: rockchip: Add DesignWare based PCIe controller - Patchwork

3,IP核的配置说明

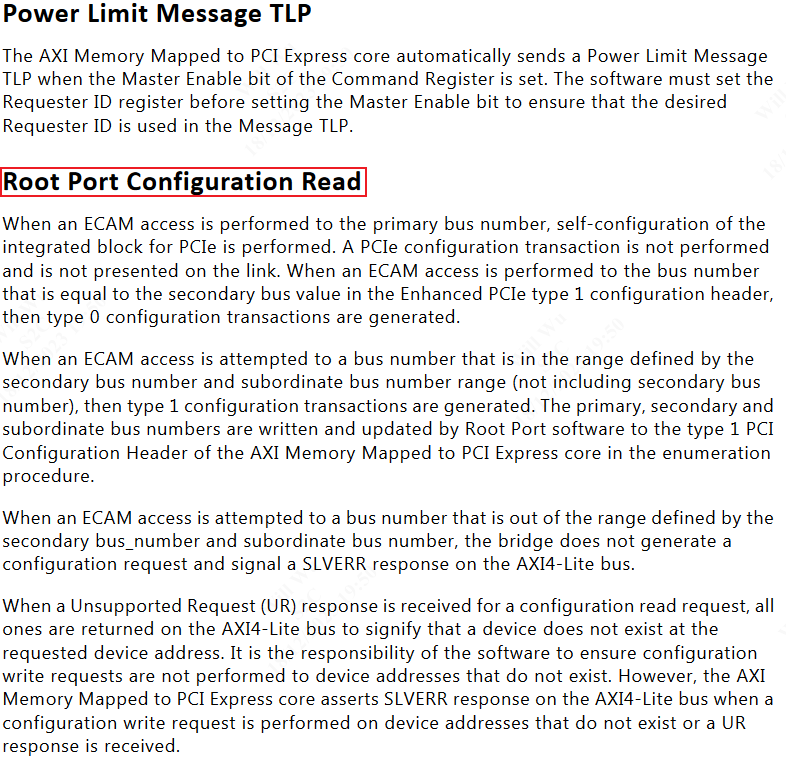

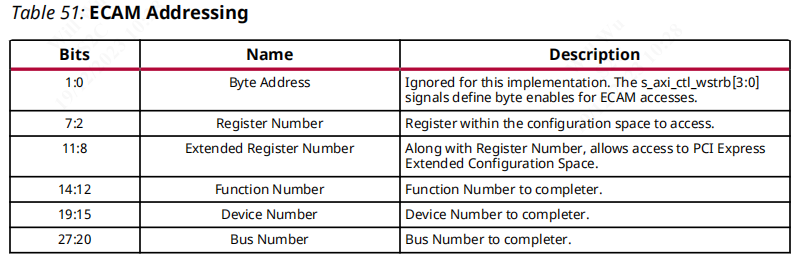

ECAM的特点是根据prim bus num/second bus num/subordinate bus num去自动选择本地、type0、或者type1的配置包。

xilinx pcie mm寄存器空间说明:ECAM通过AXI4-Lite访问

ECAM的寻址方式是Spec标准定义的:

Xilinx PCIe 驱动:

https://github.com/Xilinx/linux-xlnx/blob/master/drivers/pci/controller/pcie-xilinx.c

Xilinx PCIe Root and EndPoint - Xilinx Wiki - Confluence

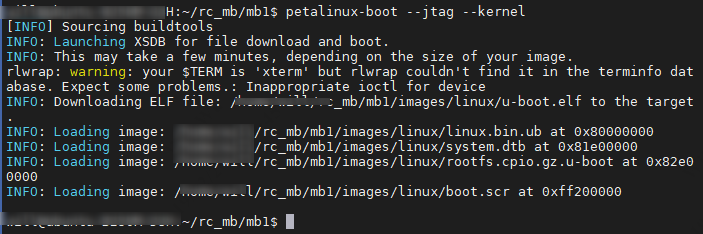

4,启动方式

Boot PetaLinux over JTAG

petalinux-boot --jtag --fpga --bitstream ../design_1_wrapper.bit

petalinux-boot --jtag --kernel

默认用户名:petalinux 密码:root

AMD Adaptive Computing Documentation Portal

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!