在芯片设计端,从事DFT岗位是什么体验?

从1975年PHILIPS公司实验中心首次提出“可测性设计”概念至今,DFT已经伴随着芯片走过了半个世纪。

但DFT在数字IC设计岗位中还是显得很神秘很低调。

你说他重要吧,并不是所有芯片设计公司都有这个岗位,你说他不重要吧,但凡芯片产品达到一定规模后,就必须设置DFT部门。

我曾见过某个大厂的HR,在各类DFT相关话题下疯狂评论招人,属实急迫。

那么成为一个DFT工程师到底是什么样的体验呢?

DFT对于芯片有多重要?

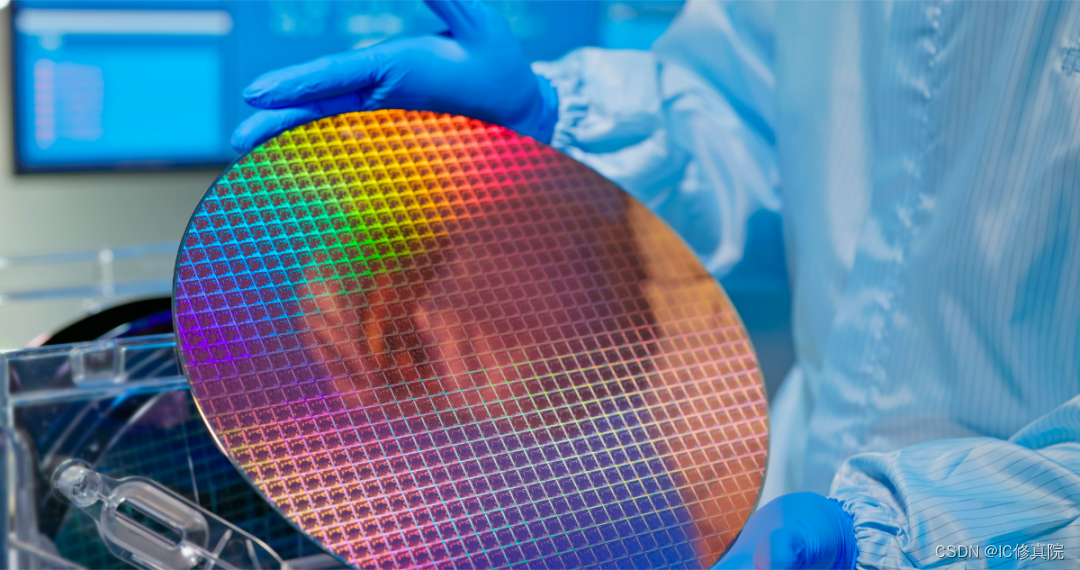

芯片制造工序非常繁杂,要经历掺杂、氧化、光刻、刻蚀等数百道工艺程序,涉及化学、物理、机械等各种加工过程,每个环节都得精益求精,甚至“吹毛求疵”。

即使如此,也很难能保证良率100%(晶圆制造、封装测试每一步都会对良率产生影响),生产过程中依然会有芯片出现缺陷。

在加工过程中,大到工艺偏差,小到粉尘颗粒,都会引入制造缺陷,使晶体管短路/断路/不能正常工作。

而DFT(可测性设计),就是在满足芯片正常功能的基础上,加入可测性逻辑,等芯片制造出来,在ATE(自动测试仪)设备上通过可测性逻辑对芯片进行测试,挑出有制造缺陷的芯片并淘汰掉,留下没有制造缺陷的好芯片。

在电路设计之初就考虑到未来测试的问题,一方面算是芯片设计者的“未雨绸缪”,另一方面也能降低芯片测试的难度、节省测试的时间和费用成本。

DFT工程师需要掌握什么?

DFT设计有一个很重要的目标,就是提升芯片的可测性、可控性和可观测性。

为了实现这个目标,在设计芯片的时候会进行一些“埋点”操作,等芯片生产出来之后,可以通过外面的端口看到内部的情况。

但实际情况并不只是在电路中增加测试点那么简单,而是需要经过系统的规划,将电路分解为输入/输出关系最少的若干模块,版图设计也以相应的模块形式设计,将各模块间最关键且数量最少的结合点作为测试点。

所以懂设计、懂电路、懂实现、懂测试是一个DFT工程师的基本功。

就岗位本身而言,DFT工程师需要掌握一些基本的知识和技能:

SCAN:扫描测试,主要是用来检测芯片制造过程中经常会出现的失效问题。

BIST:内建自测试,主要是在芯片内部产生测试码,对测试的结果进行分析。

JTAG:是指国际标准测试协议(IEEE 1149.1),主要用于芯片内部测试。

各种BIST在结构设计阶段就要开始规划了,然后在RTL编码阶段实现,同时还要在RTL功能仿真阶段还要验证其正确性;而DFT扫描链、BSD和JTAG主要在RTL综合完成之后,直接由EDA工具插入。

不仅要掌握这些技术原理,还得会用EDA工具,毕竟技术的实现还得靠EDA工具。除此之外,还要掌握perl、tcl脚本语言、Linux等IC设计通用的必备技能。

DFT日常工作内容是怎样的?

一般来说,接到项目之后,各岗位工程师要一起开会,确定DFT Spec,包括IP测试策略,Pin Sharing,HT Block划分和Clock设计等。

然后要进行DFT设计,也就是分模块在设计中插入前面所提到的电路,进行综合,接下来会是Scan Chain连接和相关电路的插入。

下来就是验证环节,用针对性的EDA工具进行电路验证。与此同时要配合后端进行物理实现,这个环节可能会根据后端的不同要求进行多次电路调整。

当网表最终物理实现后,还要用工具跑ATPG,生成测试向量并进行门级仿真验证。

还没结束,剩下最关键的一步。在芯片生产出来之后,要跟TE一起进行pattern bring-up,并协助TE完成pattern导入量产的一切调试工作。

我们可以很肯定的说DFT工程师就是设计环节中的一个多面手。

在日常工作中,DFT工程师需要多读文档、多看书籍论文,和团队中其他岗位的工程师们多聊多沟通,尽可能从前辈那里取经学习。这一点对于其他岗位也同样适用。

DFT的市场需求和前景如何?

尽管相对于设计、验证这些大火的岗位来说,DFT的市场需求量相对来说少一些。

然而,需求少也只是相对的。目前国内IC设计公司但凡是有些规模或者所做产品需要一定产量,都是急招DFT工程师的。

另一方面,国内高校目前并没有相关的专业课程,所以人才培养方面存在困境,这就让DFT工程师变得更珍贵了。

但DFT是一个越在大厂越重要的角色。前些年我们对DFT并不算重视,近些年才逐渐进入高端线,所以现在的DFT工程师极其稀缺。

一直以来,DFT技术也在不断优化进步。无论是钻研技术做技术专家,还是带团队做leader,只要入行做到资深,都能有很不错的前景。

如果你正在面临入行/转行IC的选择关口,对各方向岗位还拿捏不准,对代码不感兴趣,又不想做后端,那么不妨考虑下DFT,同样是一个可以走得很远且值得奋斗的岗位选择。

这里给大家放个入口:DFT入门了解/免费资料领取

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!