《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(10)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(9)

1.3?PCI总线的存储器读写总线事务

1.3.1 PCI总线事务的时序

PCI总线使用前文中所述的信号进行数据和配置信息的传递。为了便于理解和加深印象,在此回顾一下:

(1)地址和数据信号

在PCI地址总线中,与地址和数据有关的信号如下所示:

- AD[31:0]信号

PCI总线复用地址和数据信号。

- C/BE[3:0]#信号

在地址周期中,C/BE[3:0]#信号表示PCI总线的命令;而在数据周期中,C/BE[3:0]#引脚输出字节选通信号,其中,C/BE3#、C/BE2#、C/BE1#、C/BE0#分别与数据的字节3、2、1、0对应。

- PAR信号

AD[31:0]和C/BE[3:0]的奇偶校验信号。

(2)接口控制信号

在PCI总线中,接口控制信号的主要作用是保证数据的正常传递,并根据PCI主从设备的状态,暂停、终止或者正常完成当前总线事务,其主要信号如下:

- FRAME#信号

指示一个PCI总线事务的开始与结束。当PCI设备获得总线的使用权后,将置该信号有效(即置为低),启动PCI总线事务;当结束总线事务时,将置该信号无效(即置为高)。

- IRDY#信号

由PCI主设备(包括HOST主桥)驱动,该信号有效时,表示PCI主设备的数据已经准备完毕。如果当前PCI总线事务为写事务,表示数据已经在AD[31:0]上有效;如果为读事务,则表示PCI目标设备已经准备好接收缓冲,目标设备可以将数据发送到AD[31:0]上。

- TRDY#信号

由目标设备驱动,有效时表示目标设备已经将数据准备完毕。如果当前PCI总线事务为写事务,表示目标设备已经准备好接收缓冲,可以将AD[31:0]上的数据写入目标设备;如果为读事务,表示PCI设备需要的数据已经在AD[31:0]上有效。

该信号可以与IRDY#信号联合使用,在PCI总线事务上插入等待周期,对PCI总线上的数据传送进行控制。

- STOP#信号

该信号有效时,表示目标设备请求主设备停止当前PCI总线事务。

- IDSEL信号

PCI总线在进行配置读写总线事务时,使用该信号选择PCI目标设备。IDSEL信号与PCI设备的设备号相关,相当于PCI设备配置空间的片选信号。

- DEVSEL#信号

该信号有效时,表示PCI总线的目标设备准备好。该信号与TRDY#信号的不同之处在于,该信号有效仅表示目标设备已经完成了地址译码,而并不表示目标设备可以与主设备进行数据交换。

- LOCK#信号

PCI主设备可以使用该信号,将目标设备的某个存储器或者I/O资源锁定,以禁止其它PCI主设备访问此资源,直到锁定这个资源的主设备将其释放。

(3)仲裁信号

PCI设备使用该组信号进行总线仲裁,并获得PCI总线的使用权。这组信号由REQ#和GNT#组成。

PCI主设备使用PCI总线进行数据传递时,需要:

1)首先置REQ#有效,向PCI总线仲裁器发出总线申请;

2)当PCI总线仲裁器允许PCI主设备获得PCI总线的使用权后,将置GNT#信号为有效,并将其发送给指定的PCI主设备;

3)而PCI主设备在获得总线使用权之后,将可以置FRAME#信号为有效,与PCI从设备进行数据通信。

(4)中断请求等其它信号

- INTA~D#信号

PCI总线提供了INTA#、INTB#、INTC#和INTD#4个中断请求信号。PCI设备借助这些中断请求信号,使用电平触发方式向处理器提交中断请求。

- PERR#信号

PERR#信号有效时,表示数据传送过程中出现了奇偶校验错误(Special Cycle周期除外)。

- SERR#信号

SERR#信号有效时,表示当前处理器系统出现了三种错误可能,分别为地址奇偶校验错误、在Special Cycle周期中出现数据奇偶校验错误、系统出现其它严重错误。

- 其它信号

如果PCI总线支持64位模式,还需要提供AD[63:32]、C/BE[7:4]、REQ64、ACK64和PAR64这些信号。此外,PCI总线还有一些与JTAG、SMBCLK以及66MHz使能相关的信号。

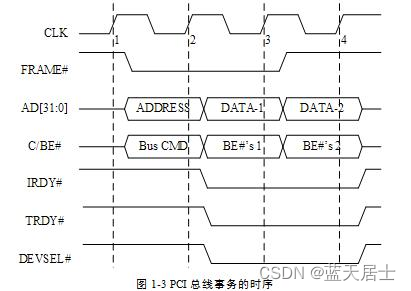

一个PCI总线事务的基本时序如下图所示:

从图中可知,与PCI总线事务相关的控制信号有FRME#、IRDY#、TRDY#、DEVSEL#等。

当一个PCI主设备需要使用PCI总线时,首先需要发送REQ#信号,通过总线仲裁获得总线使用权;当GNT#信号有效后,使用以下步骤完成一个完整PCI总线事务,对目标设备进行存储器或者I/O地址空间的读写访问。

PCI主设备使用PCI总线进行数据传递时,需要:

1)首先置REQ#有效,向PCI总线仲裁器发出总线申请;

2)当PCI总线仲裁器允许PCI主设备获得PCI总线的使用权后,将置GNT#信号为有效,并将其发送给指定的PCI主设备;

3)而PCI主设备在获得总线使用权之后,将可以置FRAME#信号为有效,与PCI从设备进行数据通信。

(1)当PCI主设备获得总线使用权后,将在CLK1的上升沿置FRAME#信号有效,启动PCI总线事务。当PCI总线事务结束后,FRAME#信号将被置为无效。

(2)PCI总线周期的第一个时钟周期(CLK1的上升沿到CLK2的上升沿之间)为地址周期。在地址周期中,PCI主设备将访问的目的地址和总线命令分别被驱动到AD[31:0]和C/BE#信号上。

- AD[31:0]信号

PCI总线复用地址和数据信号。

- C/BE[3:0]#信号

在地址周期中,C/BE[3:0]#信号表示PCI总线的命令;而在数据周期中,C/BE[3:0]#引脚输出字节选通信号,其中,C/BE3#、C/BE2#、C/BE1#、C/BE0#分别与数据的字节3、2、1、0对应。

如果当前总线命令是配置读写,那么IDSEL信号线也被置为有效,IDSEL信号与PCI总线上的AD[31:11]相连。

- IDSEL信号

PCI总线在进行配置读写总线事务时,使用该信号选择PCI目标设备。IDSEL信号与PCI设备的设备号相关,相当于PCI设备配置空间的片选信号。

(3)当IRDY#、TRDY#和DEVSEL#信号都有效后,总线事务将使用数据周期进行数据传递;当IRDY#、TRDY#信号没有同时有效时,PCI总线不能进行数据传递。PCI总线使用这两个信号进行传送控制。

- IRDY#信号

由PCI主设备(包括HOST主桥)驱动,该信号有效时,表示PCI主设备的数据已经准备完毕。如果当前PCI总线事务为写事务,表示数据已经在AD[31:0]上有效;如果为读事务,则表示PCI目标设备已经准备好接收缓冲,目标设备可以将数据发送到AD[31:0]上。

- TRDY#信号

由目标设备驱动,有效时表示目标设备已经将数据准备完毕。如果当前PCI总线事务为写事务,表示目标设备已经准备好接收缓冲,可以将AD[31:0]上的数据写入目标设备;如果为读事务,表示PCI设备需要的数据已经在AD[31:0]上有效。

(4)PCI总线支持突发周期,因此在地址周期之后可以有多个数据周期,可以传送多组数据。而目标设备并不知道突发周期的长度,如果目标设备不能继续接收数据时,可以disconnect(断连)当前总线事务。值得注意的是,只有存储器读写总线事务可以使用突发周期。

(4)STOP#信号

该信号有效时,表示目标设备请求主设备停止当前PCI总线事务。一个PCI总线事务除了可以正常结束外,目标设备还可以使用该信号终止当前PCI事务。目标设备可以根据不同的情况,要求主设备对当前PCI总线事务进行重试(Retry)、断连(Disconnect),也可以向主设备报告目标设备夭折(Target Abort)。

目标设备要求主设备Retry和Disconnect并不意味着当前PCI总线事务出现错误。当目标设备没有将数据准备好时,可以使用Retry周期使主设备重试当前的PCI总线事务。有时,当目标设备不能接收来自主设备较长的Burst操作时,可以使用Disconnect周期,将一个较长的Burst操作分解为多个Burst操作。当主设备访问的地址越界时,目标设备可以使用Disconnect周期,终止主设备的越界访问。

一个完整的PCI总线事务远比上述过程复杂得多,因为PCI总线还支持许多传送方式,如双地址周期、fast back-to-back(快速背靠背)、插入等待状态、重试和断连、总线上的错误处理等一系列总线事务。本书不一一介绍这些传送方式。

更多内容请看下回。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 小秋SLAM入门实战ROS文章汇总

- 【基础篇】四、类加载器ClassLoader

- shell编程-分支语句和循环结构

- 鸿蒙APP发布流程

- 最优化理论习题(与考试相关)

- Python从入门到网络爬虫(23个Python开源项目)

- Xcode 15 libarclite 缺失问题

- python中collections.abc.Mapping 和collections.Mapping的区别

- 电子科大软件测试~第三次作业

- James使用Mailet接收外网邮件通知提醒