米勒电容与米勒效应

米勒电容与米勒效应

米勒效应

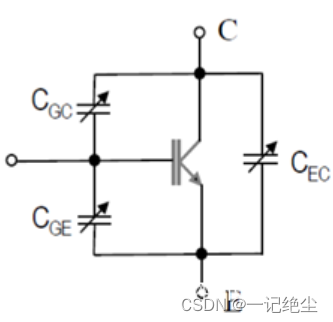

Ciss= CGE+ CGC 输入电容

Coss= CGC+ CEC 输出电容

Crss= CGC 米勒电容

下面我们以MOS中的米勒效应来展开说明:

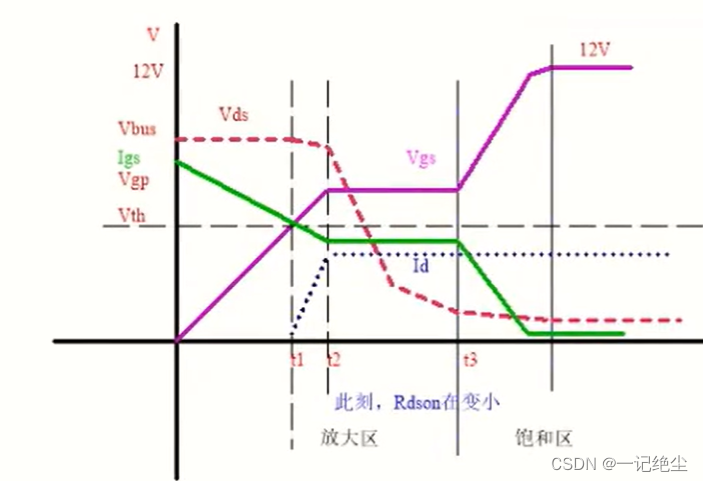

米勒效应在MOS驱动中臭名昭著,它是由MOS管的米勒电容引发的米勒效应,在MOS管开通过程中,GS电压上升到某一电压值后GS间电压会经过一段不变值的过程,过后GS间电压又开始上升直至完全导通,如下图中最粗的曲线所示:

绿色:Vgs;黄色:Vds;紫色:Id;

- MOSFET的栅极驱动过程,可以简单的理解为驱动源对MOSFET的输入电容(主要是栅源极电容Cgs)的充放电过程;

- 当Cgs达到导通阈值电压之后, MOSFET就会进入开通状态;当MOSFET开通后,Vds开始下降,Id开始上升,此时MOSFET进入饱和区;

- 但由于米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs又上升到驱动电压的值,此时MOSFET进入电阻区,

- 此时Vds彻底降下来,开通结束。(由于米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长,从而增加了损耗。)

米勒平台

在第一个转折点处: Vds开始导通。Vds的变化通过Cgd和驱动源的内阻形成一个微分。因为Vds近似线性下降,线性的微分是个常数,从而在Vgs处产生一个平台。

米勒平台是由于mos管的gd两端的电容引起的,即MOS管datasheet中的Crss, 这个过程是在给Cgd充电,所以Vgs变化很小,当Cgd充到Vgs水平时,Vgs才开始继续上升。

Cgd在MOS刚开通的时候,通过MOS快速放电,然后被驱动电压反向充电,分担了驱动电流,使得Cgs上的电压上升变缓,出现平台。

Mos主要损耗也对应这几个状态,

开关损耗(开通过程和关断过程,与管子的开关频率乘正比,米勒平台,由于Vbus电压和负载电流不能改变,开关损耗由米勒平台的时间决定)。

导通损耗(Rdson,可以通过选型降低损耗),

续流损耗(体二极管,损耗大小由负载电流决定,不是所有系统都有),

还有雪崩能量损耗。只要把这些损耗控制在mos承受规格之内,mos即会正常工作,超出承受范围,即发生损坏。而开关损耗往往大于导通状态损耗,不同mos这个差距可能很大。

米勒效应的形成原理及分析

- t0-t1: 驱动电流Ig为Cgs充电,Vgs上升,Vds和Id保持不变,一直到t1时刻,Vgs上升到导通阈值电压Vgs(th),在t1时刻以前,MOS处于截止区。

- t1-t2: MOS管开始导通,也就标志着Id开始上升。在这个时间段内,驱动电流仍然是为Cgs充电,Id逐渐上升,在上升的过程中,Vds会稍微有一些下降,这时因为下降的di/dt在杂散的电感上形成一些压降。从t1时刻开始,MOS管进入饱和区。在饱和有固有转移特性:Id=Vgs*Gm,其中Gm为跨导,只要Id不变,Vgs就不变。Id在上升到最大值以后,而此时又处于饱和区,所以Vgs会维持不变。

- t2-t3: 从t2时刻开始,进入米勒平台期,米勒平台就是Vgs在一段时间几乎维持不变的一个平台,此时漏电流Id最大,且Vgs的驱动电流转移给Cgd充电,出现了米勒平台,Vgs电压维持不变,然后Vds就开始下降了。

MOSFET中的米勒平台其实就是MOSFET处于“放大区”的典型标志。 只要电路工作在放大区,功耗比较大,需要放大时间特别短,MOS管也是在这个区域坏的最多。电子器件,三极管和MOS管在从关断到完全饱和的过程中必然会经过一个放大区。三极管经过放大区的时间极短,相对MOS管不那么容易坏。

放大区功耗大的问题举例:

- t3-t4: 当米勒电容Cgd充满时,Vgs电压开始继续上升,直到MOS管完全导通。所以,在米勒平台,是Cgd充电的过程,这时候Vgs变化很小,当Cgd和Cgs处在同等水平时,Cgs才开始继续上升。

Crss不是一成不变的,与漏极电压有关,电压越高,米勒效应越明显。高压系统的管子要更注意米勒效应。

米勒效应的危害和改进

米勒效应会产生米勒平台,也就是开通阶段阻碍驱动电压的上升,关断阶段阻碍驱动电压的下降,延长了开关时间,导致损耗严重,降低了电路的效率。另外,MOS管不能快速的开关,容易造成稳定性降低。

对于有上下管驱动的电路,有上下管同时导通的风险。如下分析:

- 上管开通,下管关断时的情况

在上管开通和关断时,下管栅极上会产生一个尖峰,尖峰的电压增加了上下管同时导通的风险,严重时会造成非常大的电流同时流过上下管,损坏器件。

在下管关断后,上管米勒平台结束时,桥臂中点电压由0V升到VDD, MOS管的源极和漏极之间产生陡峭的dv/dt。由此,在Cgd电容产生的电流会流到栅极,经栅极电阻到地,这样就会在栅极电阻上产生电压降。这种情况,可能发生上下管导通的风险。

- 上管关断下管开通时的波形

下管开通关断出现的这种波形是由Cgd电容导致的寄生开通现象。

但因为MOS管的制造工艺,一定会产生Cgd,也就是米勒电容一定会存在,所以米勒效应不能避免。当MOS管的输入信号频率较高时,米勒电容会显著影响MOS管的开关速度,产生一个延迟时间,称为米勒平台时间。因此,在高频应用中,需要考虑米勒平台时间对系统性能的影响。

改进措施:

- 降低栅极电阻的阻值,使Igs的电流增大,栅极驱动极的电流能力要大。

- 提高栅极驱动极的电压,±20V内

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 使用Linux SDK客户端向AWS Iot发送数据

- 【MySQL】给除了主键外的字段设置自增

- 一文看懂四大汽车总线:LIN、CAN、FlexRay、MOST

- 在gen_server使用ets实例演示

- 如何快速备战软件评测师?超详细备考思路

- H5的3D游戏开源框架

- 一款应用于指纹门锁上的安全芯片ACM32FP421系列,内核性能高,安全性高,内建 AES、CRC、TRNG 等算法模块

- IPQ8072: Reshaping the future of network processors

- Java Web项目中 JSP 访问问题

- 如何在 JavaScript 中过滤嵌套对象?