NXP 数位电源系列 - 如何使用 DSC 实现 PSFB Peak Current 控制 (1/3) - 全桥 PWM 波形的实现方式

本文主题是介绍如何以 NXP 的 DSC 实现 Peak Current Control Mode PSFB 功能的系列文章。文章分为三篇,本篇会先介绍 DSC 是使用那些功能来实现全桥 PWM,续篇会解说 PSFB 的动作机制。第三篇则是同步整流 PWM 的实现方式,以及透过内部机制侦测当前的 PWM 切换状态。

相位移全桥 (Phase shift full bridge,简称 PSFB) 是经常使用在大功率电源上的电源架构,使用两个 Duty 固定在 50% 的半桥开关组成全桥转换器架构,利用两个半桥间开关的相位差导通变压器初级侧,将能量转换到次级侧。由于相位差产生的开关导通时间顺序,正好可以用来使开关上的电压在导通前降至 0V,从而实现零电压切换 (ZVS) 切换来提高效率。

PSFB 在一个周期内会有两个导通的时段,分别对变压器的磁化电感充磁与泄磁。在传统的电压控制型 PSFB 电路上,是以输出电压的补偿器来决定目前输出的 Duty,两个导通时段在设计上是相同的。但是还是会因为以下的原因导致电感的充磁与泄磁的能量不同。

-

PFC 的输出电容上存在的 120Hz 涟波电压

-

每颗开关的 Rds(on) 不同导致两个区间上的电感电流不同

-

实际上开关讯号有可能因为电路延迟或 IC 的缺陷导致时间不同

-

开关晶体的 Coss 不同导致实际开关导通的时间不同

磁化电感的充磁与泄磁的能量不同,则变压器会产生磁偏,磁化电感无法工作在固定的磁化曲线上,会渐渐地朝某一边偏,最后导致电感饱和。饱和则会导致电感呈现短路状态,开关晶体则会因为短路的大电流损坏。因此必须要增加增加平衡电路,使磁偏可以被平衡回来。

但是平衡电路会造成多馀的成本与损耗,因此后来便提出了峰值电流控制模式 (Peak current control mode) 的方式,控制的对象由相位移的角度变成变压器两个区间的峰值电流,而输出电压的补偿器则是控制变压器电流的大小。如此一来便解决了磁偏的问题,但是让开关以峰值电流控制的开关方式切换需要复杂的功能来实现。

传统的 PSFB 的电路基本和和传统的全桥转换器相同,但是能量传输的方式较为特殊。是使用带有 Deadtime 的 50%? Duty PWM 分别控制两组半桥开关,当两个半桥开关的相位差大于零,使对角的开关 PWM 交叠时,变压器就可以从输入电压获得能量来进行转换。由于控制的对象是相位差,因此可以将其中一组半桥视为固定臂,另一组开关动作上相位落后的则视为相移臂。

而 Peak Current Control Mode PSFB 在电路上则多了一个变压器电流侦测的比流器,而在 PWM 上,因为采取控制变压器磁化电流的方式,因此 PWM 不再是固定的 50% Duty,而是以电流峰值来决定开关的运作。实际运作上,与传统 PSFB 相同,一样存在一个固定臂,而另一组相移臂则在电流上升顶到目标时进行开关状态的切换。

在电源上采用峰值电流控制方式时,在能量传输区大于周期 50% 时会开始因次谐波震荡的问题而有控制不易稳定的情况发生。原因与理论推导就不加详述,结论上来说,一般采用峰值电流控制时,都会需要导入负斜率补偿到电流峰值的参考讯号中来解决这个问题。

当使用 MCU 实现 PSFB 波形时,由于峰值电流控制相移,而电流变化的速度又远高于一般 MCU 的 ADC 采样与控制环路的计算速度,因此电流控制的相移臂动作会需要以硬体方式实现。以下先归纳一下要实现 PSFB 全桥开关控制的 PWM 所需要的功能。

-

全桥的固定臂要可以设定固定的 PWM 频率,并在需要时可以改变频率 ( 用作产生 Jitter 降低 EMI 噪声 )。

-

四个 PWM 都需要有 Deadtime,Deadtime 需要可以调整以优化效率。

-

变压器顺向与逆向电流的电流峰值必须相同,避免造成磁偏。因此相移臂应该在每次峰值电流顶到相同高度时切换相移臂的开关的状态。

-

电流的参考讯号需要带有负斜率。

-

相移臂需要具备不传输能量的状态 ( 相移角 0 度或是关闭 PWM 输出 )。

-

可以限制最大的相移角度低于 180 度或是更低,以避免变压器初次侧两端短路。

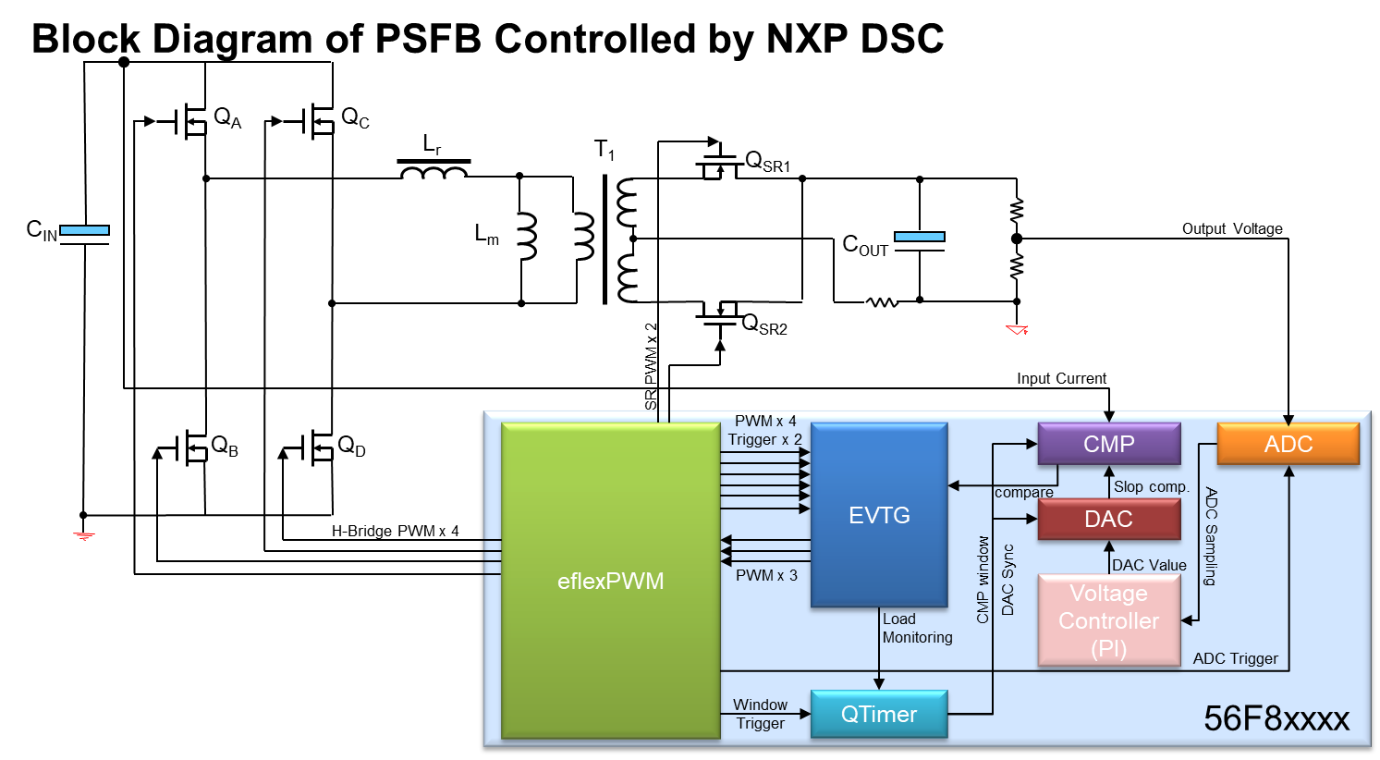

NXP 的 DSC 具备了灵活的功能,使用内部的专用功能互相搭配,可以完成所需波形的所有功能。整体控制环路的框图可以参考下图,所有的 PWM 都透过 eflexPWM 模组输出,内部的数个模组之间互相连动,搭配软体的 PI 环路控制 PSFB 转换器的输出电压。

NXP PSFB Block Diagram

?

主要的控制环路,分为由 ADC 与软体控制器实现的电压环,以及使用 DSC 硬体实现的电流环。

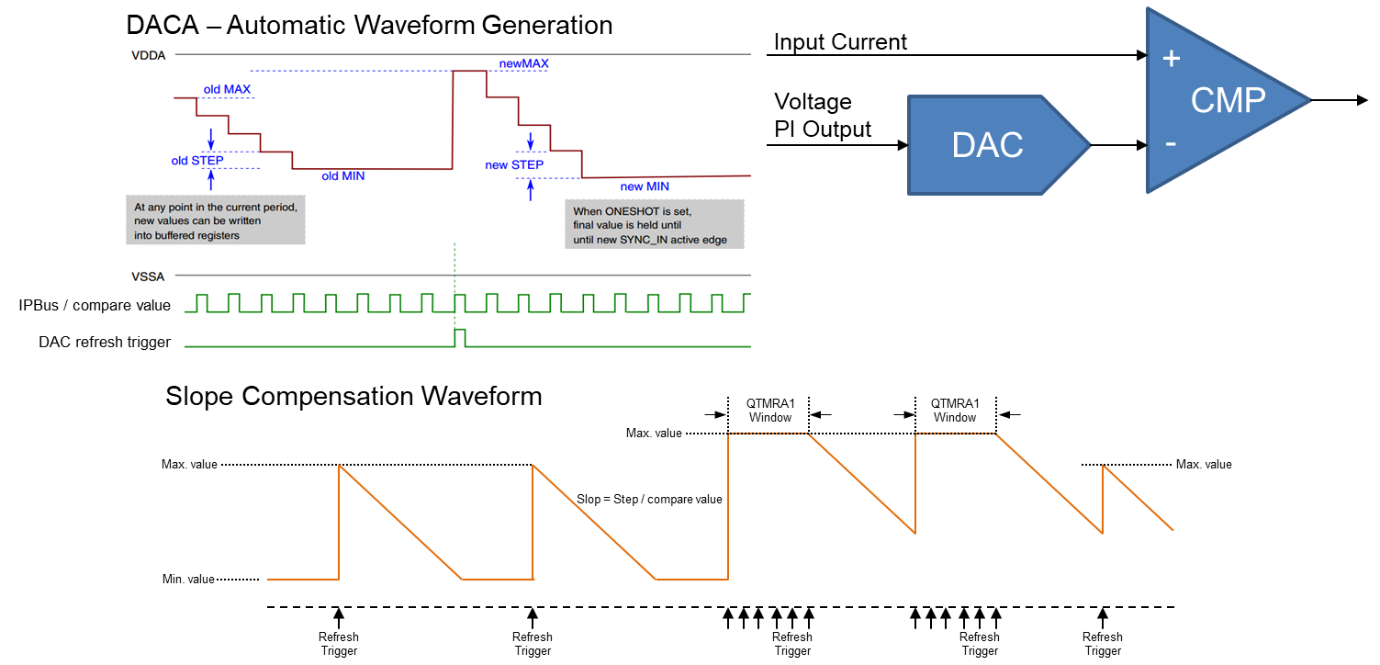

硬体电流环的实现方式,会使用到几个内部模组互相搭配。首先是峰值电流侦测的比较器与参考讯号。参考讯号由 DAC 产生,比较器则负责输出电流采样讯号与参考讯号比对的结果。

-

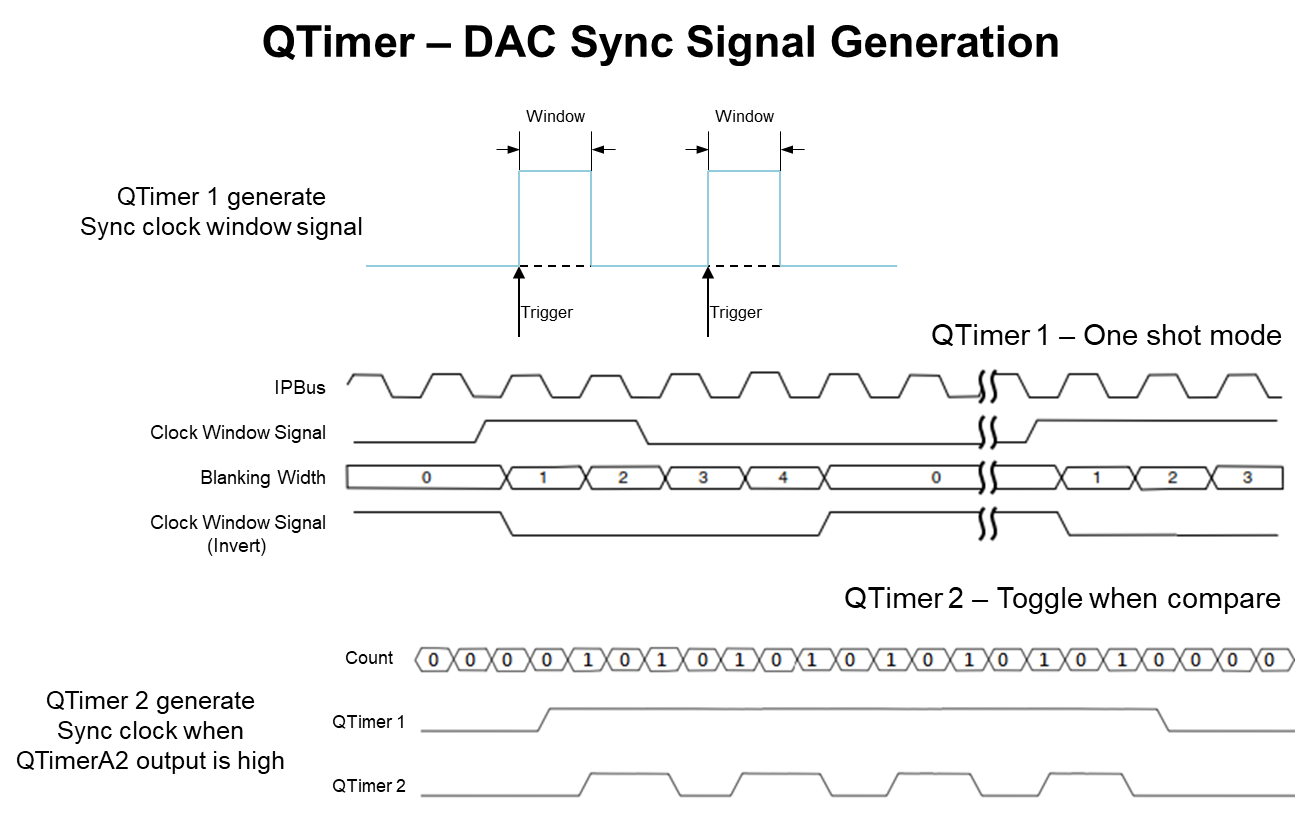

QTimer ( DAC Refresh Trigger ) : 使用两组 QTimer 通道产生可以连续触发的 DAC SYNC 讯号,如此一来,当负斜率波形的起点超过 DAC 输出上限的 3.3V 时,可以使超出 3.3V 的部分维持在 3.3V 。

-

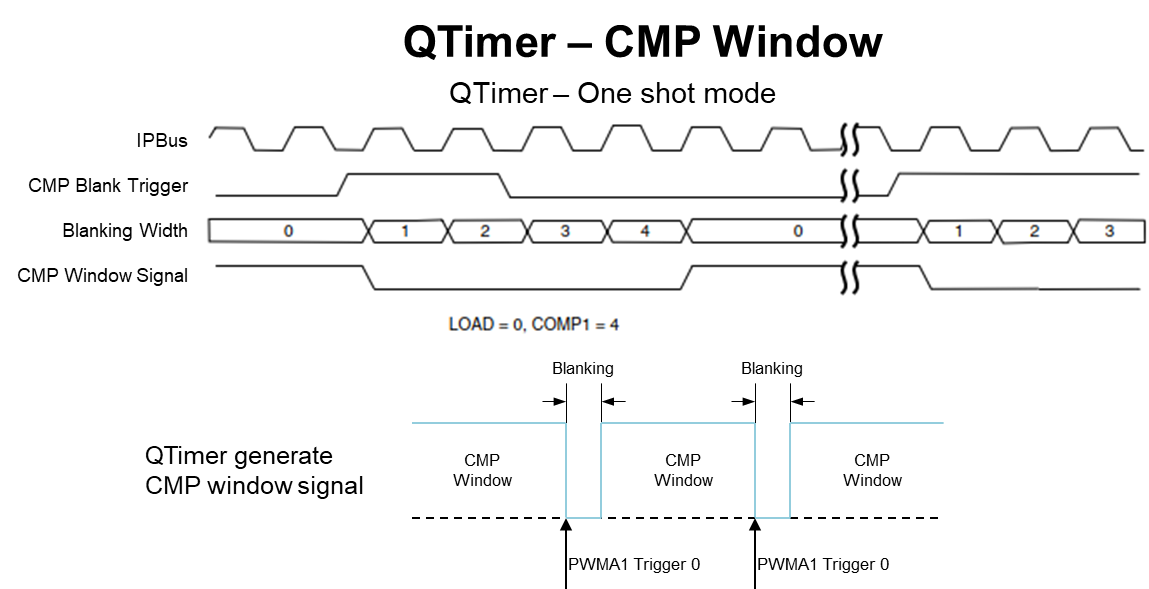

QTimer ( Window ) : 由于在开关切换时的杂讯较大,单靠比较器的滤波来处理不太合适,因此使用 QTimer 用来产生避开杂讯的 Window 讯号,使比较器只在 Window 讯号存在时才会改变输出。

-

DAC : 带有自动波形产生功能的 DAC 可以用来产生带有斜率补偿所需的向下斜坡的参考电压,作为峰值电流控制环路参考电流使用。透过 SYNC 讯号与双缓冲的暂存器,DAC 可以不使用 CPU 或是 DMA 的资源,就能透过 QTimer 触发负斜率波形的更新,使负斜率波形的更新完全与 PWM 同步。

-

CMP : 带有滤波与迟滞级数调整的比较器可以构成峰值控制环路的一部分,并且很好的过滤掉可能产生的杂讯。

-

EVTG : 这个模组内部带有逻辑闸电路与可程式化正反器,可以透过设置产生全桥波形中 PWM 相移臂的 PWM 来源讯号。

-

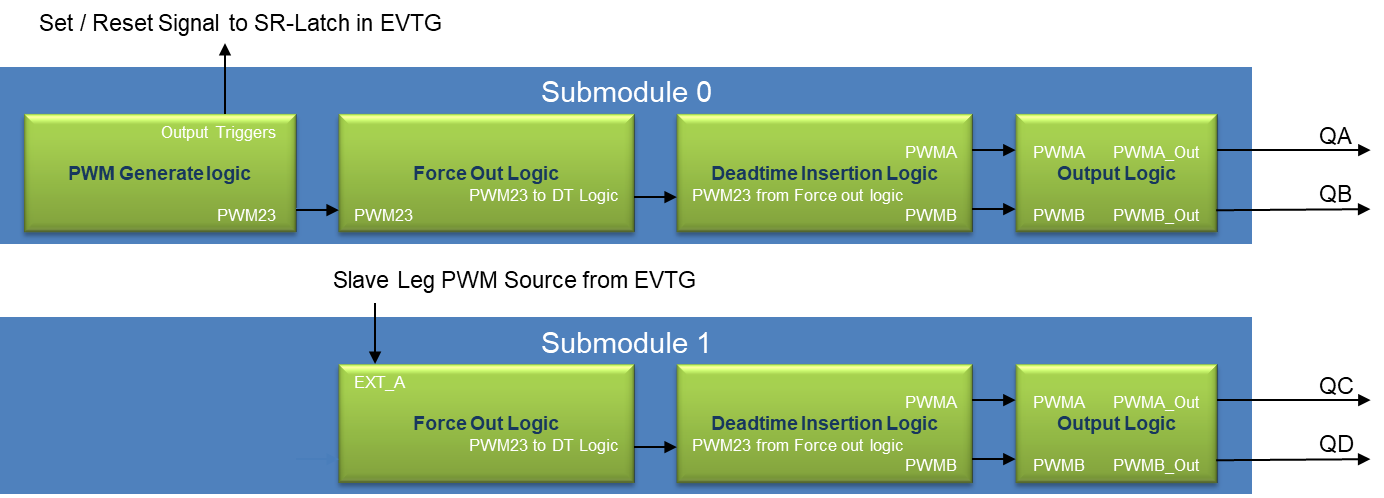

eflexPWM : 第一个通道 ( Submodule 0 ) 负责 PWM 固定臂 PWM 的产生。第二个通道则负责将来自 EVTG 的相移臂 PWM 参考讯号生成带 Deadtime 的互补对 PWM。

以 DSC 实现的 PSFB 带有以下优势 :

-

电流环路完全由硬体机制实现,不占用程式资源。

-

相移臂可以由软体决定相移量的上限,上限可以在运作中灵活调整,可以与电流侦测的动作并行,不会有误动作情形。

-

比较器有额外的 Filter 功能,可以确保电流侦测的正确性。

-

比较器带有 Window 功能,可以无视周期中固定时段产生的特定讯号,比如固定臂开关的 Switching Noise 或 CT 取样电路的二极体反向恢复杂讯。

-

PWM 全由同一个模组输出,可以做到与周期同步的 PWM 开启与关闭,避免开启或关闭 PWM 时造成 PSFB 硬体上运作有某些不理想的情况发生。

本篇介绍的是 DSC 实现 PSFB 全桥的 PWM,下一篇将针对其中的运作原理与动作的方式进行说明及演示。

若想要知道相关的细节,请联络 Jamescl.hsu@wpi-group.com

?

【NXP 数位电源系列 -如何使用 DSC 实现 PSFB Peak Current 控制 (1/3)~(3/3)】系列文章现已全部更新,感兴趣的小伙伴可移步大大通网站查看~使用搜索功能快人一步

?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!