【USTC】verilog 习题练习1-5

发布时间:2024年01月18日

1?编写 Verilog 代码,使电路输出信号1

输入格式

无输入

输出格式

输出1,位宽为1

module top_module(

output out

);

// Write your code here

assign out =1;

endmodule2编写 Verilog 代码,使电路输出信号0

输入格式

无输入

输出格式

输出0,位宽为1

module top_module(

output out

);

// Write your code here

assign out = 0;

endmodule3 WIRE

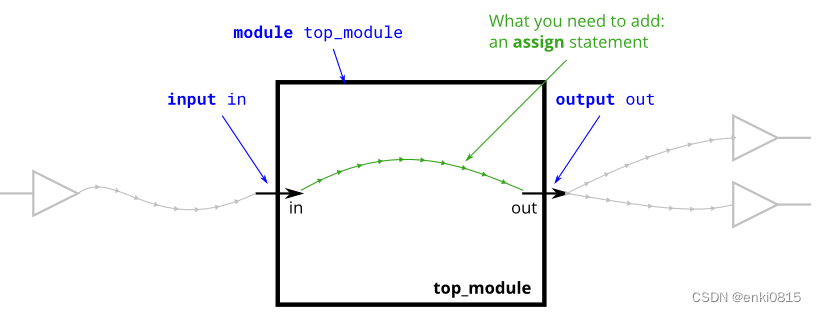

wire 是 Verilog 的关键字,用于表征信号类型的,其含义是线网。wire 可理解为物理连线,但又有所不同,因为 Verilog 中的 wire 是有方向的。例如设计一模块,模块名命名为 top_module,输入信号名为 in,输出信号名为 out,使 in 与 out 直连,如下图所示:

请使用 assign 语句将代码补充完整,使其实现上述电路图的功能。

输入格式

任意

输出格式

与输入完全相同

module top_module(

input in, output out

);

// Write your code here

assign out = in ;

endmodule4?多个端口的模块

题目描述

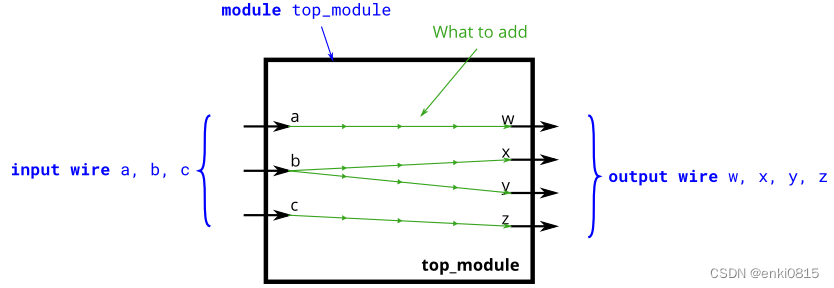

wire是Verilog的关键字,用于表征信号类型的,其含义是线网,wire可理解为物理连线,但又有所不同,因为verilog中的wire是有方向的,例如设计一模块,模块名命名为top_module,输入信号名为in,输出信号名为out,使in与out直连,如下图所示:

请使用assign语句将代码补充完整,使其实现上述电路图的功能

输入格式

1 1 1

输出格式

1 1 1 1

module top_module(

input a,b,c,

output w,x,y,z );

// 请用户在下方编辑代码

assign w=a;

assign x=b;

assign y=b;

assign z=c;

//用户编辑到此为止

endmodule

5?非门

题目描述

创建一个名为top_module的Verilog模块,实现非门的功能

输入格式

无

输出格式

无

module top_module( input in, output out );

// 请用户在下方编辑代码

assign out = ~in;

//用户编辑到此为止

endmodule

文章来源:https://blog.csdn.net/luhputu520/article/details/135651857

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 抖音小店2024年创业新趋势,新手找项目,不要再错过这次的机会了

- IP代理检测:关于Ping测试你需要知道的一切

- 中国社科院与新加坡社科大联合培养博士——为未来壮大事业打下坚实的基础!

- 每日一题——LeetCode1154.一年中的第几天

- Kafka安装及简单使用介绍

- Nomad Web中导出notes.ini和应用

- HBase基础知识(六):HBase 对接 Hive

- redhat linux 8 安装 阿里云centos-8 yum源(网络yum源配置)

- AutomationML 学习心得

- springboot中使用mongodb进行简单的查询