数字IC后端实现之物理验证Calibre LVS常见错误案例解析

小编今天向各位分享下数字IC后端实现物理验证中特别经常遇到的几类Calibre LVS错误。相信只要把这几类LVS Violation彻底搞清楚,那么LVS基本上你都可以很轻松过掉。

在进入Calibre LVS案例前,小编提醒下各位,在看LVS报告前一定要确保LVS的layout extraction抽取报告是clean的。

1)查看layout的抽取报告

2)查看LVS report

3)查看ERC report (有些比较严重的ERC会导致LVS INCORRECT)

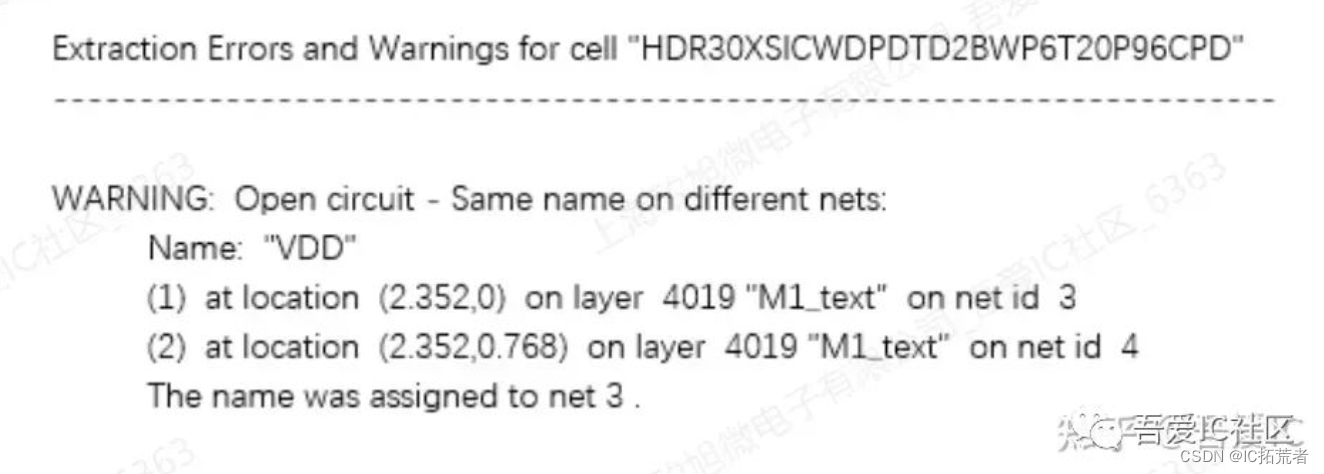

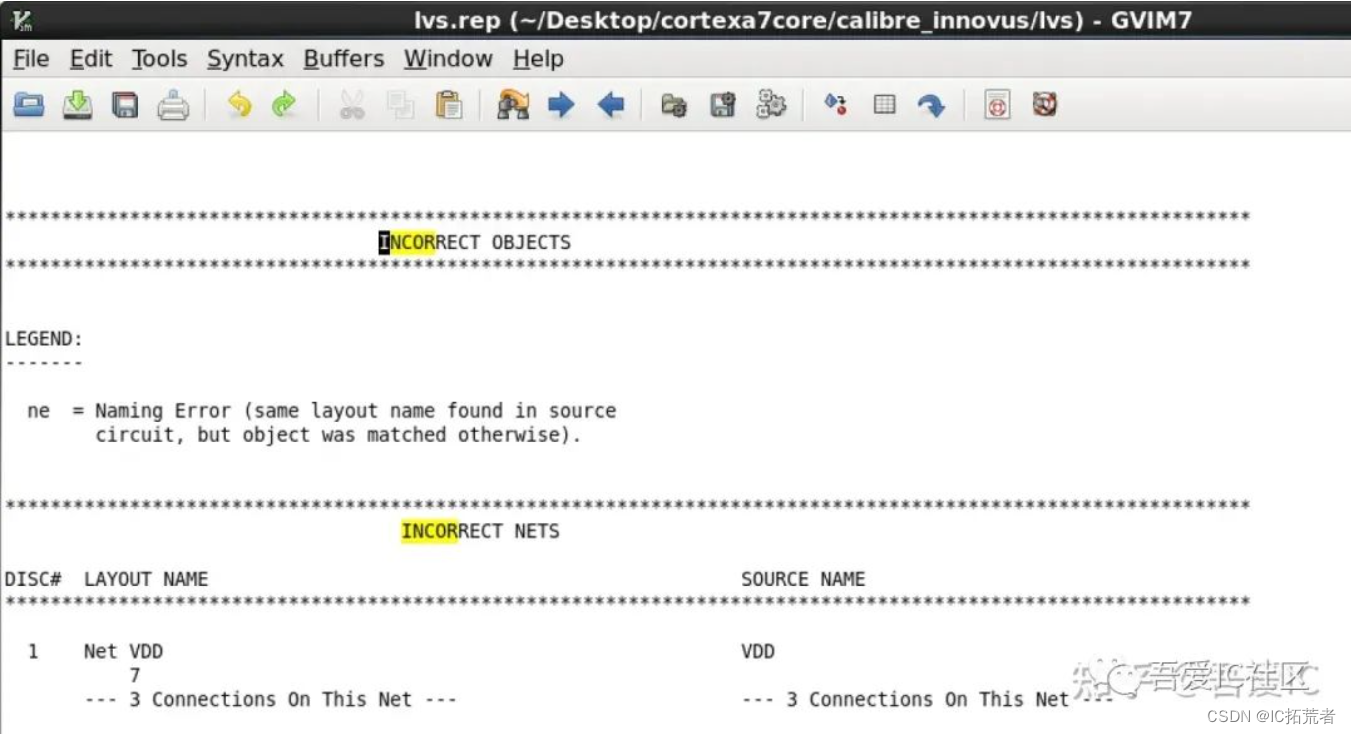

案例一:Same name on different nets

典型的Open现象。属于设计中的power switch cell没有供电导致的。

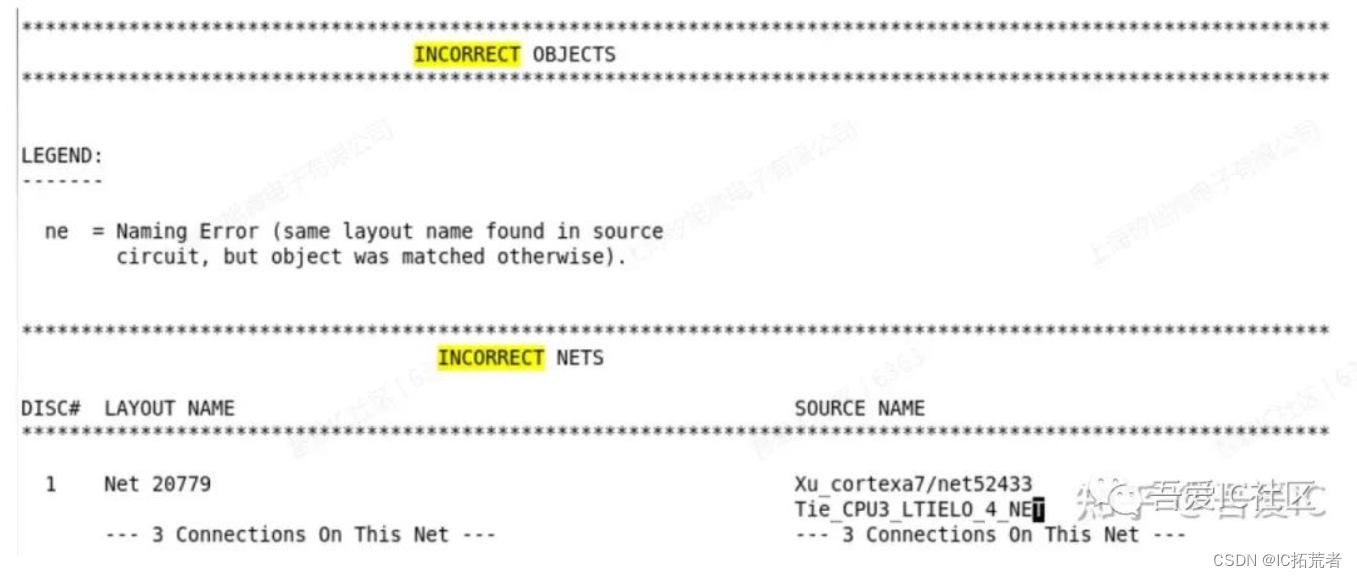

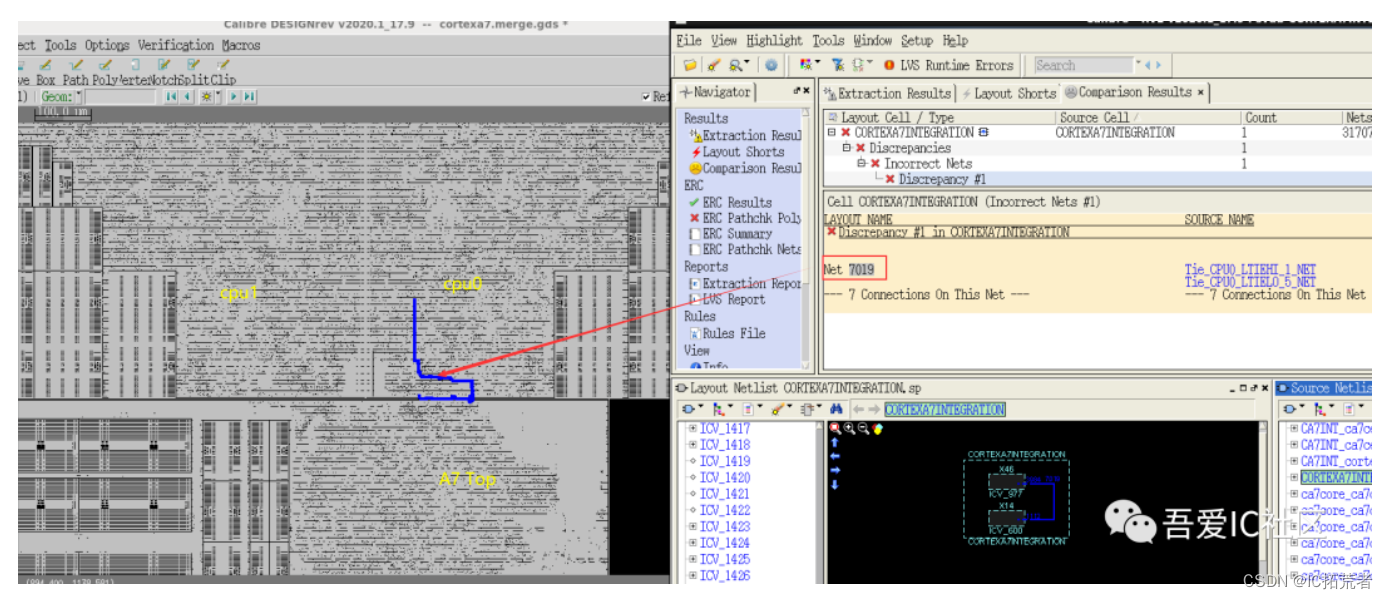

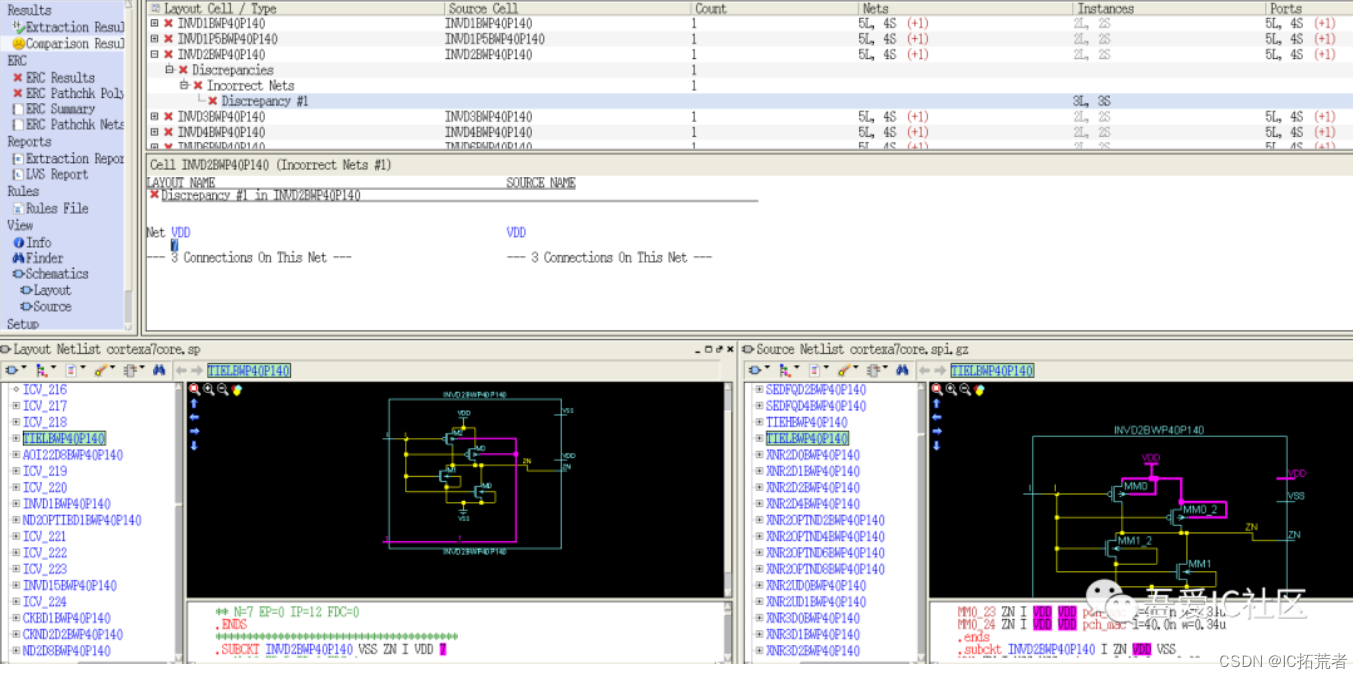

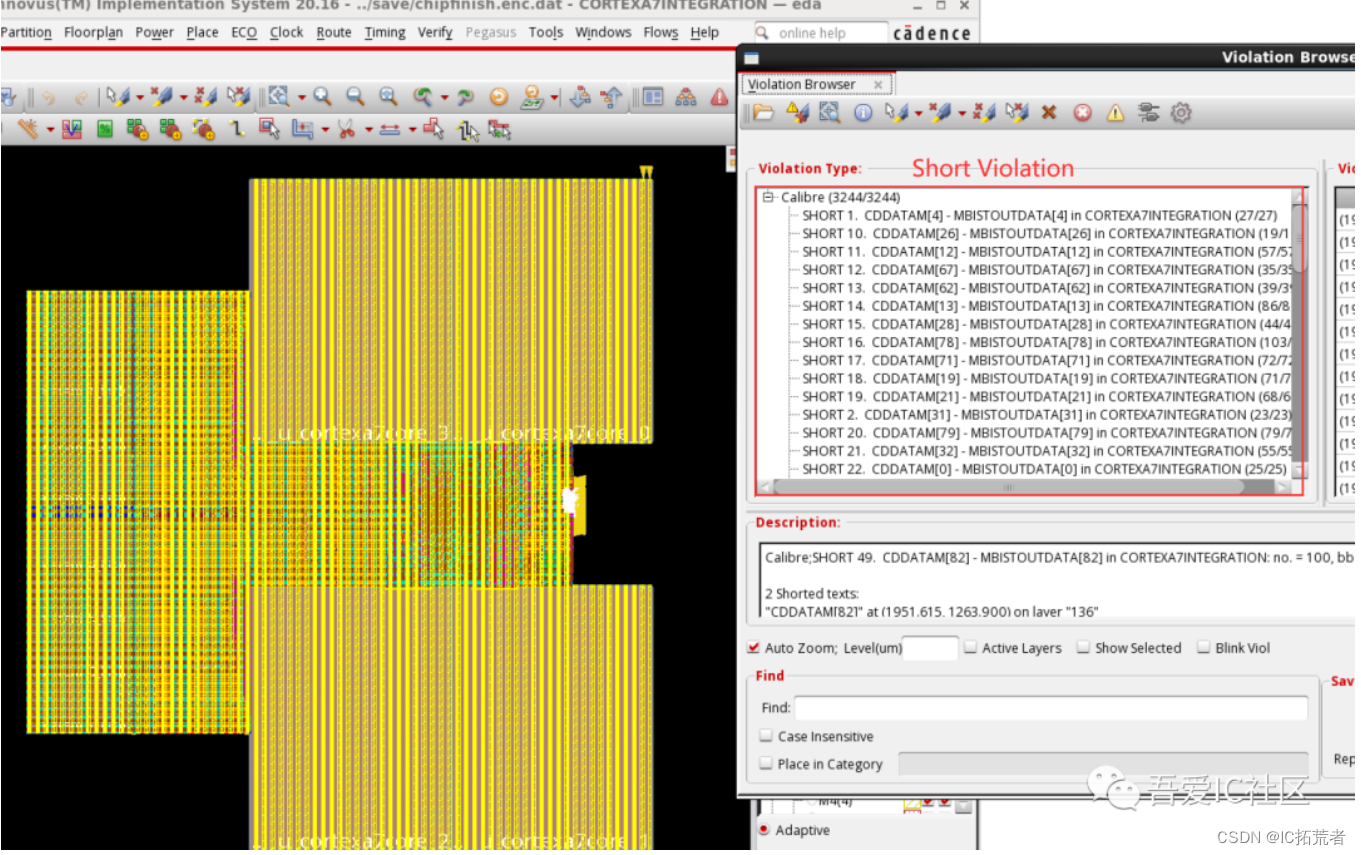

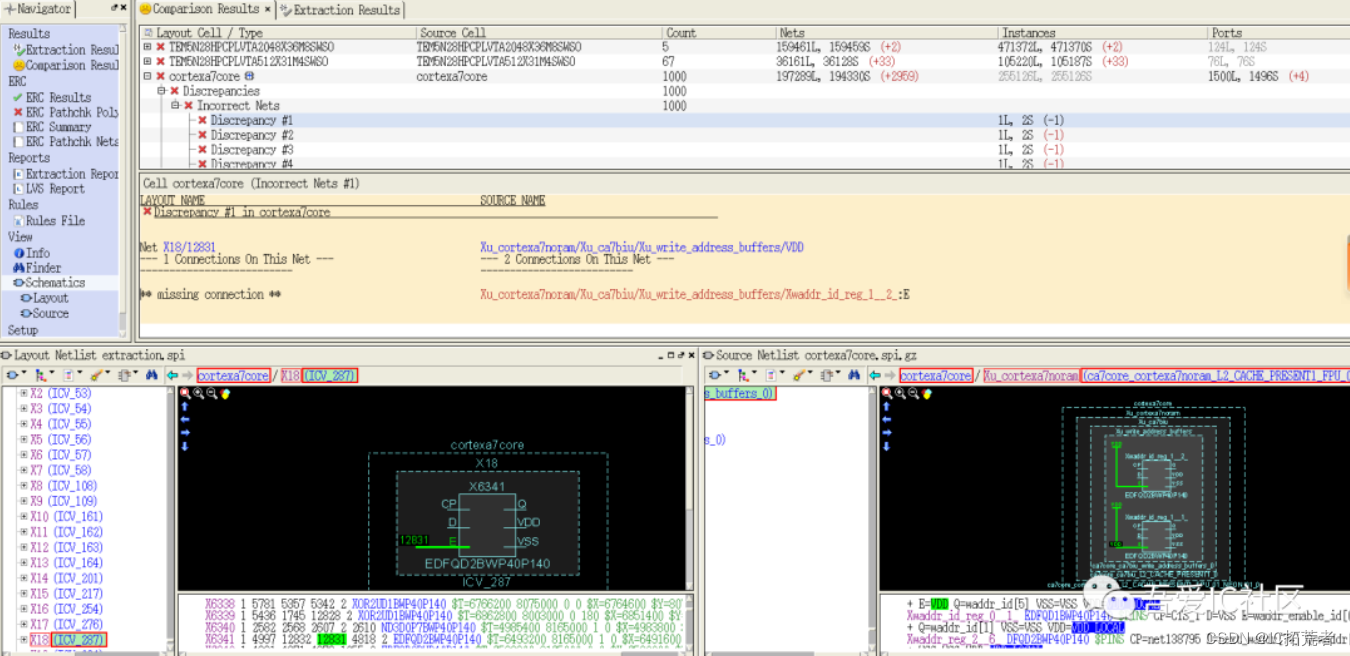

案例二:Flatten LVS发现顶层和子模块接口的LVS错误

经过定位发现是子模块cortexa7core的内部信号和A7 Top中的Tie信号在接口处存在short。

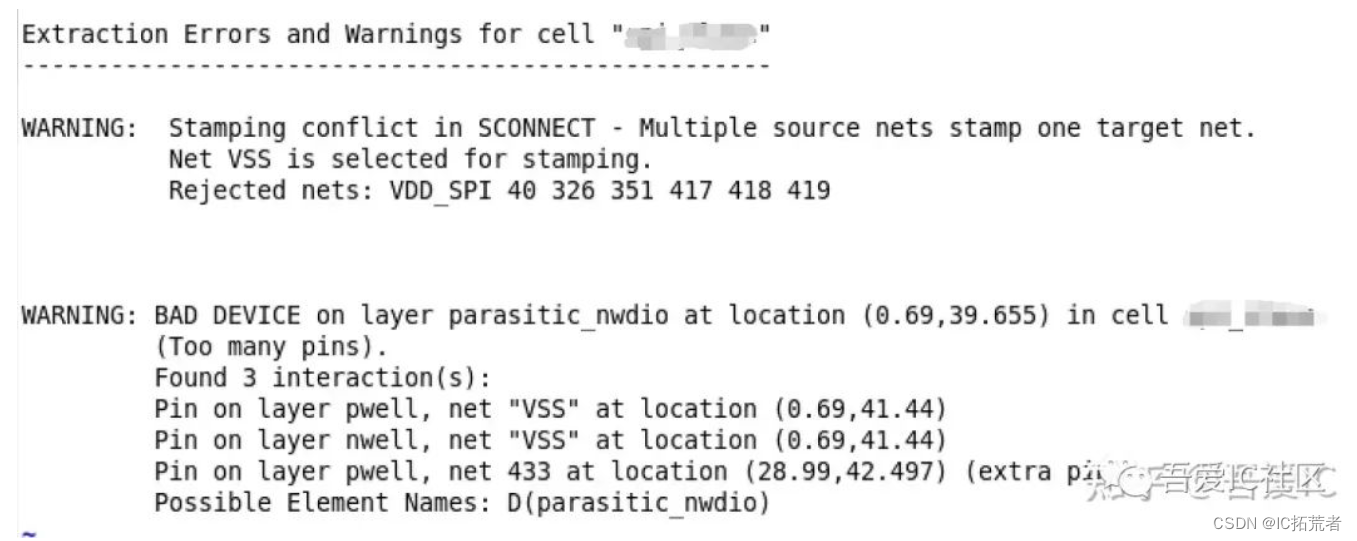

案例三:SCONNECT错误——Net VSS is selected for stamping

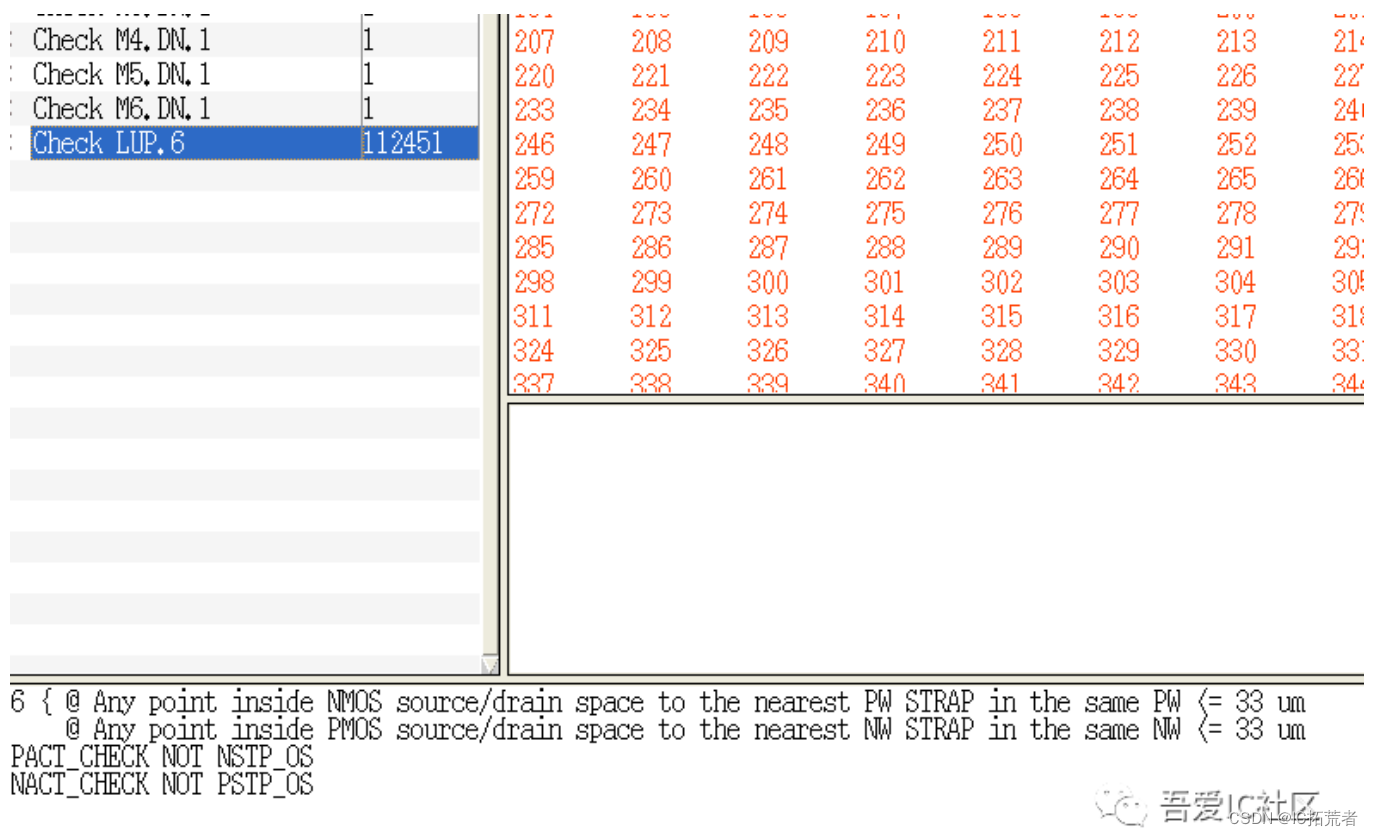

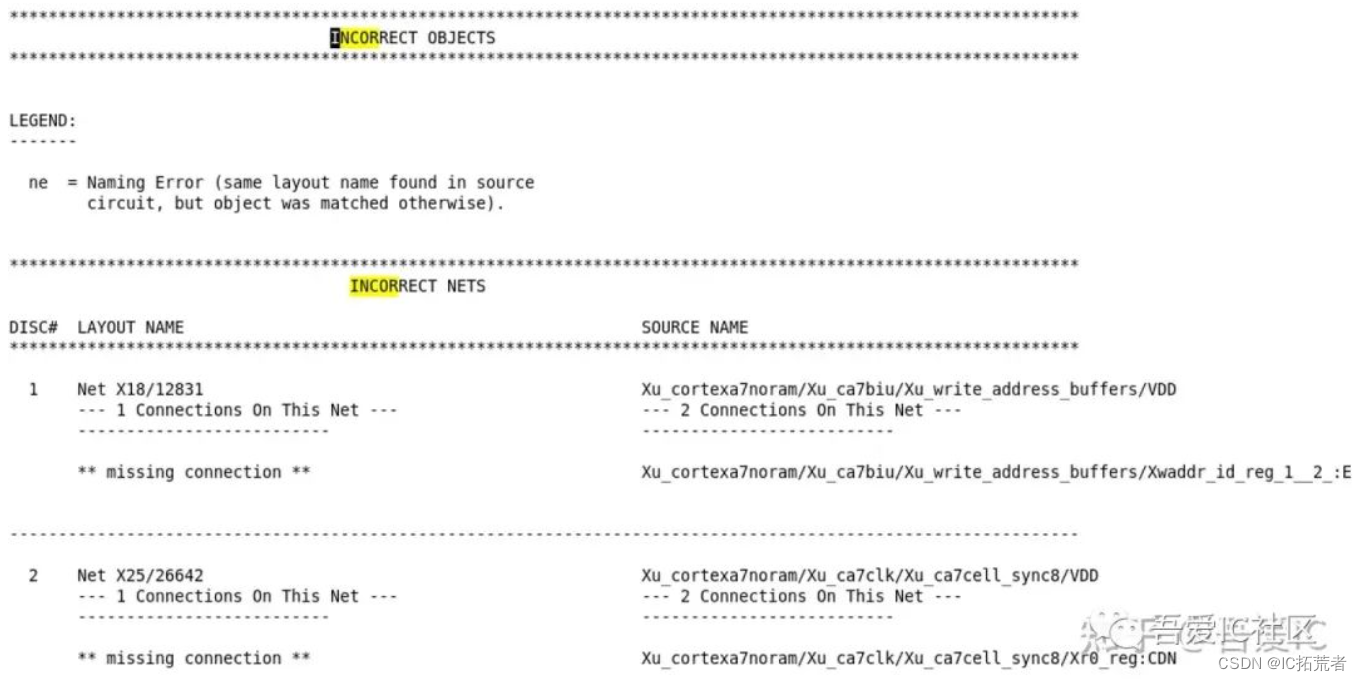

案例四:INCORRECT NETS之Layout比SOURCE多一条net

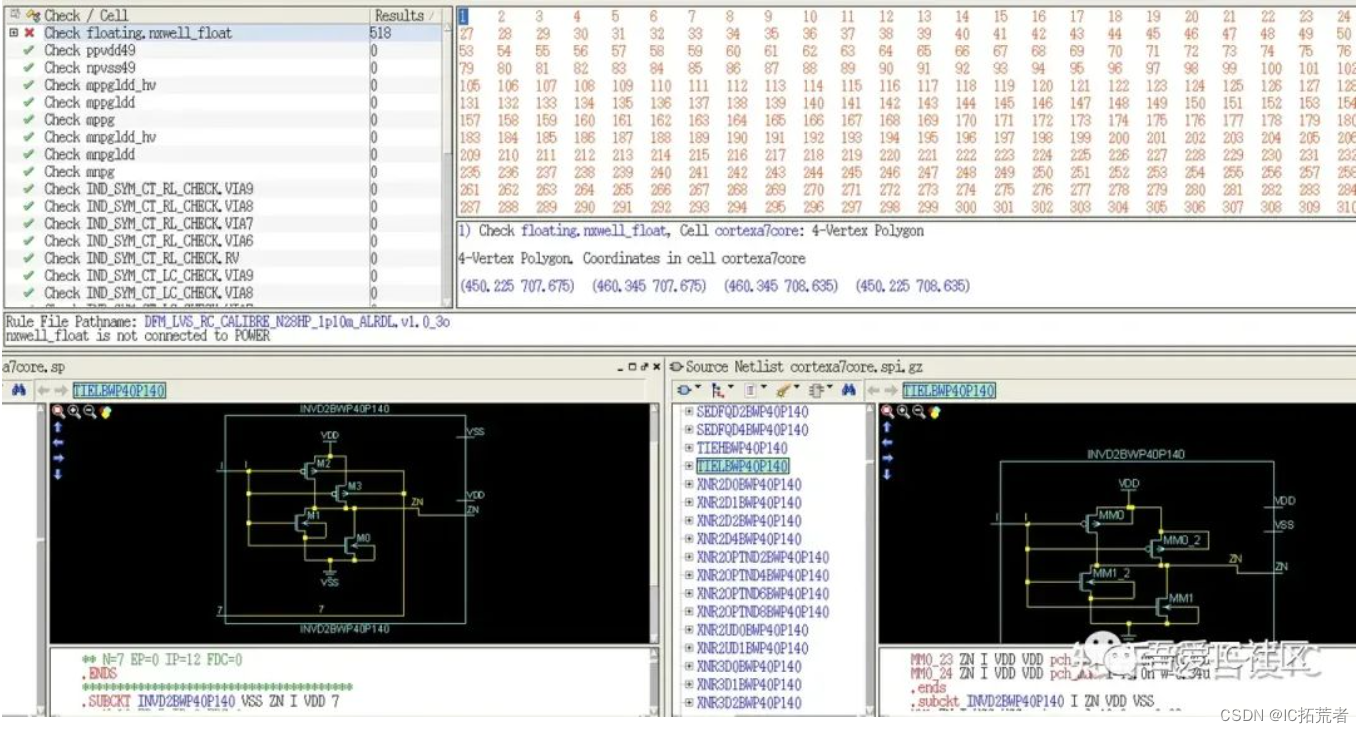

提示:设计中存在nwell和psub没有连接到对应电位的情况(通过ERC结果分析得知)。

如果此时拿着这个gds去做calibre drc检查,你也会发现存在大量LUP.6的DRC Violation。

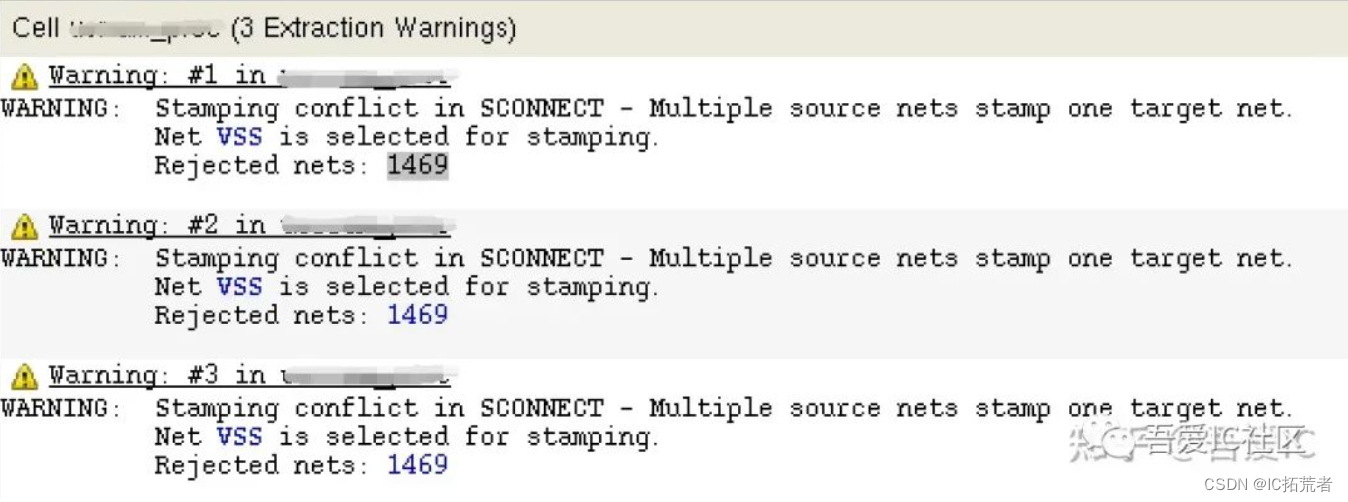

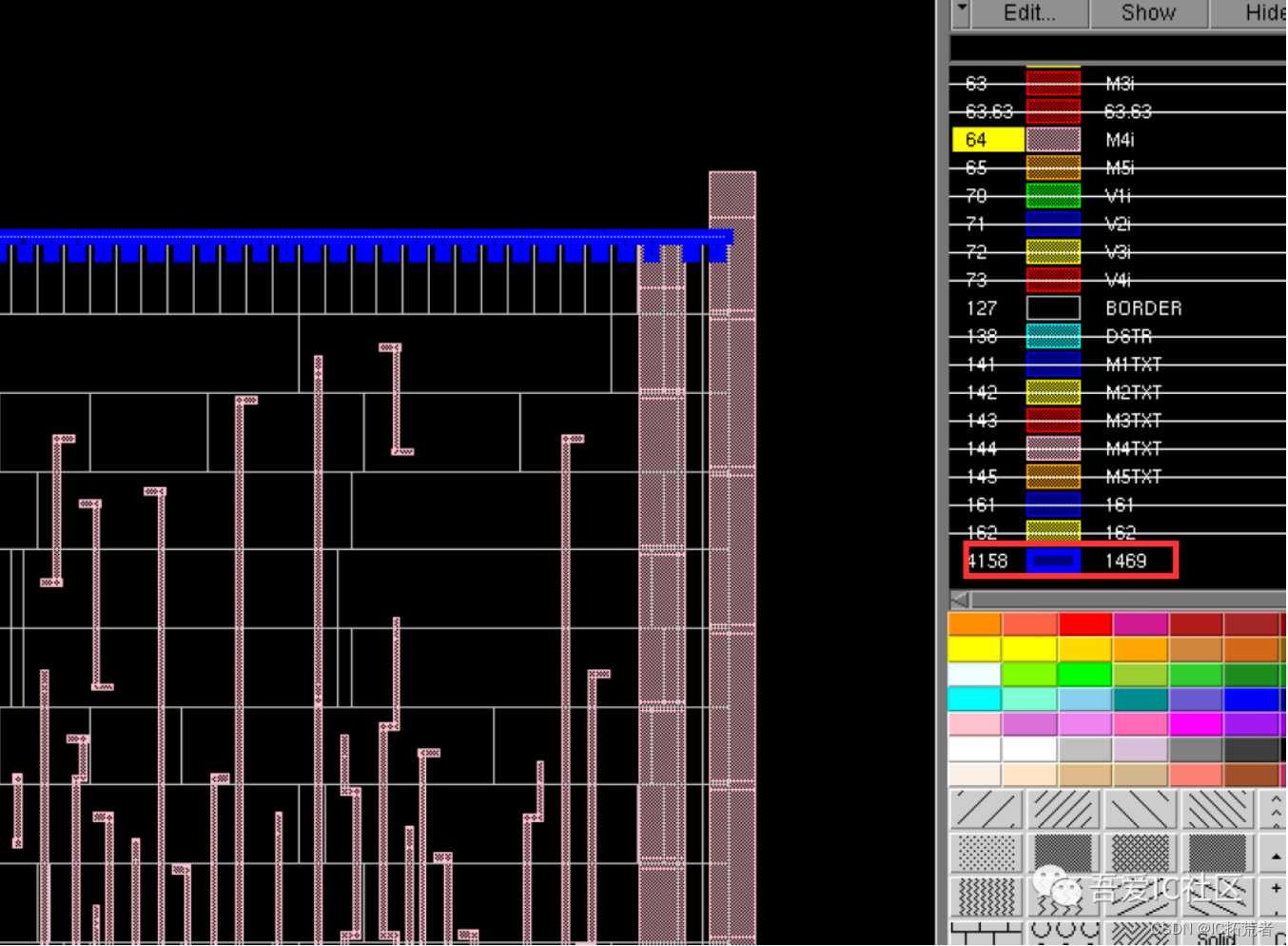

案例五:Stamping Conflict 错误

高亮1469这条net后很容易就可以看到存在M1的VSS power rail floating的情况。

这里重点提醒下:设计中有soft connect问题必须解决。而ERC的有些错误可能是假的,但这种一般都是设计中两条不同的信号short在一起了(或missing label)。

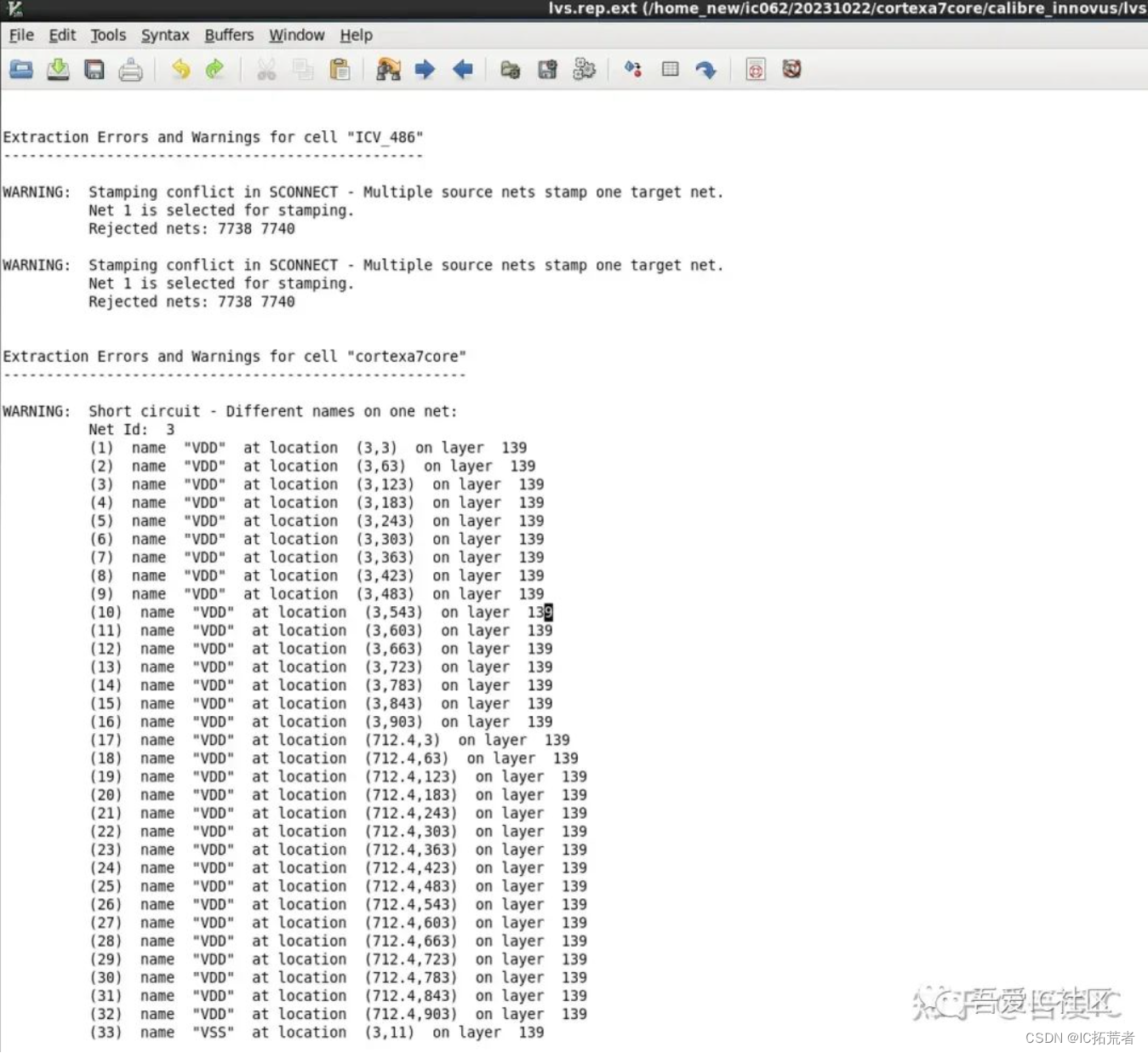

案例六:GDS抽取报告的Short circuit 错误

这个案例是设计中存在PG的short,即VDD和VSS存在short。遇到这种情况calibre会在当前LVS的目录生成一个lvs.rep.shorts文件。我们可以把这个文件直接导入到PR工具进行分析,快速定位到PG short的位置。

案例七:Layout missing connection错误

https://alidocs.dingtalk.com/i/nodes/4Pko7gla1mAWR7ZkkwopVBxz5qZY9Q6j?doc_type=wiki_doc&dontjump=true&utm_medium=main_vertical&utm_scene=team_space&utm_source=search# 「Innovus&ICC2获取设计中input floating pin 的golden脚本」

案例八:Floating NWELL错误

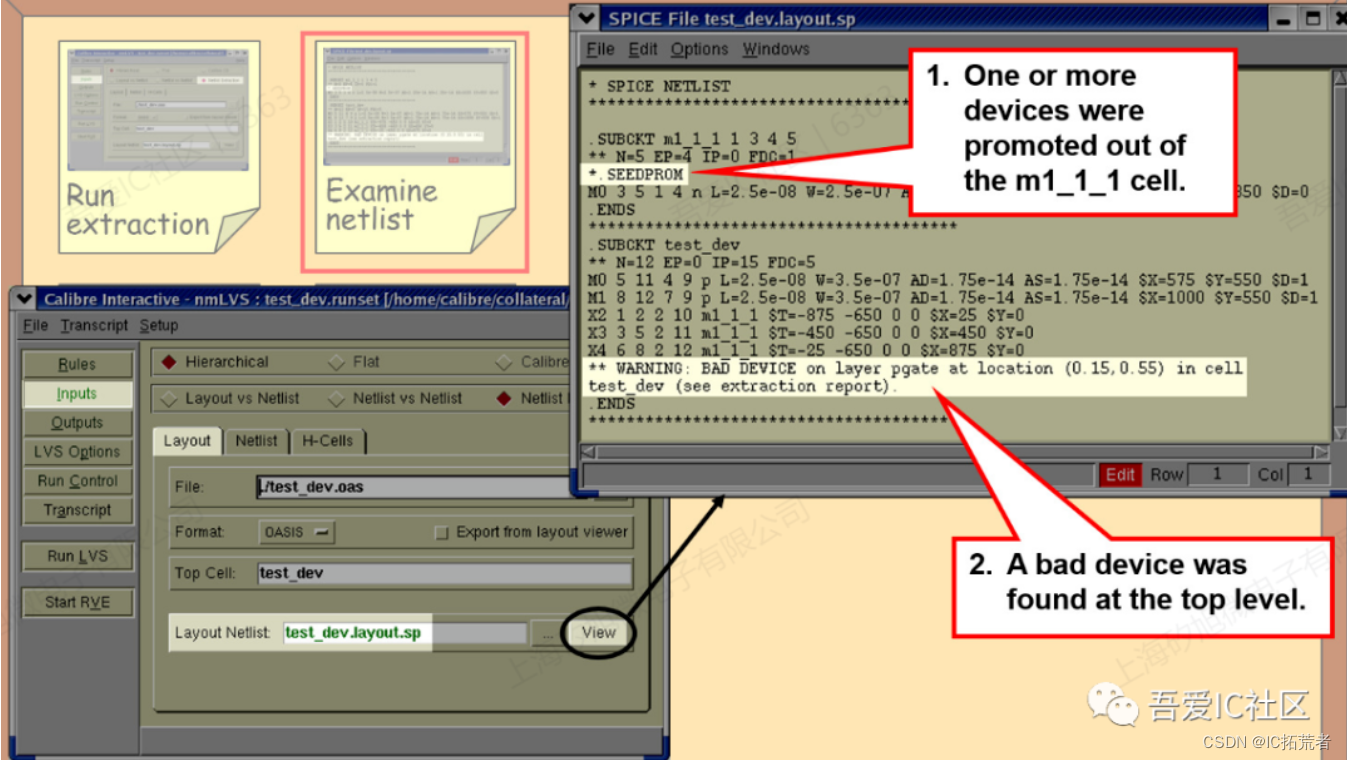

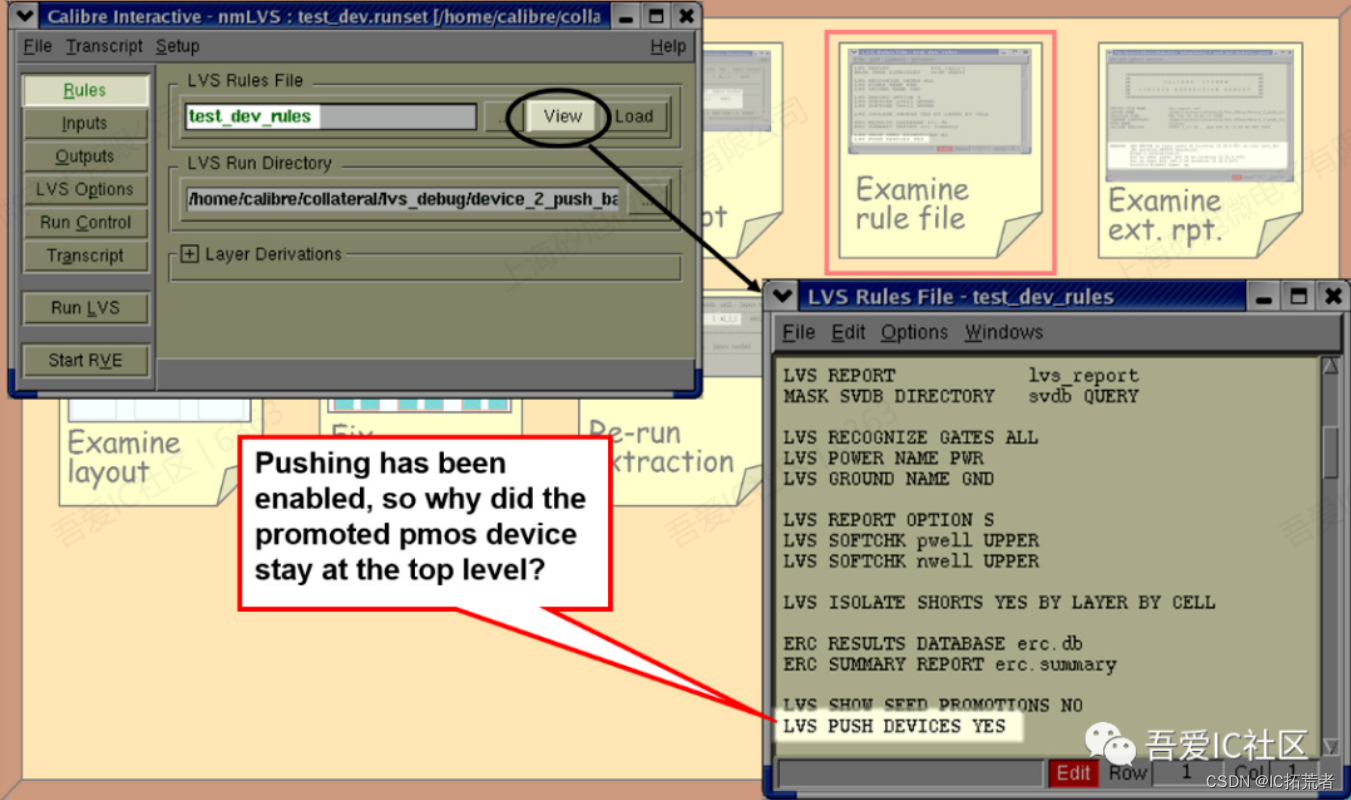

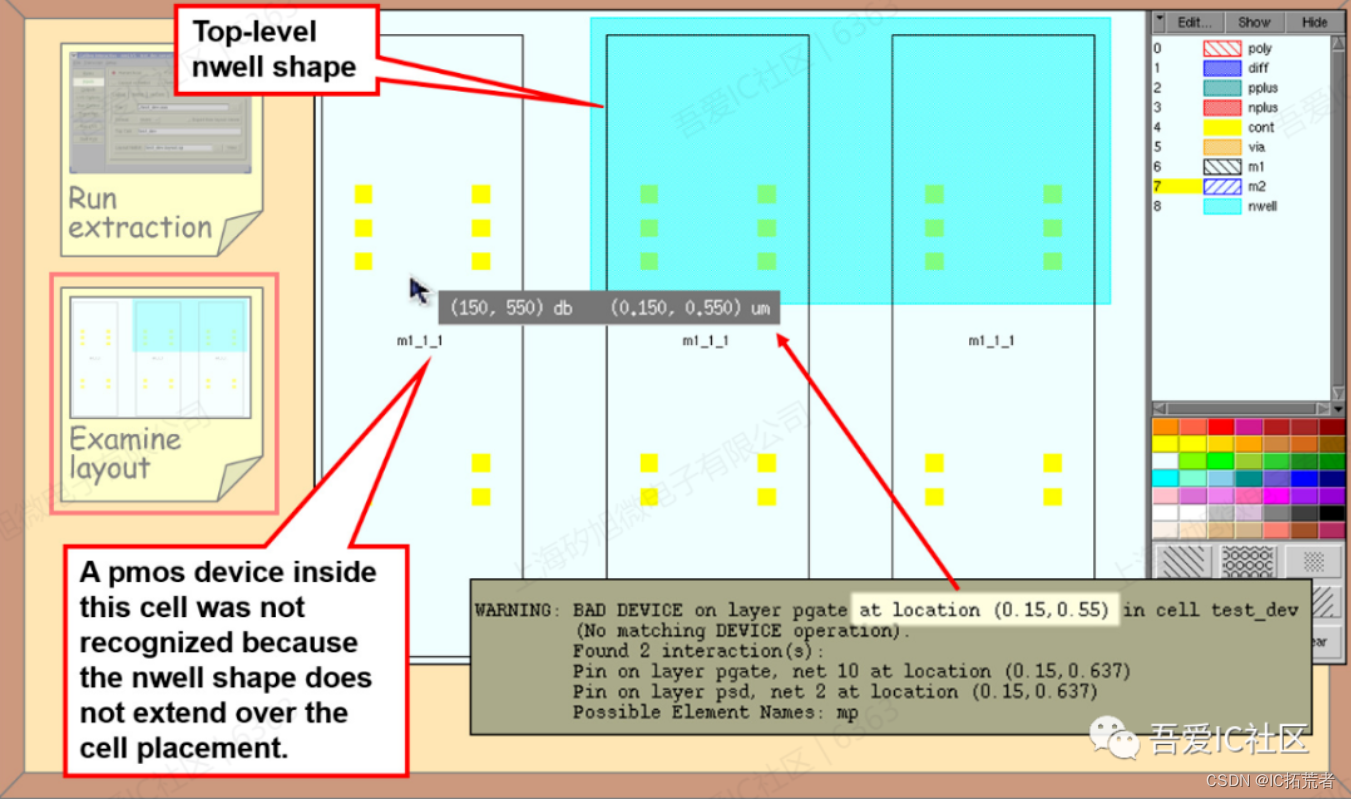

案例九:Seed Promotion With Bad Devices

如果出现这种LVS错误,首先需要在layout抽取后的spice netlist中搜索"SEEDPROM"关键词。

如果有,我们首先检查LVS下面的选项,是否已经设置成YES。

LVS PUSH DEVICES YES

https://alidocs.dingtalk.com/i/nodes/xdqZp24KneBJzg1AB9ao8vyb7RA0Nr1E?doc_type=wiki_doc&dontjump=true&utm_medium=main_vertical&utm_scene=team_space&utm_source=search# 「calibre-lvs-option解释」

在这个案例中,这个PUSH DEVICES的选项已经是YES了。通过进一步分析发现存在一个device没有被Nwell盖住的情况。

好了,今天的内容分享就到这里。另外,因为公众号更改推送规则,小编分享的每篇干货不一定能及时推送给各位。为了避免错过精彩内容,请关注星标公众号,点击“在看”,点赞并分享到朋友圈,让推送算法知道你是社区的老铁,这样就不会错过任何精彩内容了。

如果你想和小编有更进一步的沟通交流的机会,欢迎加入小编知识星球,让我们一起学习成长,共同进步。相信在这里能让你成就一个更完美的自己。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 使用antd design pro 及后端nodejs express 结合minio进行文件的上传和下载管理

- 详解如何撰写一个基础的技术交底书

- 迅为RK3588开发板编译 Buildroot单独编译图形化界面(编译 buildroot)

- 为突发事件提供高现势性数据支撑!大势智慧助力中山市2023应急测绘保障演练举行

- 【Python】dbf批量转为excel(非arcpy和arcpy转法)

- C#中使用OpenCV的常用函数

- 细谈Type-C Port的Data Role、Power Role | 乐得瑞科技

- 软件测评中心▏性能测试之压力测试、负载测试的区别和联系简析

- JS本地持久化

- 蛋白表达|酵母蛋白表达-卡梅德生物