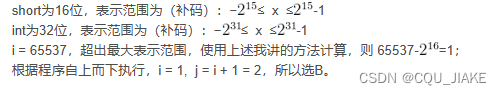

1.4补码范围,溢出,补码加减法、加法器、竞争与冒险、杂项

正数三码合一

负数的原码有1的符号位,反码为除了符号位以外全部取反,补码在反码的基础上再加1

移码的符号位中0表示负数,1表示正数,简单来说,原码的补码数值位不变,符号位取反就是移码。

对于8位寄存器:

原码表示范围为 -127-127,即1111 1111~0111 1111

反码表示范围为 -127-127,即1000 0000~0111 1111

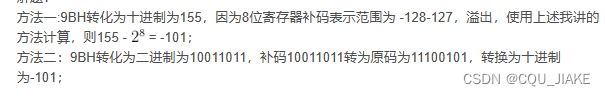

补码表示范围为 -128-127,即1000 0000~0111 1111

移码表示范围为 -128-127,即0000 0000~1111 1111

补码范围比原码以及反码,在负数上要大1

2.数据溢出:

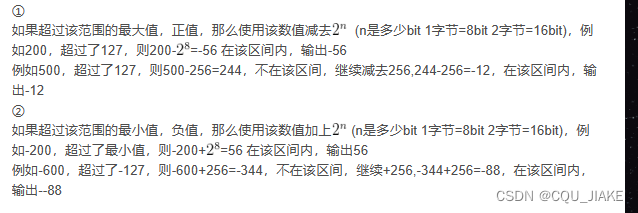

方法总结:

是直接减去最大的位数,?

①

如果超过该范围的最大值,正值,那么使用该数值减去 ?(n是多少bit 1字节=8bit 2字节=16bit),例如200,超过了127,则200-=-56 在该区间内,输出-56

例如500,超过了127,则500-256=244,不在该区间,继续减去256,244-256=-12,在该区间内,输出-12

②

如果超过该范围的最小值,负值,那么使用该数值加上 (n是多少bit 1字节=8bit 2字节=16bit),例如-200,超过了最小值h-344+256=-88,在该区间内,输出--88

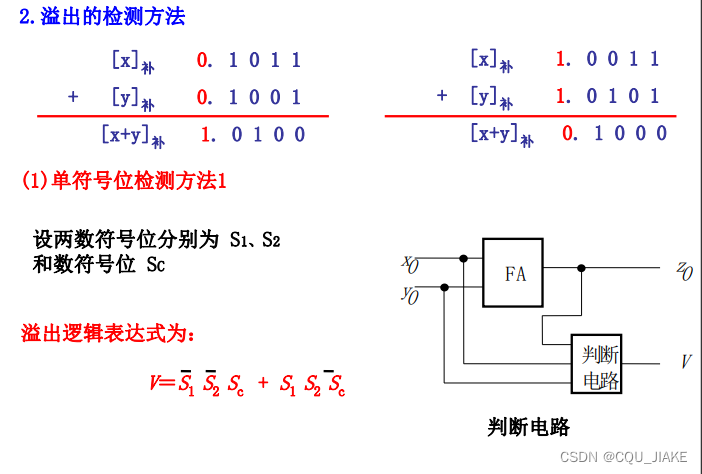

溢出检测

就是说,两个正数相加最后只能是正数,两个负数相加最后只能是负数,如果00,最后结果是1,或者11,最后是0,就是溢出了?

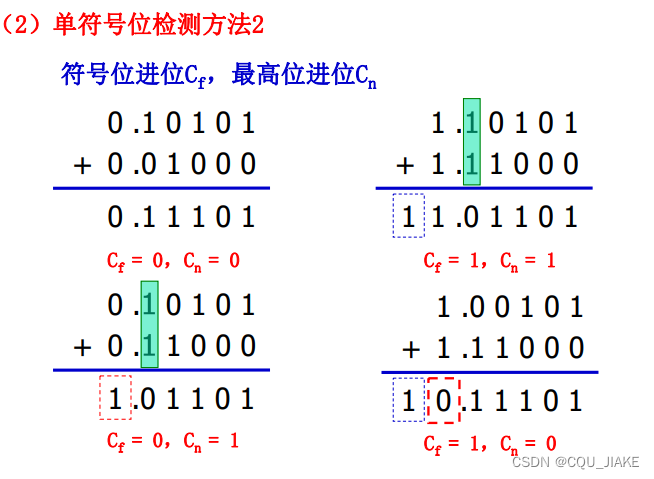

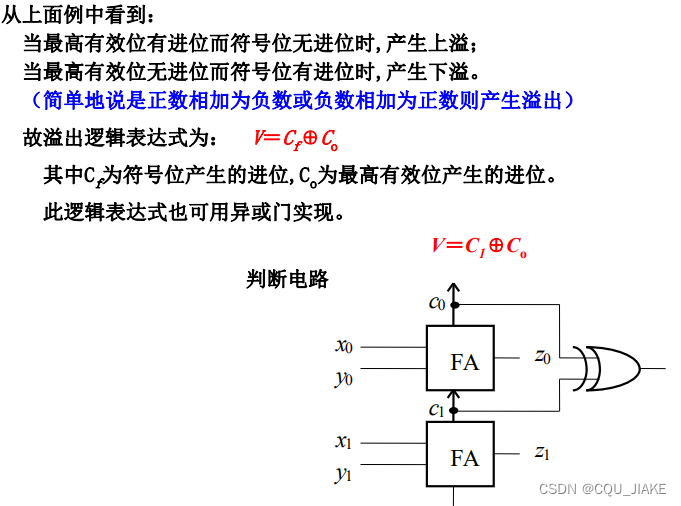

最高位有进位而符号位无进位,说明出现了两个正数相加为负数,就产生了上溢

最高位无进位,而符号位有进位,说明两个负数相加为正数,产生了下溢?

?

?

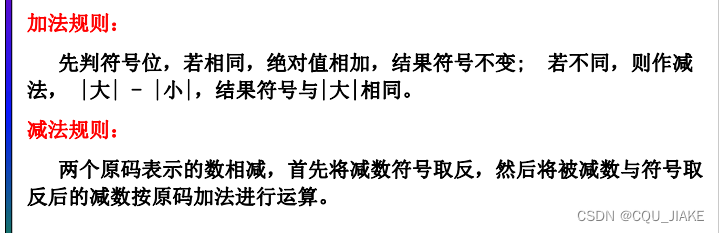

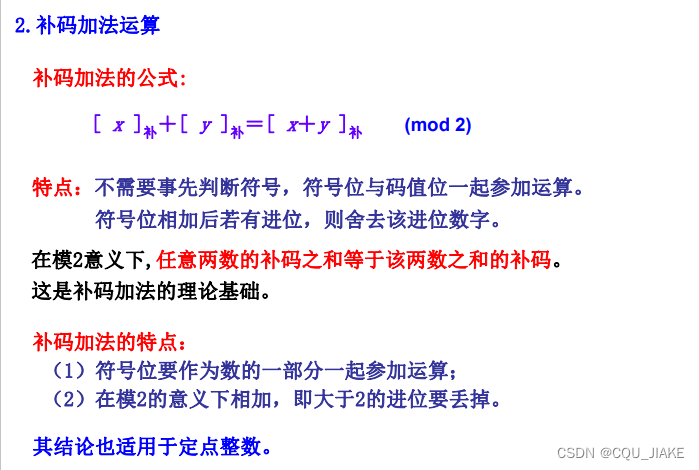

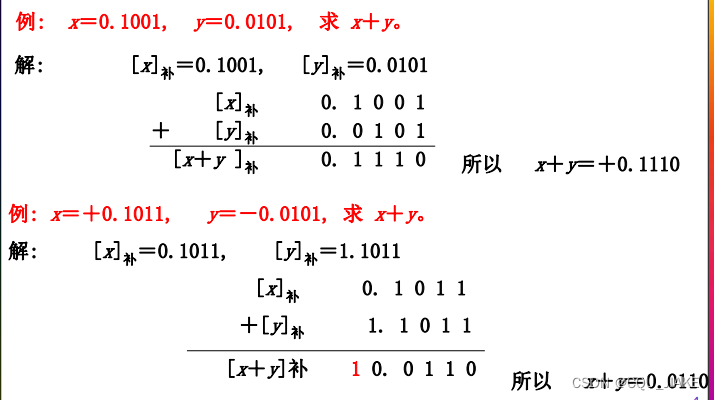

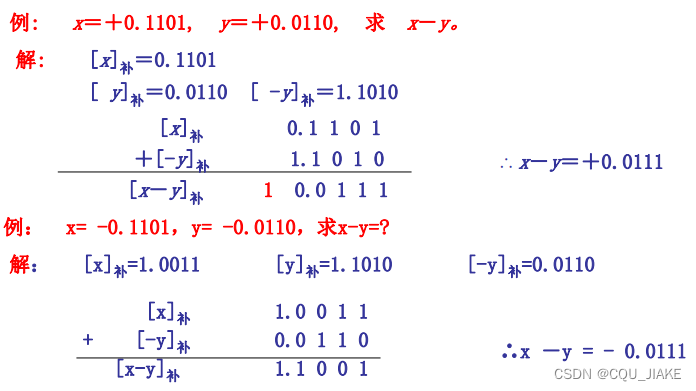

补码加减法?

?

?

?

?

?

?

补码运算,符号位参与运算?

就是先让减数变一下,变成加法,然后求补码,进行运算,最后运算结果把最高位转化成符号(如果有1的话)

?

?

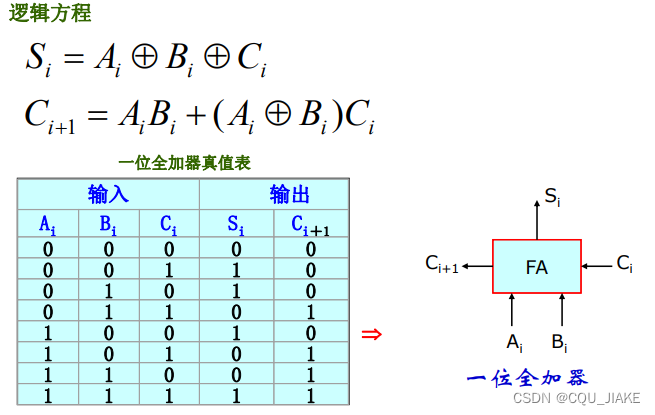

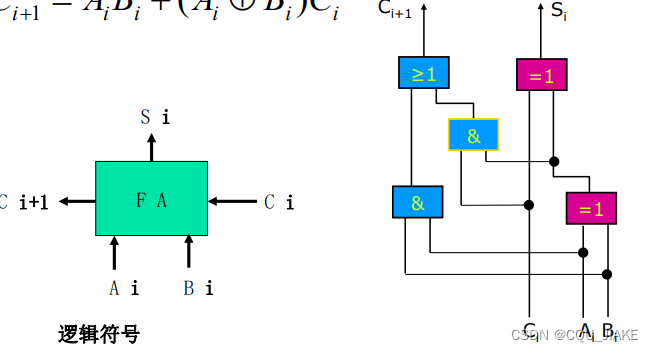

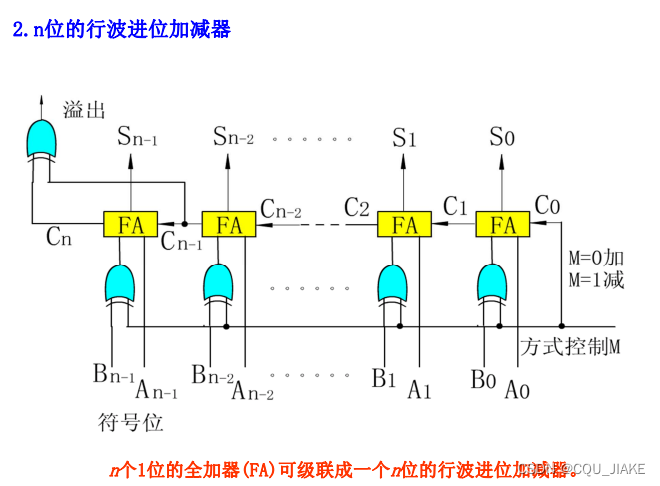

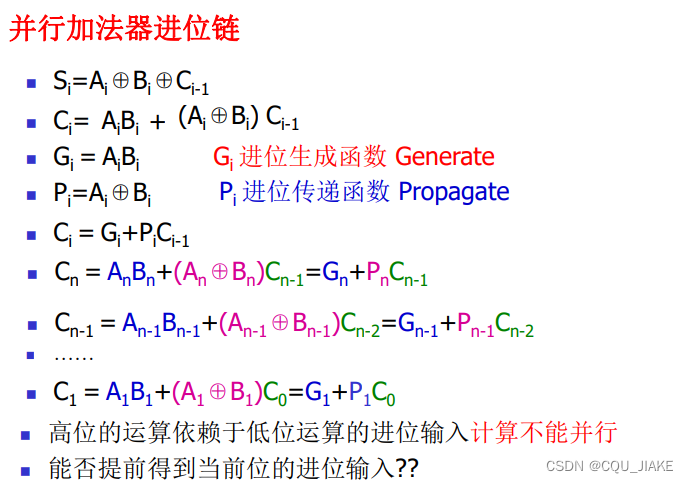

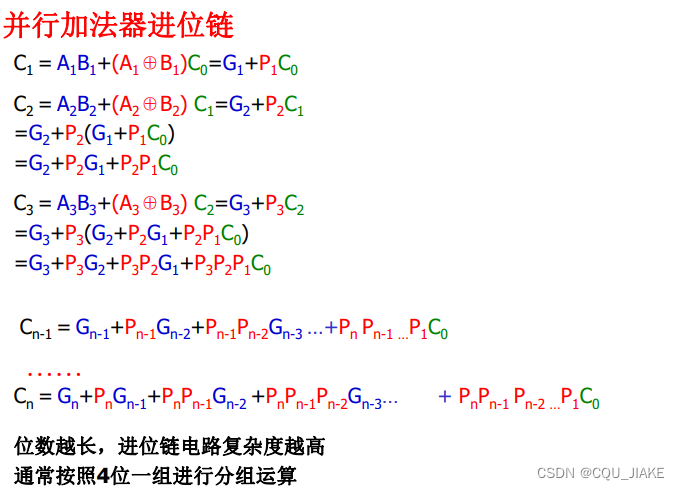

?加法器

CI是说进到本位上的进位,CI+1是进到下一位上的进位,此位的保留位为该位两数相加,再加上进位CI

对于下位进位,就是三个数里,有至少两个就行

这个C式子也可以表达这一种情况,AB+AC+BC,用那个式子可以节省资源,首先A异或B是省不掉的,如果不利用,用那个,得额外用三个与门,两个或门,而用了后,就可以只用两个与门,一个或门

注意逻辑表达式里并没有消掉这一说法,如A+AB=A,并不意味着AB=0,这里同理

AC+BC≠A异或B再与上C

输入三个信号,进位信号CI,AI,BI,出来两个信号SI,CI+1?

?

?

》1的门是或,=1的门是异或?

?

?

?

?

?

?

?

?

?

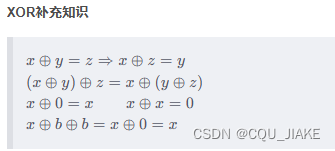

异或:A?B=AB′+A′BA?B=AB′+A′B

同或:A?B=AB+A′B′A?B=AB+A′B′

异或与同或互为反运算。?

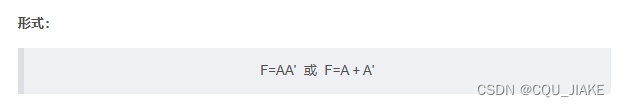

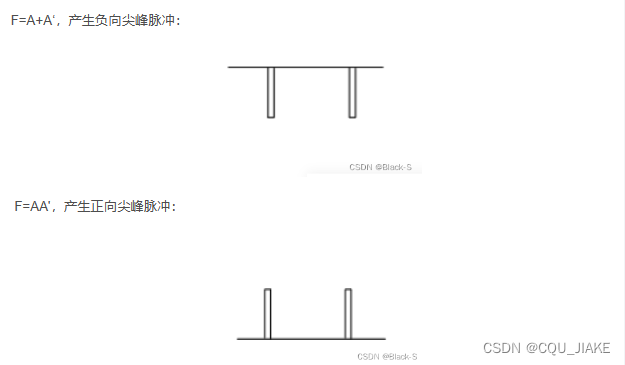

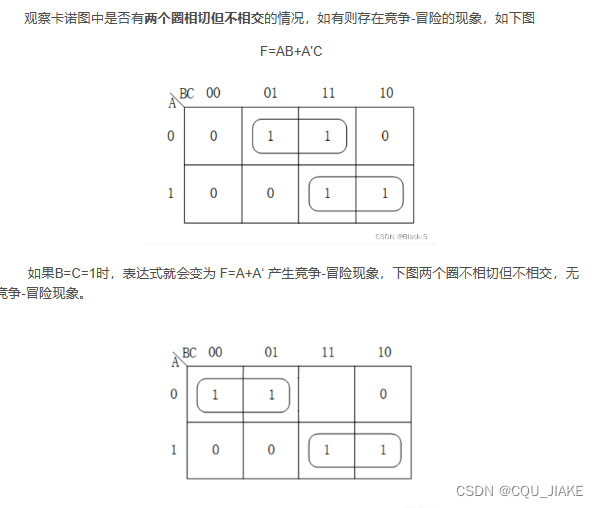

竞争与冒险

在组合电路中,某一输入变量经过不同路径传输后,到达电路中某一汇合点的时间有先有后,这种现象称为竞争;由于竞争而使电路输出发生瞬时错误的现象叫做冒险。由于竞争产生的毛刺叫做冒险

?

?

?

?

时序逻辑电路中通常包含组合电路和存储电路两个部分??

在同步电路中,由于所有触发器都在同一时钟操作下动作,而在此之前每个触发器的输入信号已处于稳态状态,因而可以认为不存在竞争现象。因此,一般认为存储电路的竞争—冒险现象仅发生在异步时序电路中。

竞争不一定有冒险,但冒险一定会有竞争

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

画状态转移表,就是先把现态量都给穷举出来,此时次态分量都还是未知的,然后依据状态转移方程求出各个次态分量的情况?

触发器联通的是某个状态分量现态与次态之间的关系

Q1,Q1次态与Q1现态之间的关系

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!