数字集成系统设计——物理设计

发布时间:2024年01月12日

目录

一、布局规划

1.1 规划

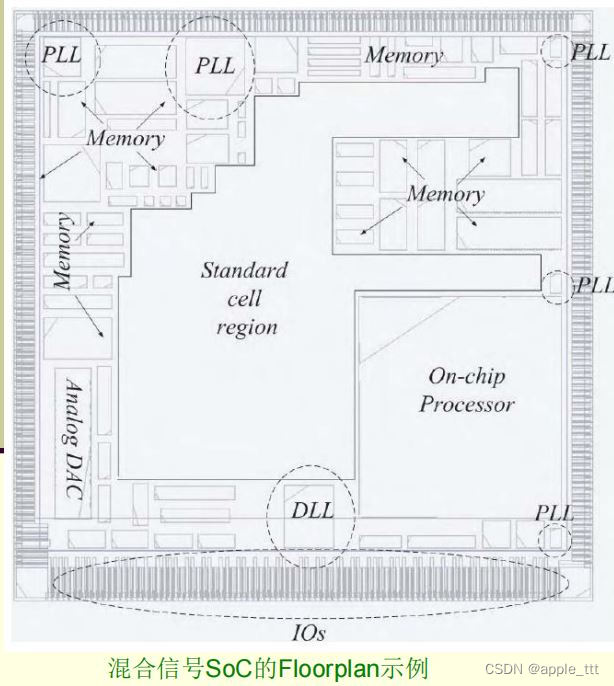

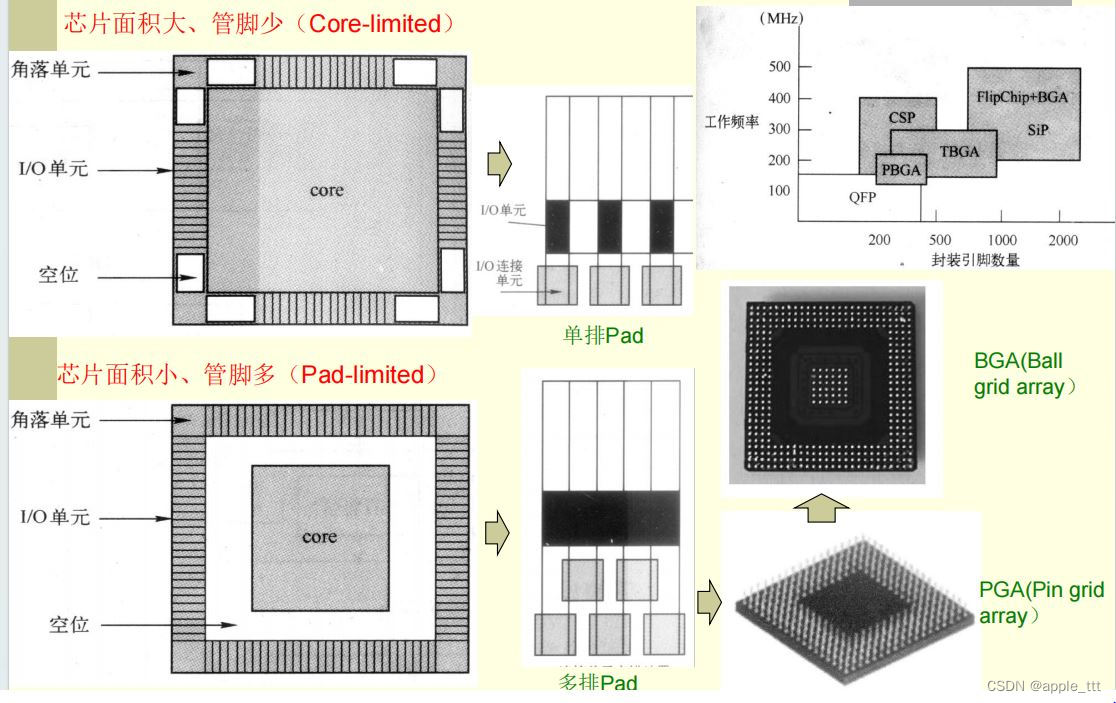

????????版图布局规划(Floorplan):确定各个电路模块在版图上的分布位置以及I/O端口沿周边的布置等。我们以以下的一个SoC芯片的布局规划为例:

1.2 I/O单元

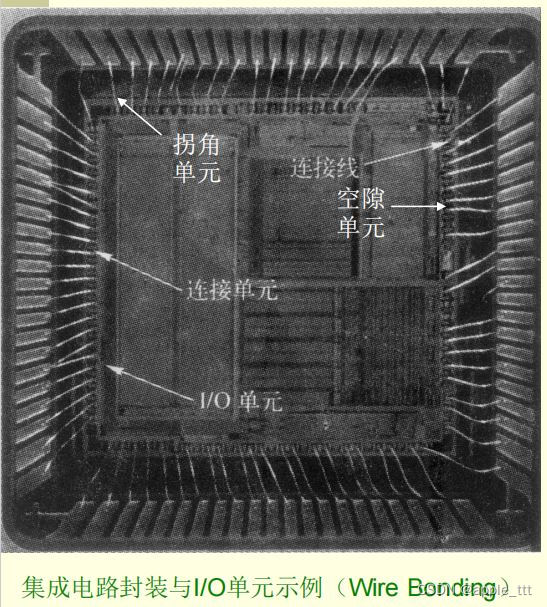

????????我们以下图为例进行介绍:

- I/O单元:输入接口电路、输出驱动电路、电平转换电路、静电放电(ESD,Electrostatic Discharge)保护电路等。

1.3 电源网络

1.3.1 要求

????????芯片供电网络的设计应保证芯片工作时电源线和地线上的压降(IR Drop)和开关浪涌不会超过规定的范围,同时避免因电流分布不均造成的热点(hot spot)和电迁移(EM,electro-migration)问题。

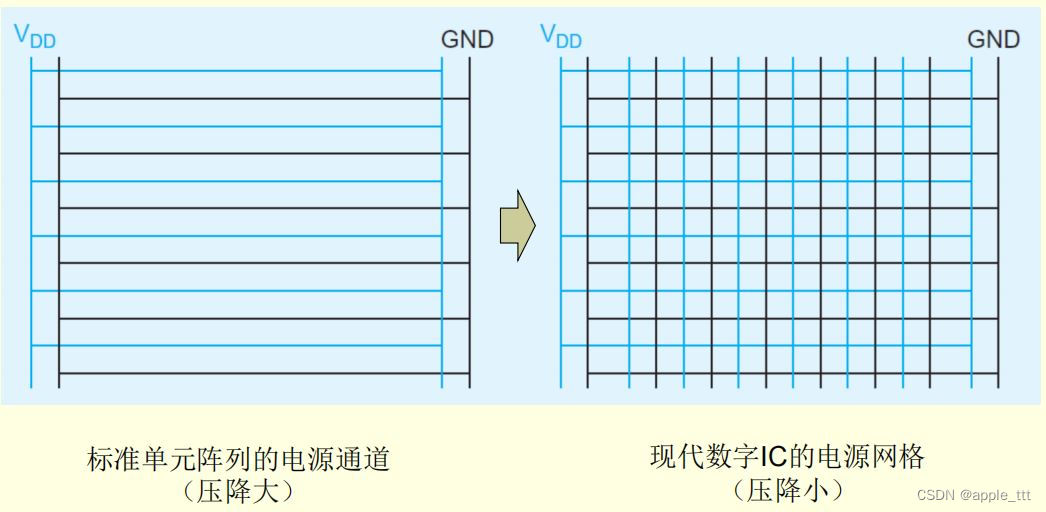

1.3.2 网络架构

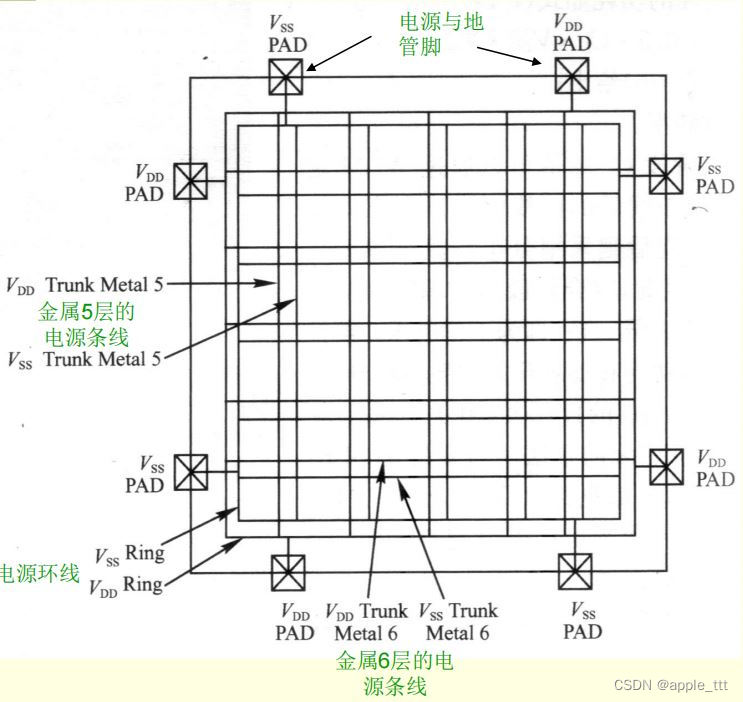

- 电源网格由内部的条线(strip)和四周的环线(ring)组成。如有宏单元,则其四周也有环线

- IR Drop一般要求不超过±5%,其中内部约±3%,I/O单元和电源环±1%,封装管脚与键合线±1%。

- 增大电源网格的密度、加粗电源线、增加电源线通孔数量、增加电源与地管脚数量,都有利于降低IR drop。

- 位于相邻互连层的电源及地线尽可能相互垂直。

- 数字电路多使用网格(多点接地),模拟电路使用环状或树状(单点接地)。

1.3.3?混合信号芯片示例

1.4 布局

- 单元布局优化(Placement & Optimization)根据时序收敛要求,对单元的布局进行优化调整,确定门级网表中所有标准单元及I/O单元的精确位置

- 布局的优化目标是在确保时序收敛的前提下,尽量缩小面积和缩短互连线

- 自动布局依赖各种几何算法和强大的运算能力(所需机时随芯片面积的增加得比线性更快)

- 先自动布局,再人工调整

? ? ? ? 下图是一个由129个标准单元和15个I/O脚构成的数字芯片布局示例

二、时钟分布

2.1 时钟偏斜

- 时钟偏斜(Skew)是指时钟源点到达不同寄存器时钟引脚的时间差,通常由不同时钟路径的长度及负载导致延时不同所致

- 若接收数据的时钟沿早到(△<0)/晚到(△>0),就会产生建立时间/保持时间的冲突;如果发送数据的时钟沿早到(△>0)/晚到(△<0),就会产生保持时间/建立时间的冲突。因此,实际设计时会保留少许的时钟偏移量,既保证设计电路的健壮性,又能得到更接近实际情况的时序分析结果

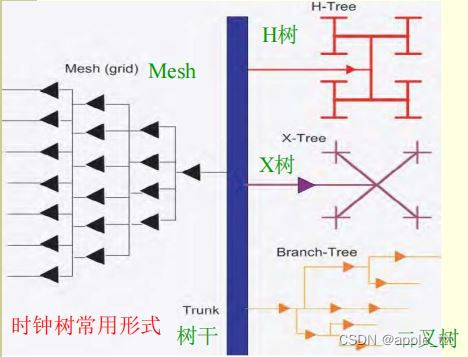

- 前端设计通常会人为设定所需的少许时钟偏斜量,后端设计会通过设计专门的时钟树或时钟网格结构来保证时钟偏斜在规定的限度内

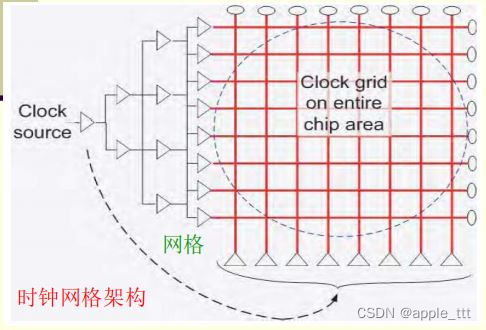

2.2 时钟分布网络

????????时钟分布网络要确保所有单元获得的时钟信号具有相同的相位,同时应尽量减少时钟线的寄生电容和寄生电阻,以降低其对延迟和功耗的贡献,普通电路(如ASIC)多采用时钟树(Clock tree)结构,高性能芯片(如片上处理器)才采用时钟网格(Clock grid)。

?

?

?

2.3 时钟树综合?

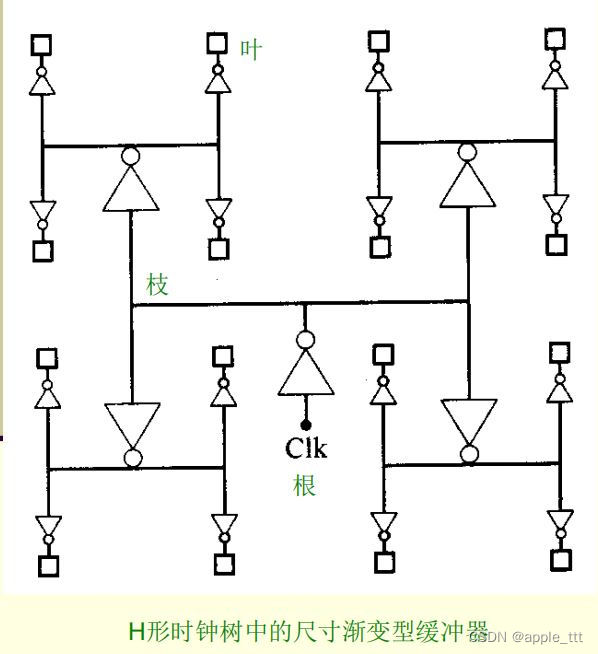

- 时钟树综合(Clock Tree Synthesis)是指使用EDA工具自动生成时钟树并实现时钟收敛,包括了时钟缓冲器的插入(主要途径)和时钟信号的布线

- 将缓冲器分散在整个时钟网络的不同层次中,可根据每层不同的驱动要求,设计不同驱动强度的缓冲器,而且连线RC引起的延迟不均衡亦可通过设计位于不同层次、具有不同级数及大小的驱动器来弥补

2.4 时钟树收敛

????????时钟树收敛是指时钟树的平均延迟达到最小,而且时钟偏斜在规定的限度以内

三、布线与参数提取?

3.1?布线(Routing)

- 布线是根据网表文件给出的单元互连关系和布局给出的单元位置,确定连接单元的线网

- 布线设计的目标是在保证布通率的前提下,使所有连线尽量短、通过的层数尽量少(目的是减少延时和功耗,提高可靠性),平行走线尽量少(目的是减少串扰和寄生电容),符合设计规则(目的是符合工艺要求)

- 先总体布线(Global Routing),确定所有线网的路径分配方案;再详细布线(Detailed?Routing),确定金属线和通孔的精确位置

- 先利用EDA工具完成自动布线,再人工布线进行补充和优化

- 规划和布局对布线的成败以及优化程度有关键性的影响

3.2?布线规则示例

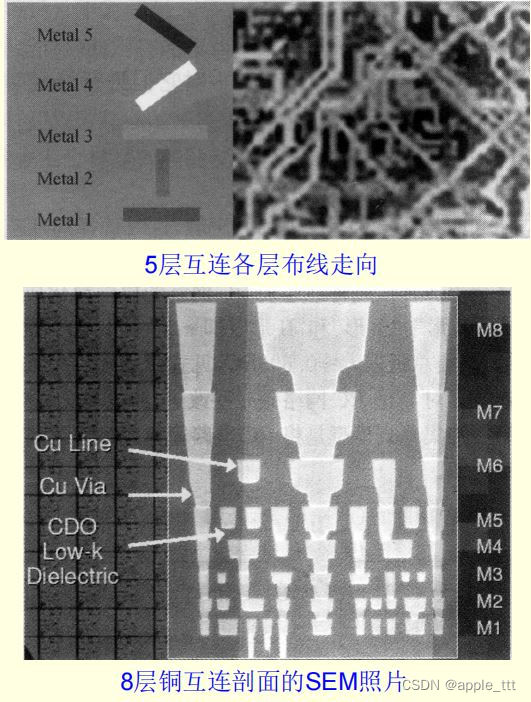

- 相邻两个互连层导线的走向相互交叉,有利于提高布通率并抑制串扰

- 在65nm及以下芯片中,常建议顶层金属按45°方向走线,有利于减少延迟、功耗等

- 互连线顶层的宽度和周距(pitch)设得较大,底层的宽度和间距较小,但并非线性递进

3.3 参数提取?

3.3.1 必要性

- 进入深亚微米尺度(0.25um)之后,互连对芯片延迟的贡献已显著超过有源器件门电路的贡献,而互连延迟取决于互连的寄生参数,故互连寄生参数的精确提取(Parasitic extraction)是完成时序分析验证的前提

- 互连的寄生参数取决于其几何参数(长、宽、厚、间距、空间分布),因此只能在布局布线后提取

- 器件延迟由标准单元的延迟以及总负载电容决定,因此参数提取主要是提取互连线的寄生参数(对于数字电路主要是电阻和电容,对于模拟电路特别是射频电路才需要考虑电感)来计算互连延迟

3.3.2 流程

3.3.3 范围

?

?

3.3.4 延迟计算

3.4 ECO??

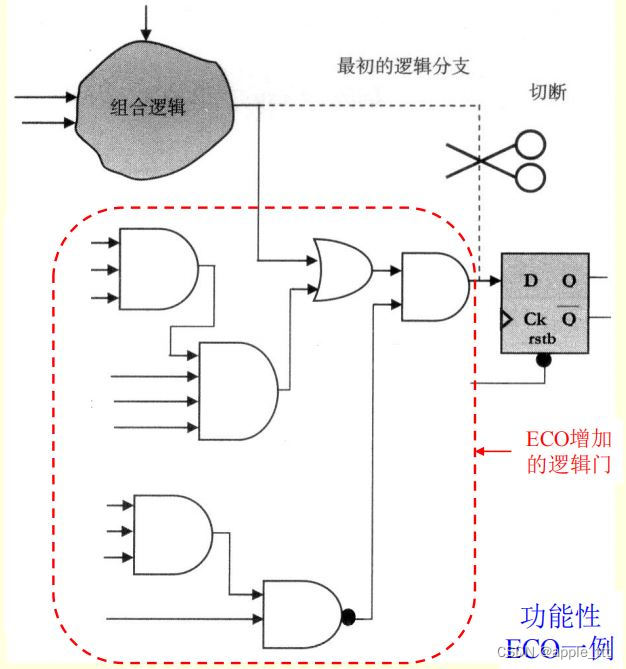

- 工程更改指令ECO(Engineering Change Order)主要是在布局布线后发现个别路径有时序或逻辑错误时,基于EDA工具对设计进行小范围、快速的修改

- 相对于传统的推倒重来式的后端设计修改流程,基于ECO的设计修改流程缩短了设计时间,修改结果具有可预测性,降低了后端设计失败的风险

- 修改布线:只能修正时序、串扰、负载不匹配等错误,称为非功能性ECO

- 修改网表:通过追踪逻辑锥(即与错误有关的上级逻辑),添加或修改少许逻辑门和触发器来纠正逻辑错误(右图为一例),称为功能性ECO,最为常用

- 修改RTL代码:如果修改涉及数百个触发器和数百个逻辑门,最好修改RTL代码并重新综合,这已经脱离ECO范畴了

文章来源:https://blog.csdn.net/apple_53311083/article/details/135556361

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 35岁了,怎么办?

- 勒索家族瞄准制造业,亚信安全发布《勒索家族和勒索事件监控报告》

- SSL VPN移动安全接入策略

- 全网最全pytest大型攻略,单元测试学这就够了!

- go语言学习计划。

- 常用算法-冒泡算法

- C语言K&R圣经笔记 5.3指针和数组 5.4地址运算

- Java八股文面试全套真题【含答案】- SpringCloud Alibaba篇

- java.security.invalidkeyexception: illegal key size or default parameters

- dpo笔记