Verilog刷题笔记16

题目:

Since digital circuits are composed of logic gates connected with wires, any circuit can be expressed as some combination of modules and assign statements. However, sometimes this is not the most convenient way to describe the circuit. Procedures (of which always blocks are one example) provide an alternative syntax for describing circuits.

For synthesizing hardware, two types of always blocks are relevant:

Combinational: always @(*)

Clocked: always @(posedge clk)

Combinational always blocks are equivalent to assign statements, thus there is always a way to express a combinational circuit both ways. The choice between which to use is mainly an issue of which syntax is more convenient. The syntax for code inside a procedural block is different from code that is outside. Procedural blocks have a richer set of statements (e.g., if-then, case), cannot contain continuous assignments, but also introduces many new non-intuitive ways of making errors. *(*Procedural continuous assignments do exist, but are somewhat different from continuous assignments, and are not synthesizable.)

For example, the assign and combinational always block describe the same circuit. Both create the same blob of combinational logic. Both will recompute the output whenever any of the inputs (right side) changes value.

assign out1 = a & b | c ^ d;

always @(*) out2 = a & b | c ^ d;

我的解法:

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign=a&b;

always @(*) out_alwaysblock=a&b;

endmodule

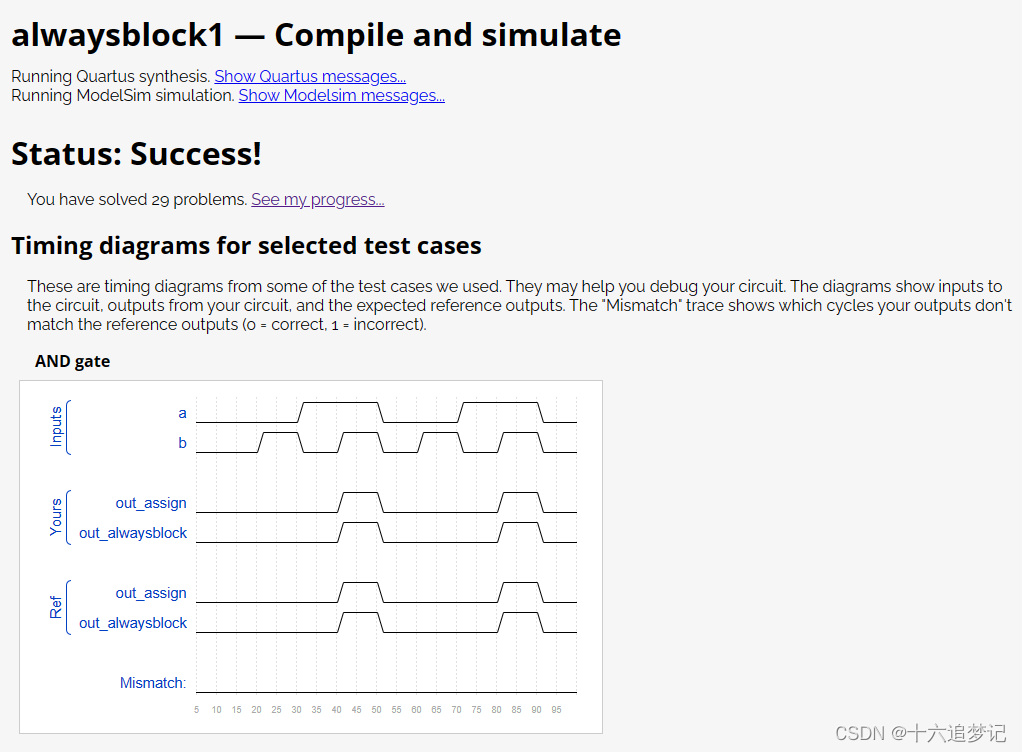

结果正确:

此题考查两种赋值方法:

两种类型:

output wire out_assign

output reg out_alwaysblock

对应两种不同赋值方法:

assign out_assign=a&b;

always @(*) out_alwaysblock=a&b;

关于 wire 与 reg 的说明:赋值语句的左侧必须是 net 类型(例如,wire),而过程赋值的左侧(在 always 块中)必须是变量类型(例如,reg)。这些类型(wire 与 reg)与合成的硬件无关,只是 Verilog 用作硬件仿真语言时遗留下来的语法。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Docker(三)使用 Docker 镜像

- MATLAB中padarray函数用法

- protobuf-Java使用.md

- 【工业智能】音频信号相关场景

- C# 图解教程 第5版 —— 第21章 异步编程

- 【日积月累】Java Lambda 表达式

- python--re库

- 智能环境与可持续发展:人工智能为地球未来添翼

- 如何快速水出人生中的第一篇SCI系列:深度学习目标检测算法常用评估指标——一文读懂!

- 【前端素材】同城服务分类手机APP页面的设计实现