南京观海微电子----时序分析基本概念(一)——建立时间

1.?概念的理解

以上升沿锁存为例,建立时间(Tsu)是指在时钟翻转之前输入的数据D必须保持稳定的时间。如下图所示,一个数据要在上升沿被锁存,那么这个数据就要在时钟上升沿的建立时间内保持稳定。

建立时间是对触发器而言,以能够稳定准确的锁存或者触发为目的,对其输入数据信号保持稳定的时间要求。

2.?简单的实例

以两个级联寄存器为例。

时钟通过CLK PIN管脚输入,到达第一个寄存器的时钟端口经历的时延为Tclk1,到达第二个寄存器的线上时延为Tclk2。

第一个寄存器从时钟进入时钟端口驱动寄存器到寄存器输出数据的延时为Tco,Tco为寄存器内部的时延。

数据从第一个寄存器Q端口输出,经历Tdata延时到达第二个寄存器的数据输入端。Tdata可能包含路径上的延时以及引入的组合逻辑电路导致的延时。

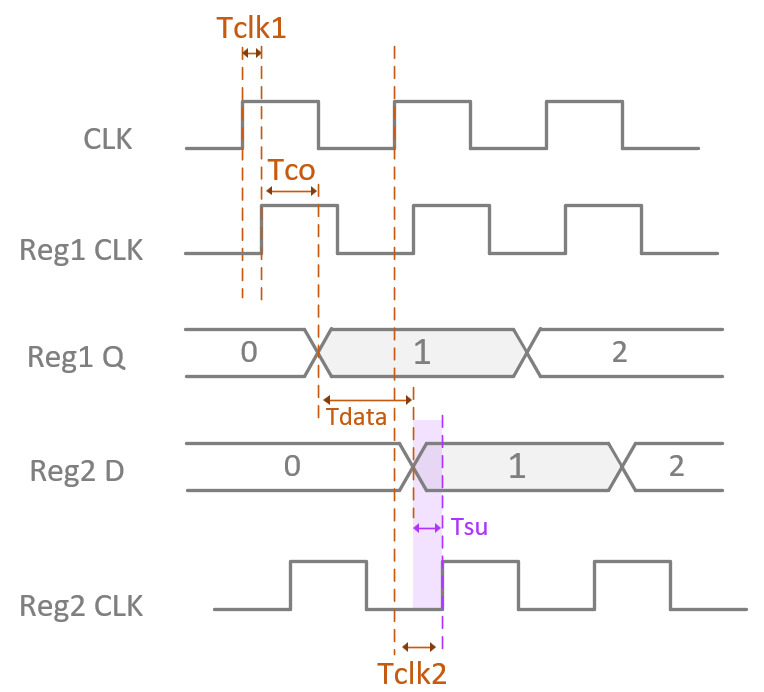

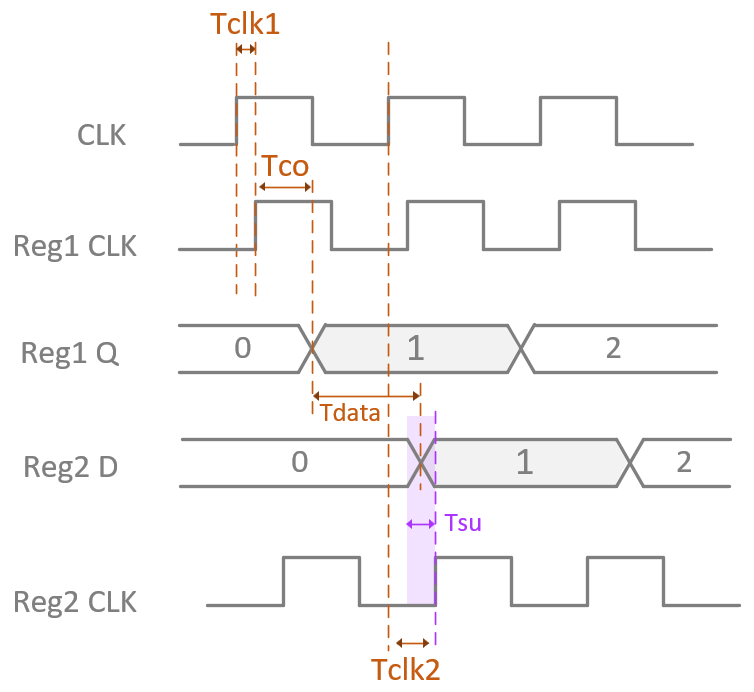

时序图如下图所示:

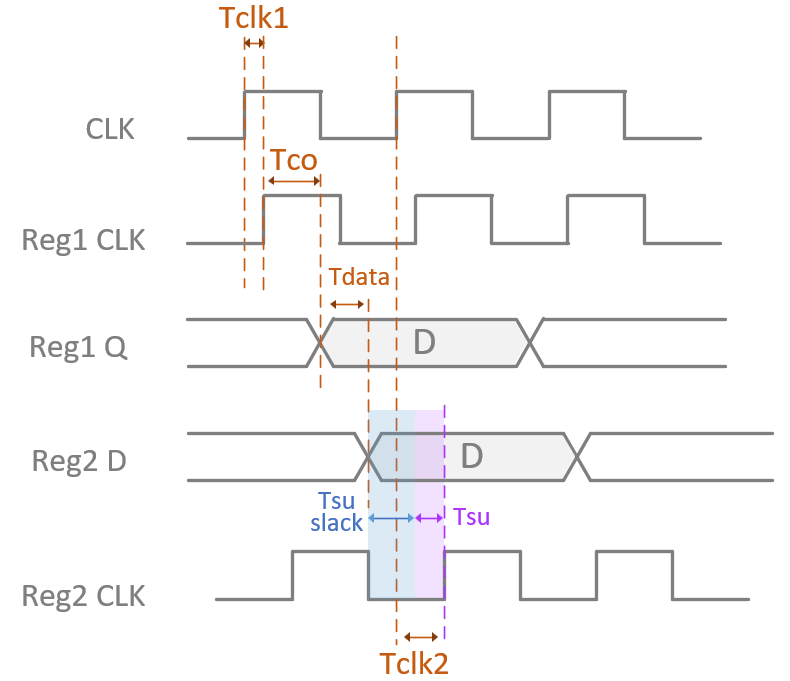

图中,紫色区域为Tsu需要的时间,蓝色的区域为富余的建立时间(Tsu slack)。

如果由于Tdata时间较长,使得Tsu slack为0,但Reg2的D输入口数据仍然比下个时钟上升沿提前Tsu时间到达,则Reg2?寄存器仍然能稳定的采集到输入数据“1”,如下图所示。

如果由于组合逻辑过于复杂使得Tdata时间过长,使得Tsu slack为负值,Reg2的D输入口数据比下个时钟上升沿提前到达的时间不足Tsu时长,则Reg2?寄存器不能稳定的采集到输入数据“1”,而是个亚稳态,如下图所示。

3.?时序计算公式

由以下时序图,我们可以得到建立时间的计算公式:

Tsu_slack = Tcycle + Tclk2 - Tsu - (Tclk1 + Tco + Tdata);

其中Tcycle为CLK一个时钟周期的时间。

例:如果已知Tcycle为10ns(即工作时钟100MHz)、Tclk1为3ns、Tclk2为2ns、Tdata为3ns、Tsu为0.5ns、Tco为1ns,则求Tcu_slack为多少?并计算该电路最高能工作的时钟频率是多少?

答:通过套用上面的公式可得

Tsu_slack = 10 + 2 - 0.5 - (3 + 1 + 3) = 4.5 ns

如果想计算该电路最高能工作的时钟频率,则可以将Tsu_slack设为0,反求下Tcycle:

Tcycle = 0 - 2 + 0.5 + (3 + 1 + 3) = 5.5 ns (即181.8 MHz)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- KnowLM知识抽取大模型

- 【第十八节】变量与运算符-算术运算符的使用

- LeetCode2.AddTwoNumbers两数相加(Java可运行,带测试用例)

- 半监督学习 - 半监督生成对抗网络(Semi-Supervised GANs)

- 500强企业都是如何选择数据摆渡方式的?核心看这三点!

- 月子中心网站搭建的效果如何

- Linux开发工具——gdb篇

- C#,实用代码——运算符重载、泛型与加强版的数组Array

- 当在线教育流量预警时,我们还能从小程序挖掘

- 爬虫代理IP在电商行业的应用