vivado约束方法7

输出延迟

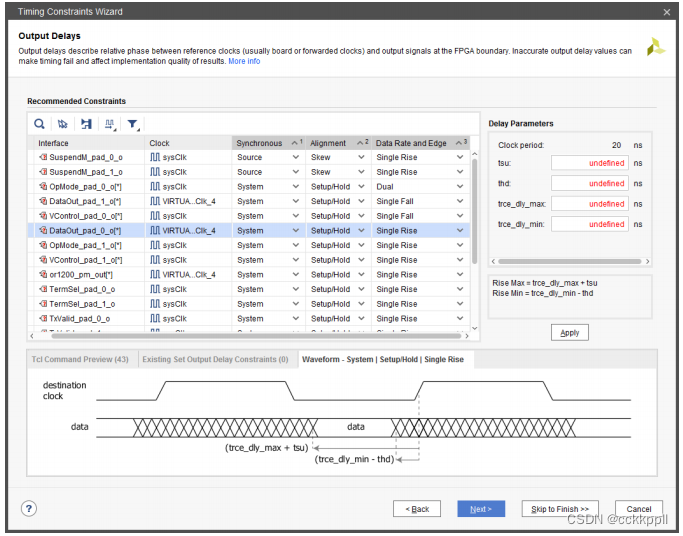

与“输入延迟”步骤类似,“定时约束”向导分析所有输出的路径端口,以识别其在设计内部的源时钟及其活动边缘。模板选择规则与输入延迟中描述的相同。下图显示了几个由向导提出并由用户部分编辑的输出约束。

对于每个约束,可以编辑三个特征,以便指定适当的与板上的实际接口时序相对应的波形:

?同步:描述时钟数据关系的性质(有关更多信息,请参阅输入延详细信息)。

?对齐:描述相对于活动时钟边缘的数据转换对齐。

?设置/保持:当基于指定模板延迟参数时,使用此设置

FPGA外部的数据有效窗口时序特性。

?偏斜(仅限源同步):当模板延迟参数为基于FPGA的输出引脚上的偏斜要求来指定。

?数据速率和边沿:描述受模板约束的活动时钟边沿。

参考时钟通常是板时钟,以下情况除外:

?板时钟和输出路径内部时钟具有不同的时钟周期。输出约束引用具有与内部相同波形的虚拟时钟时钟,从而以1个周期的路径要求来执行设置分析。虚拟的时钟是自动创建的。

?与板时钟相比,输出路径内部时钟具有负相移。向导使用虚拟时钟作为参考时钟。虚拟时钟是自动的以与板时钟相同的波形创建。此外,向导还指虚拟时钟和内部时钟之间的多周期路径约束,以调整默认分析为1个周期+用于设置的相移量。的组合虚拟时钟和多周期路径约束为Vivado提供了更简单的约束Design Suite计时器可处理

?已确定转发时钟,用于根据共享时钟对输出路径进行定时连通性转发的时钟必须在向导的第三步“转发”中创建时钟”,否则将使用板时钟或虚拟时钟作为输出延迟约束参考时钟。

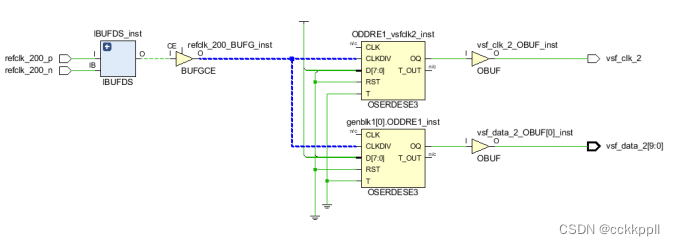

下图显示了输出源同步路径的基本示例及其7系列系列的转发时钟。两个ODDR/OSERDES实例都连接到相同的时钟网络(以蓝色突出显示)。已在上定义ck_vsf_clk_2生成的时钟vsf_clk_2输出端口。

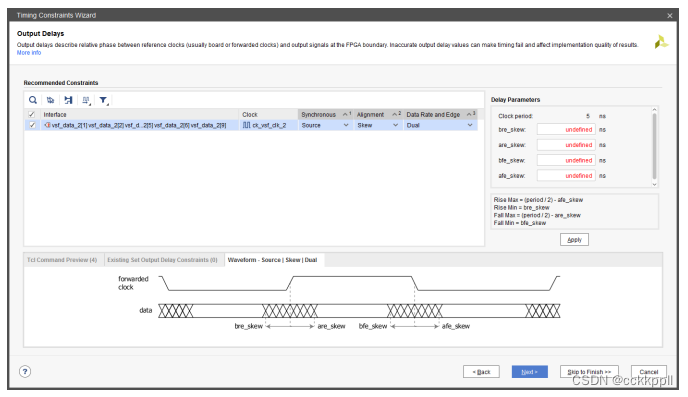

下图显示了向导中相应的约束。

选择正确的模板后,必须输入延迟参数值。加速在延迟参数输入任务中,您可以选择和编辑具有相同时钟的多个约束同时使用相同的模板。完成并应用约束后,可以查看在“Tcl命令预览”选项卡中显示相应的Tcl语法,或者您可以单击“下一步”继续进入下一步。只能在向导之外创建约束。

组合延迟

某些路径直接从输入端口传播到输出端口,而不会在内部捕获通过一个顺序单元对设备进行控制。如果输入端口同时连接到输出端口和顺序单元格,“定时约束”向导不建议使用组合约束在输入/输出端口对之间,因为输入端口在输入延迟步骤。

最终的组合路径延迟约束是:

?对于设置分析:虚拟时钟周期-最大输入延迟-最大输出延迟

?对于持有分析:0-最小输出延迟-最小输入延迟必须修改虚拟时钟周期,使其大于最大组合时钟周期所有受约束组合路径上的延迟约束。下图显示了延迟每个输入/输出端口对所需的条目。

输入和输出延迟约束都不会覆盖现有的延迟约束。如果给定端口具有对于同一时钟的多个延迟约束,所有约束的最小值为Vivado定时分析功能在保持分析过程中使用,也是设置过程中最大的一个分析填写完所有延迟条目后,可以单击“下一步”继续下一步。

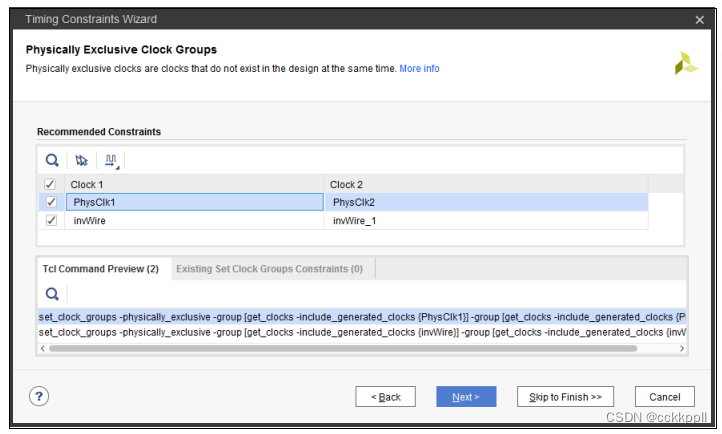

物理独占时钟组

物理排他性时钟是在同一源点上定义并在上传播的时钟同一个时钟树。下图显示了一个示例,其中两个主时钟定义在同一输入端口上。

虽然它们的重叠便于用一个设计和约束数据库,这些时钟及其子级生成的时钟永远不应该计时在一起“定时约束”向导可识别此类时钟并推荐时钟组约束,以防止对时钟域交叉路径进行不必要的时序分析,如图所示如下图所示。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 2024SIA上海国际轴承工业展览会 ▎参行业盛会 展轴研风采

- 从 “template1“ is being accessed 报错,看PG数据库的创建过程

- (C00147)基于SSM(非maven)的学生成绩管理系统-有报告

- 4-新建子模块(尝鲜)

- 【Java SE语法篇】9.抽象类和接口

- 支付宝沙箱环境配置结合内网穿透实现远程调试Java SDK接口

- @Autoware和@Resource区别

- IIS 和 WEB 站点文件夹权限配置,一个空间绑定10个域名

- Arduino串口测试

- 微信小程序-----wxss模版样式