仿真验证方法(3)——物理验证

发布时间:2024年01月13日

目录

?

一、物理验证的分类

? ? ? ? 对于物理验证,大致上可以分成以下的三种类型:

1、设计规则检查(DRC,Design Rule Check)

- 检查版图各掩膜层的几何参数是否符合代工厂给出的设计规则

- 检查错误类型:几何尺寸与设计规则不符

2、电气规则检查(ERC,Electronic Rule Check)

- 检查版图中是否存在没有电路意义的连接错误,但不涉及电路的行为检查

- 检查错误类型:元器件的开路或短路,浮空节点,无意义分支,无用器件等

3、版图-原理图一致性检查(LVS,Layout Versus Schematic,也叫原理图验证SV,Schematic Verification)

- 从版图提取出网表结构,以确认其是否与原始网表结构一致

- 检查错误类型:元器件数目不一致(如版图有、原理图没有),元器件类型不一致,节点数不一致

二、DRC

2.1 设计规则

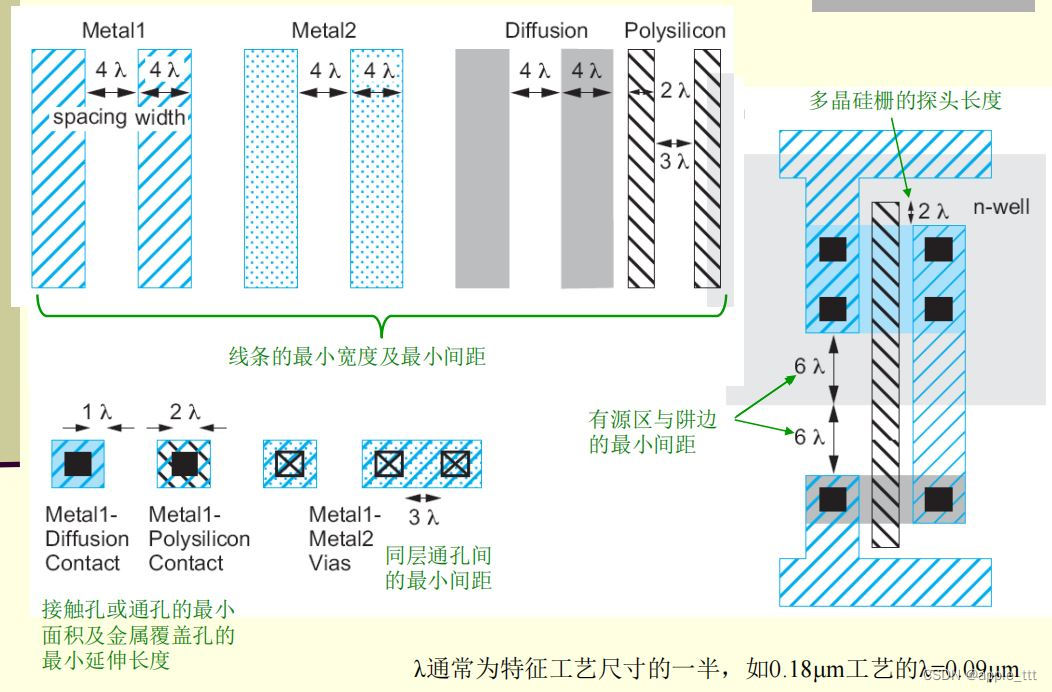

????????设计规则是版图设计必须遵守的几何规则(最小特征尺寸),由半导体代工厂提供,体现了制造工艺的物理限制。

2.2?规则示例

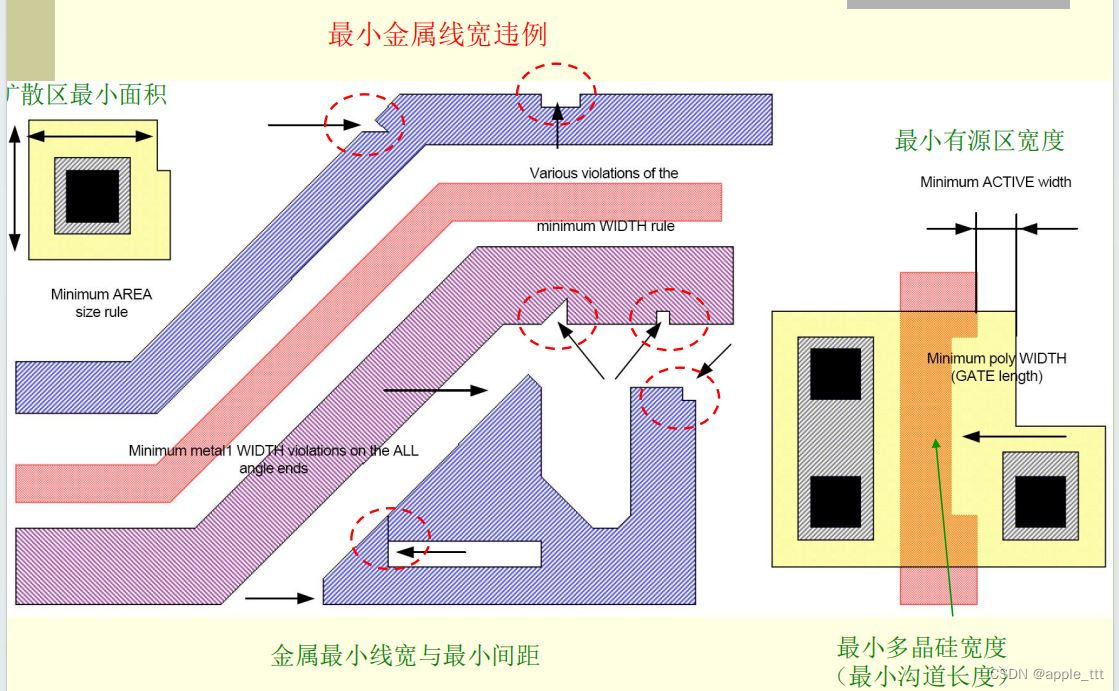

2.3?线宽违例

2.4?间距违例

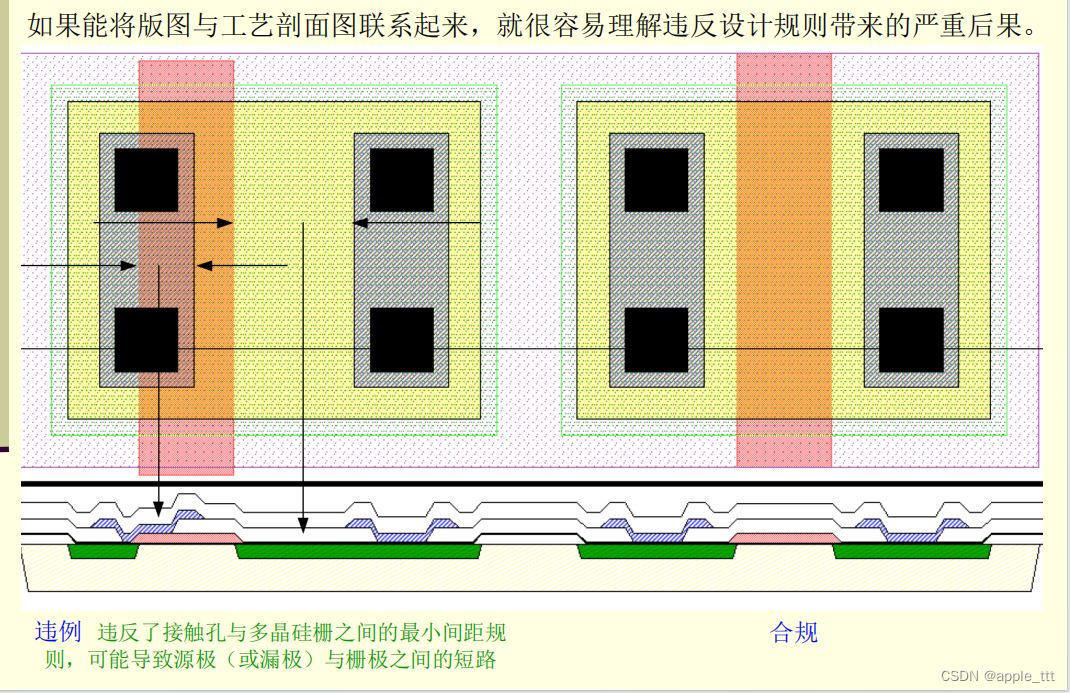

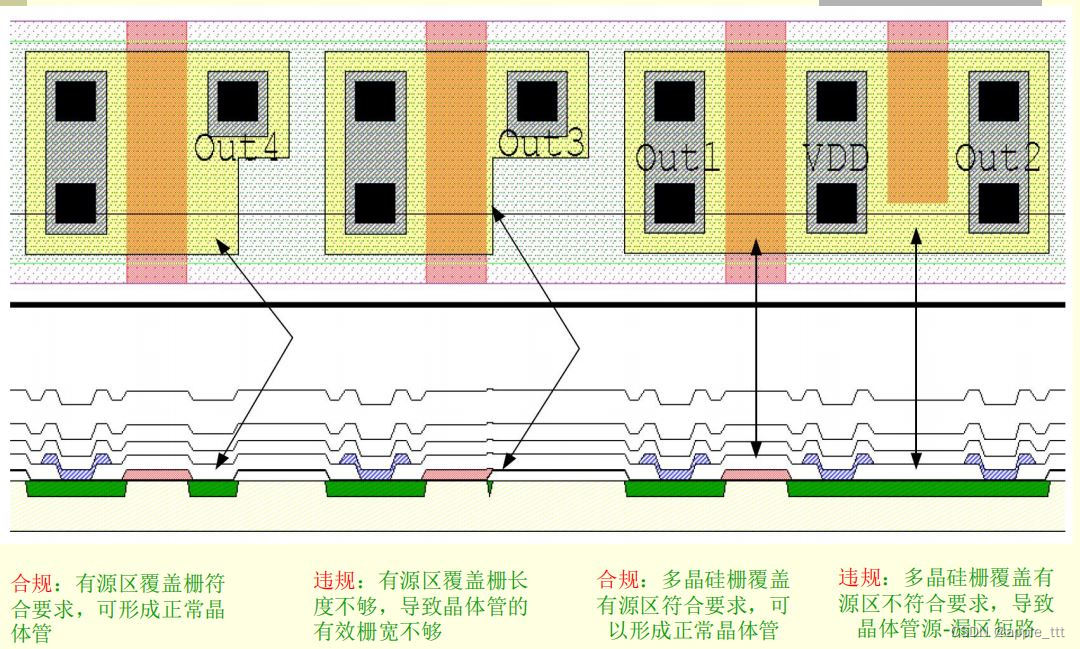

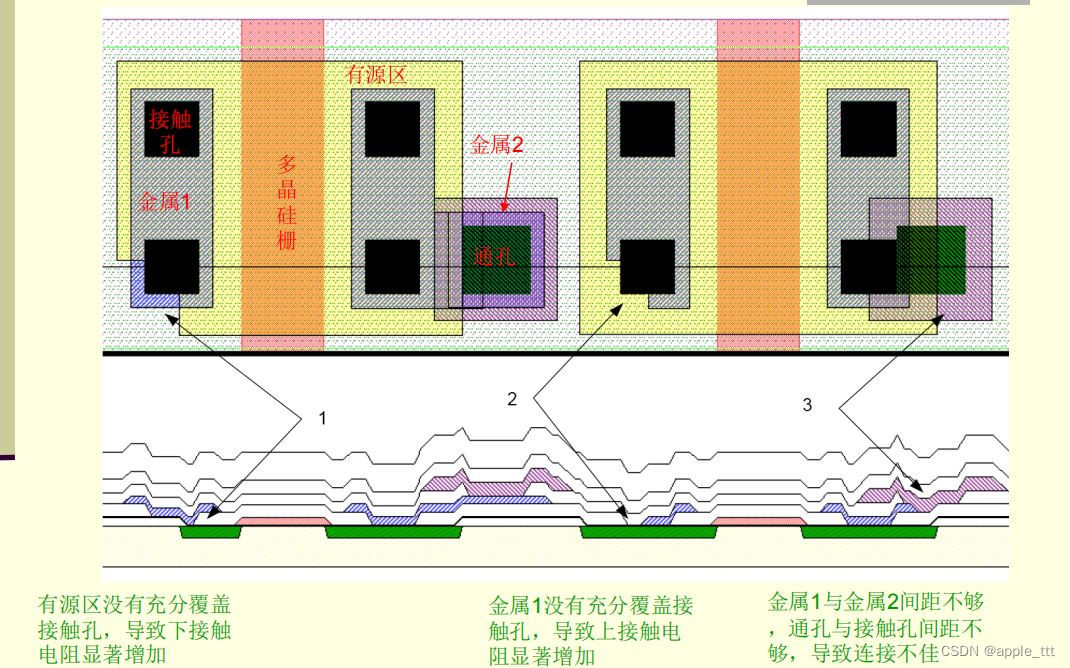

2.5?交叠违例

?

?

三、金属覆盖图形密度检查

????????化学机械抛光(CMP)与片内均匀性要求每一层互连金属在单位区域内必须达到一定的覆盖密度,一般为50%~80%。如达不到,可采用两种办法改变密度: (1)在空白区域填充金属,以增加密度;(2)将较宽的导线(如电源线和地线)切割分布,以减少密度。有挖空(slotting)或分割(splitting)两种方法,后者的电流分布均匀性更好,两种方法还有利于改善导线的散热。

?

?

四、天线比率检查

4.1 起因

????????工艺天线效应(Process Antenna Effect,PAE):集成电路制造采用的等离子刻蚀、溅射或化学机械抛光(CMP)等工艺会在金属互连层中引入并积累静电荷。连接到多晶硅栅的互连线多道金属化工艺中有可能悬空不接地,从而构成天线结构。电荷经此结构传导到MOSFET栅极,会导致栅介质击穿并造成永久性失效。

- 通常用天线比率(antenna ratio)来表征工艺天线效应的强弱,定义为受工艺影响的金属面积与所连接的多晶硅栅面积之比。

- 通常要求天线比率不得大于某值(如100或1000),在LEF文件中规定,作为DRC规则之一。

4.2 计算

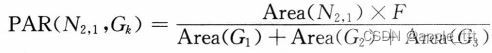

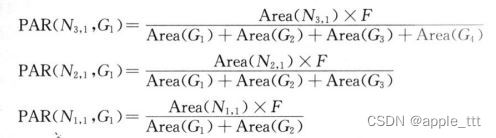

????????部分天线比率(PAR):只考虑一层金属的影响,如图中金属N2,1对栅G1或G2的影响

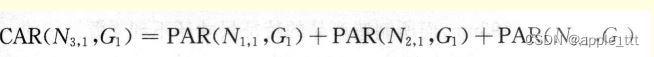

????????积累天线比率(CAR):考虑顶层及以下经过的各层金属的影响,如图中金属N3,1对栅G1的影响

?

?

?

????????F是修正因子,通常接近于1;金属面积Area在小尺寸条件(厚度>>宽度)下多取侧面面积而非底面面积。?

4.3 改进

????????保护二极管法:在天线与地之间加二极管,金属上一旦出现过压就导通,起箝位(限制栅极电压不超过临界值)和泄流(泄放金属上的额外电荷到地)作用,但会引入额外的寄生电容,影响延时。

?

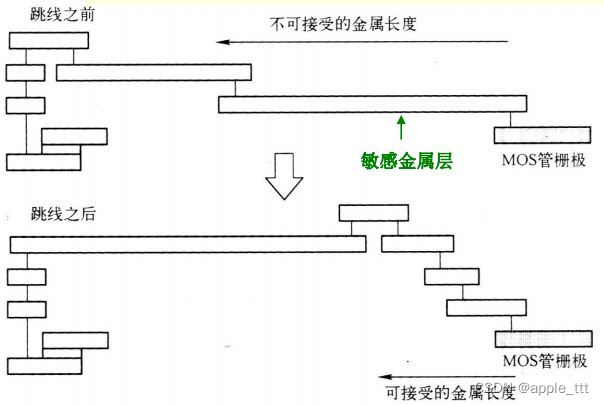

????????跳线法:将最易积累电荷的一层上的长金属线通过过孔分散到其他非敏感的互连层上,从而减少敏感层的天线比率

?

五、LVS检查

????????基本步骤 1. 版图(GDSII格式)→管级网表(SPICE格式)2. 门级网表(Verilog 格式)→管级网表(SPICE格式)3. 将两个网表进行比较,看是否有不一致的地方。

?

六、物理验证常用的EDA工具

- Cadence:Assura、 Diva、Dracula

- Mentor:Calibre

- Synopsys:Hercules

? ? ? ? 以其中的Dracula为例,它的主要功能:版图绘制与编辑、寄生参数提取(LPE)、物理验证(DRC、ERC、LVS)。

?

七、总结

? ? ? ? 对于数字IC验证这个部分,物理验证这篇文章是这个系列的最后一篇,本文介绍了物理验证的分类,并对其内容进行了简单展开。

?

文章来源:https://blog.csdn.net/apple_53311083/article/details/135562584

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- adb工具介绍

- C# Onnx yolov8n forklift detection

- 按照故障码类型分类的API接口

- 防止源代码泄露的10大措施

- json.stringify()详解

- 数据库:基于mysql总结,全部理论集合

- C2855 命令行选项“/Zc:referenceBinding“与预编译头不一致和C2855 命令行选项“/Zc:__cplusplus“与预编译头不一致

- 表的增删改查 进阶(一)

- React导航守卫(V6路由)

- HTML5是什么?与HTML有什么区别?