计算机组成原理 CPU的功能和基本结构和指令执行过程

文章目录

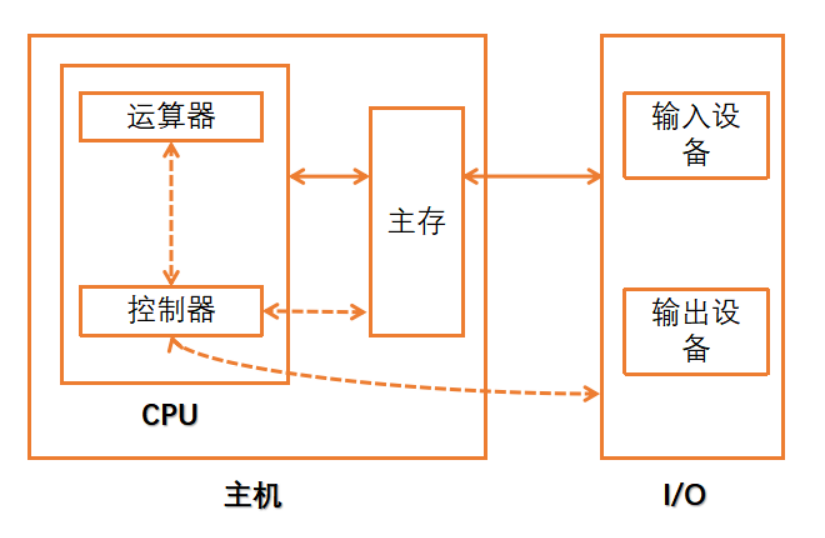

CPU的功能和基本结构

CPU的功能

- 指令控制: 完成取指令、分析指令和执行指令的操作,即程序的顺序控制。

- 操作控制:一条指令的功能往往是由若干操作信号的组合来实现的。CPU管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件,从而控制这些部件按指令的要求进行动作。

- 时间控制: 对各种操作加以时间上的控制。时间控制要为每条指令按时间顺序提供应有的控制信号。

- 数据加工: 对数据进行算术和逻辑运算。

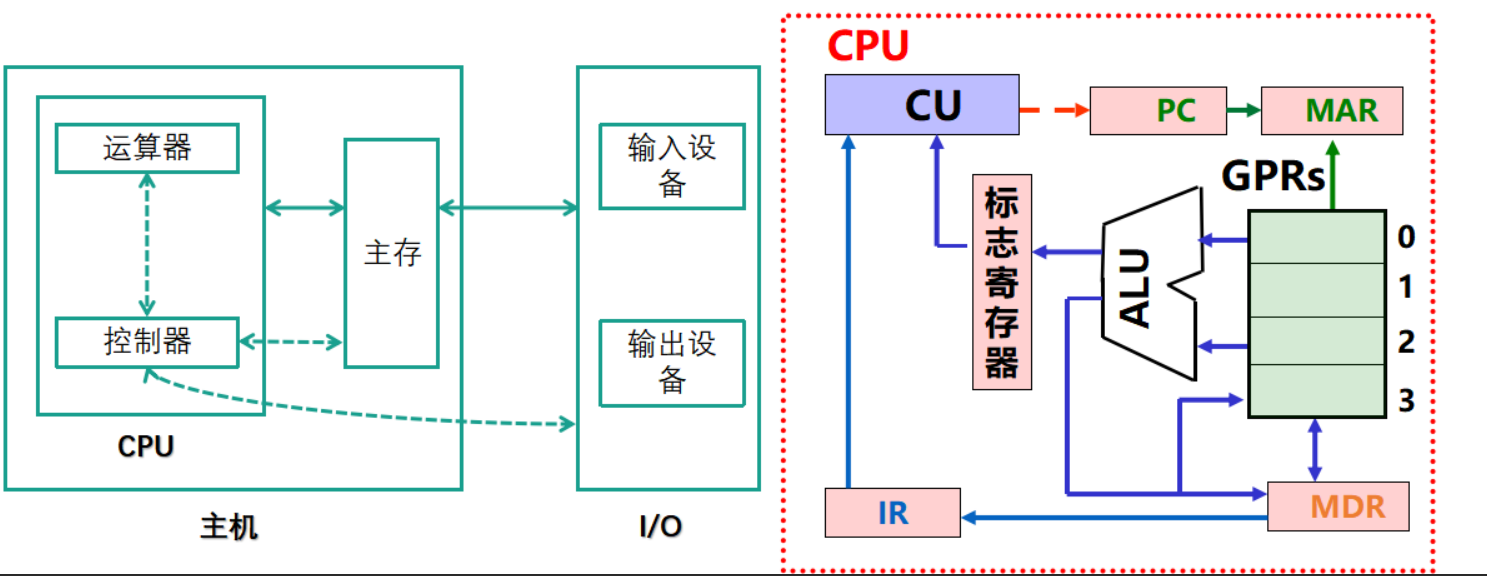

CPU的基本结构

透明性

用户可见的寄存器 (对用户不透明,用户可编程) : PSW.ACC,Ri.PC

用户不可见的寄存器 (对用户透明,用户不可编程) : SR,T,MAR,MDR,IR

控制信号

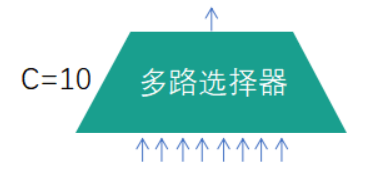

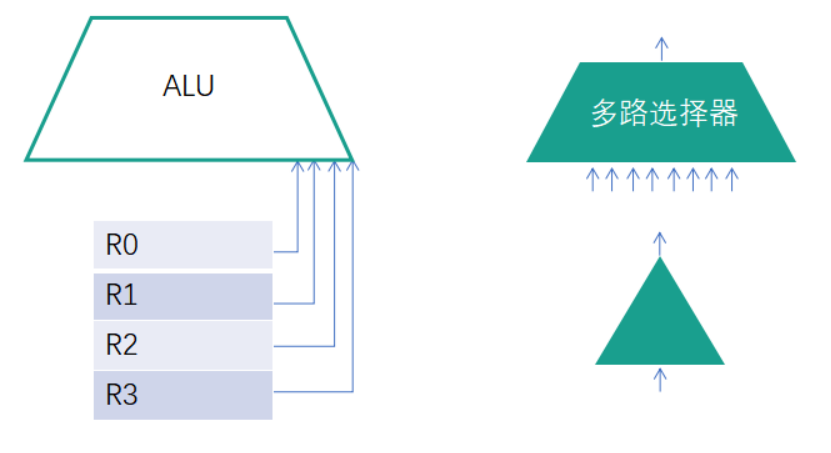

使用多路选择器根据控制信号选择一路输出

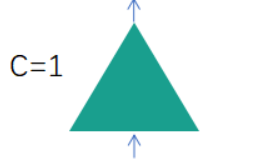

使用三态门可以控制每一路是否输出

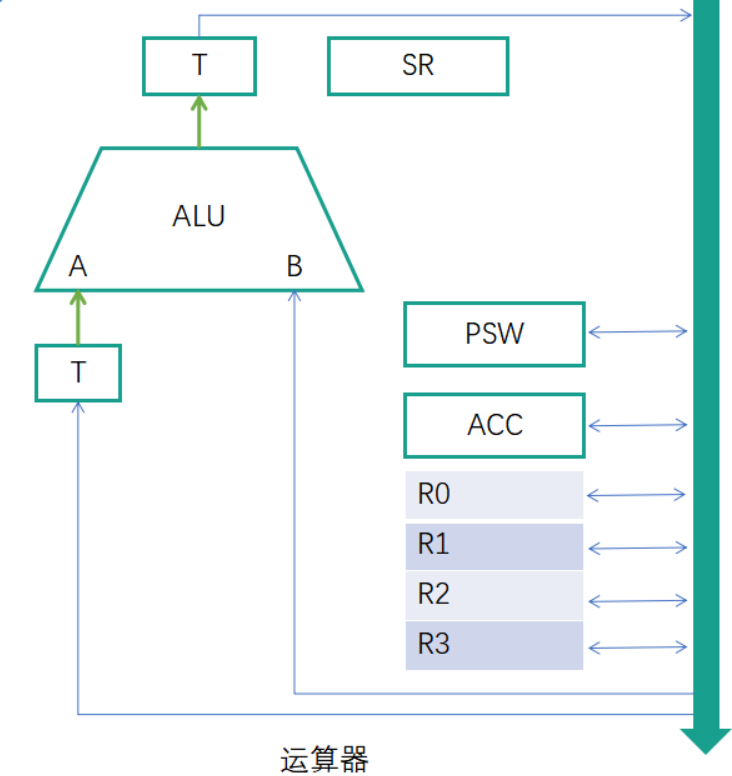

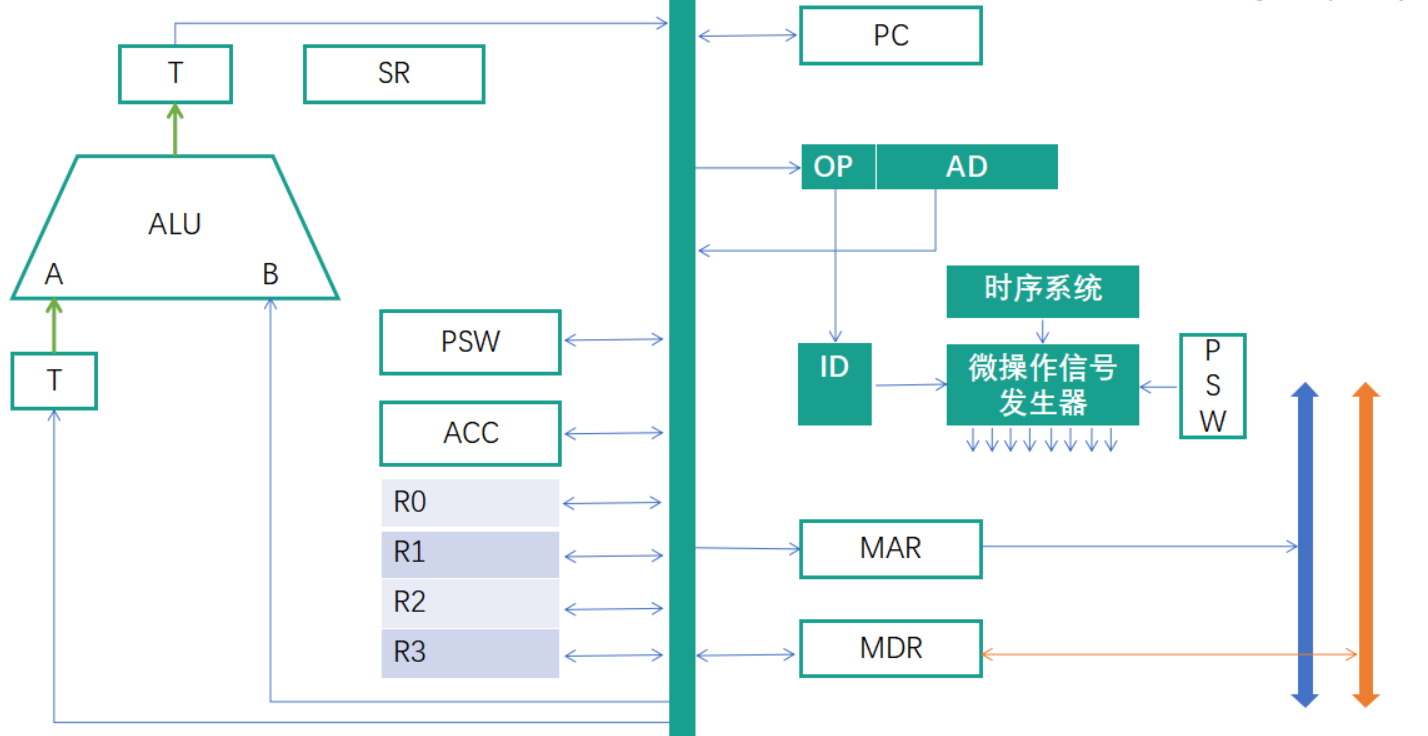

运算器

- 算术逻辑单元ALU: 主要功能是进行算术/逻辑运算。

- 通用寄存器组Ri: 用于存放操作数 (包括源操作数、目的操作数及中间结果) 和各种地址信息等。SP 是堆栈指针,用于指示栈顶的地址。

- 暂存寄存器T。用于暂存从主存读来的数据,该数据不能存放在通用寄存器中,否则会破坏其原有内容。暂存寄存器对应用程序员是透明的

- 累加寄存器ACC。它是一个通用寄存器,用于暂时存放 ALU运算的结果信息,可以作为加法运算的一个输入端

- 程序状态字寄存器PSW。保留由算术逻辑运算指令或测试指令的结果而建立的各种状态信息,如溢出标志 (OF) 、符号标志 (SF) 、零标志 (ZF) 、进位标志 (CF) 等。PSW中的这些位参与并决定微操作的形成。

- 移位器SR。对操作数或运算结果进行移位运算。

- 计数器。控制乘除运算的操作步数

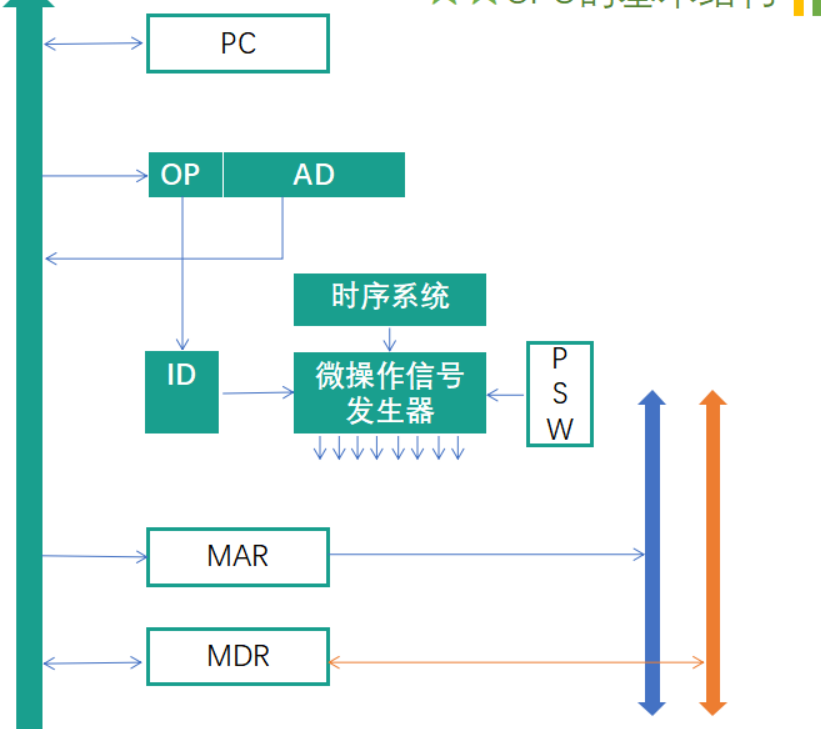

- 程序计数器: 用于指出下一条指令在主存中的存放地址。CPU 根据 PC 的内容去主存中取指令。因程序中指令(通常)是顺序执行的,所以PC 有自增功能

- 指令寄存器: 用于保存当前正在执行的那条指令

- 程序计数器: 用于指出下一条指令在主存中的存放地址。CPU 根据 PC 的内容去主存中取指令。因程序中指令(通常)是顺序执行的,所以PC 有自增功能。

- 指令寄存器: 用于保存当前正在执行的那条指令

- 指令译码器:仅对操作码字段进行译码,向控制器提供特定的操作信号

- 时序系统: 用于产生各种时序信号,它们都由统一时钟(CLOCK) 分频得到

- 微操作信号发生器: 根据IR的内容 (指令) 、PSW的内容 (状态信息) 及时序信号,产生控制整个计算机系统所需的各种控制信号,其结构有组合逻辑型和存储逻辑型两种,

- 存储器地址寄存器: 用于存放要访问的主存单元的地址

- 存储器数据寄存器:用于存放向主存写入的信息或从主存读出的信息。

指令执行过程

指令周期概念

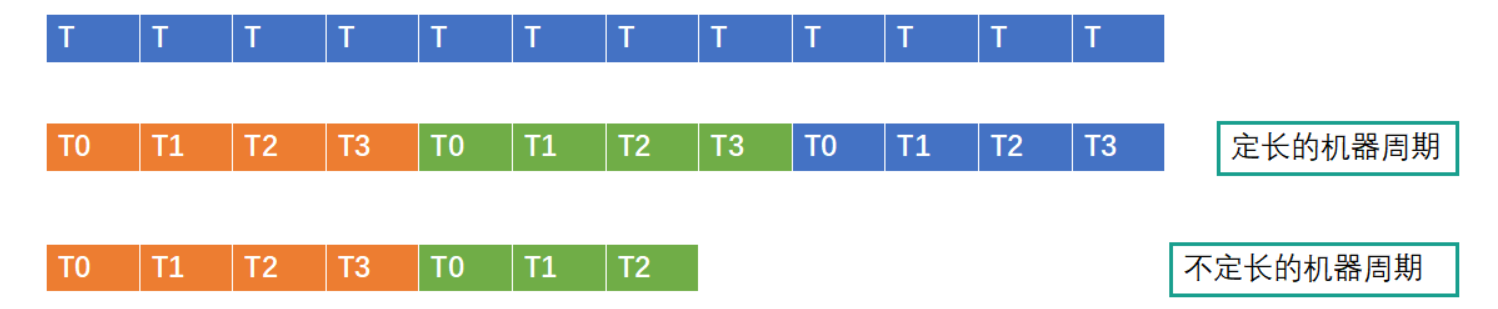

关于周期

时钟周期: (节拍,T周期,CPU时钟周期)

机器周期:(CPU周期)

指令周期: CPU 从主存中取出并执行一条指令的时间称为指令周期,不同指令的指令周期可能不同

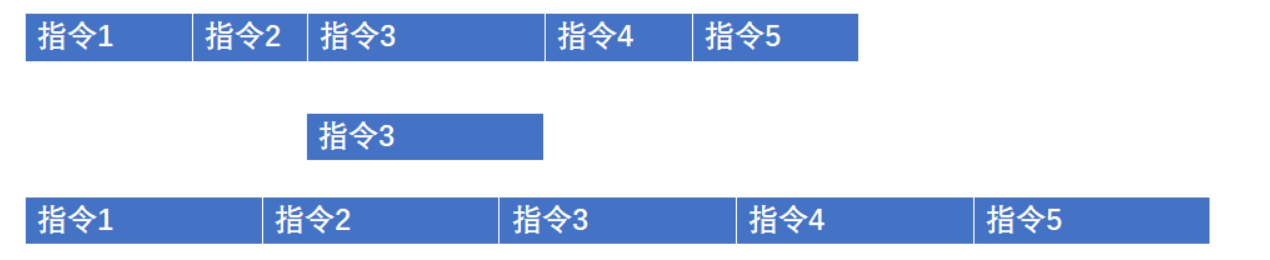

指令的不确定性

时钟周期数不同,每个机器周期内的节拍数也可能不同

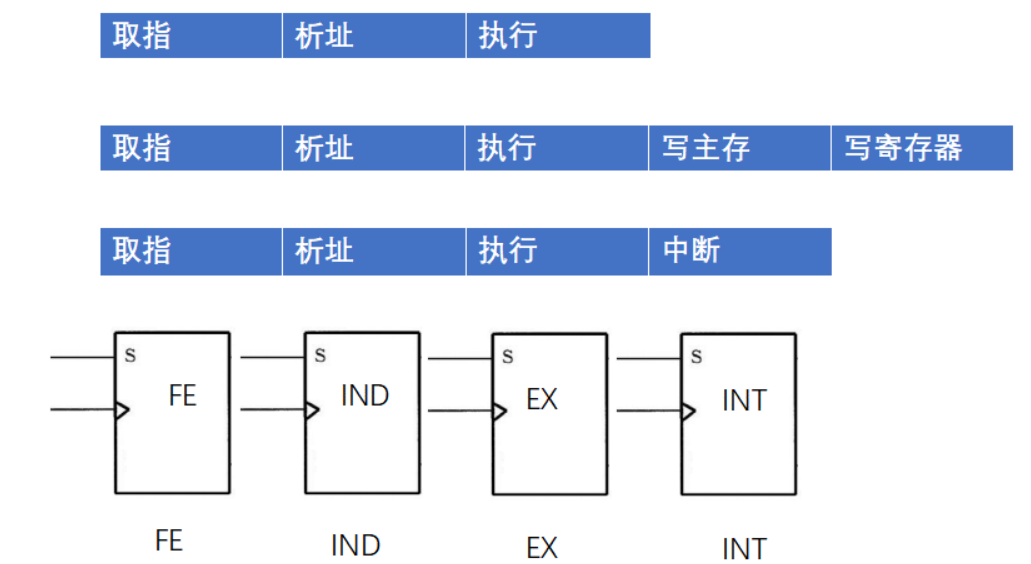

常见类型的指令

指令执行方案

单指令周期

每个指令时间可能不同,但是在单指令周期下,所有指令选用相同的执行时间,指令间串行

优点: 结构、设计简单

缺点:对于原本很短时间的指令,要在较长的时间来完成,显然会降低整个系统的运行速度

多指令周期

不同类型指令选用不同的执行步骤,指令间串行

优点: 不再要求所有的指令占用相同的执行时间

缺点: 执行指令的设计更加复杂

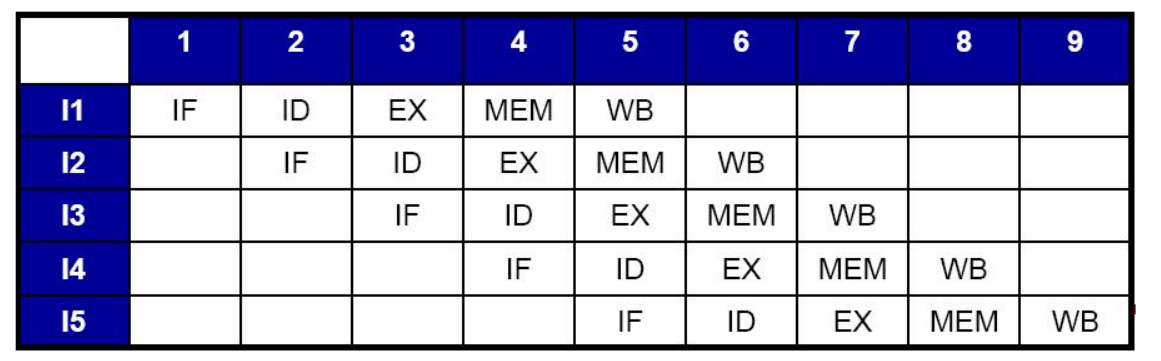

流水线方案

隔一段时间启动一条指令,多条指令位于不同阶段,同时运行

优点: 不再要求所有的指令占用相同的执行时间

缺点: 执行指令的设计更加复杂

指令数据流

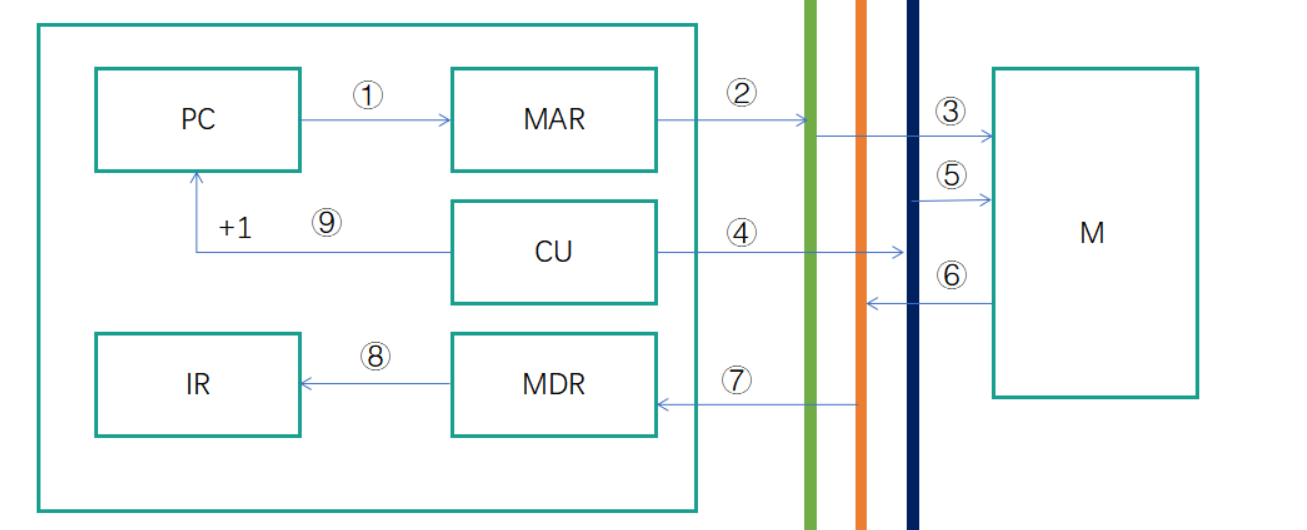

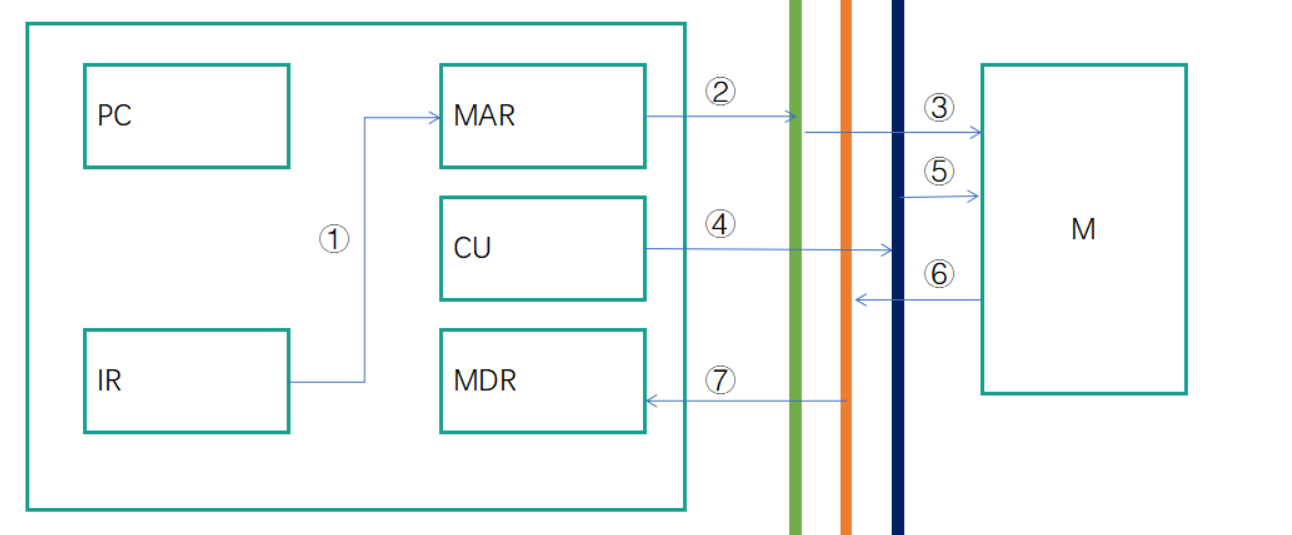

取周期数据流

- PC 1 MAR 2 地址总线3主存

- CU发出控制信号 4 控制总线 5 主存

- 主存 6 固数据总线 7 MDR 8 IR (存放指令)

- CU 发出读命令 9 PC 内容加1。

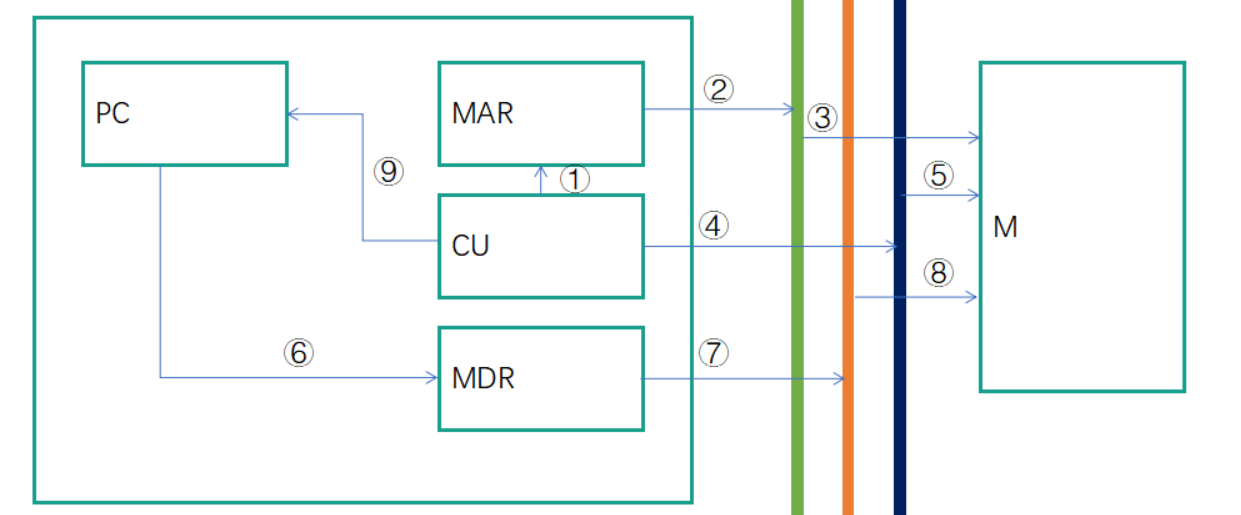

析指周期数据流

- Ad(IR)(或MDR) 1 MAR 2 地址总线 3 主存

- CU 发出读命令 4 控制总线 5 主存

- 主存 6 数据总线 7 MDR (存放有效地址)其中,Ad(IR)表示取出IR中存放的指令字的地址字段

执行周期数据流

各条指令的执行周期不同

中断周期数据流

- CU控制将 SP减 1 ,SPDMAR 2 地址总线 3 主存

- CU发出写命令 4 控制总线 5 主存

- PC 6 MDR 7 数据总线 8 主存 (程序断点存入主存)

- CU (中断服务程序的入口地址) 9 PC

数据通路的功能和基本结构

数据通路的功能

数据通路

数据在功能部件之间传送的路径称为数据通路

路径上的部件称为数据通路部件,如 ALU、通用寄存器、状态寄存器、异常和中断处理逻辑等

数据通路中专门进行数据运算的部件称为执行部件或功能部件。

数据通路功能

数据通路的功能是实现CPU内部的运算器与寄存器及寄存器之间的数据交换。

数据通路的结构

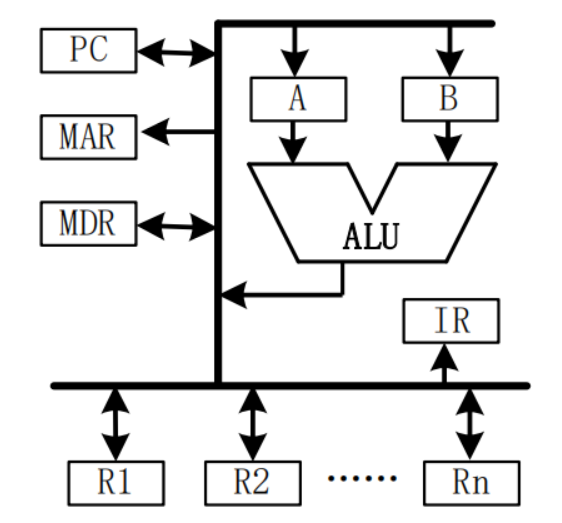

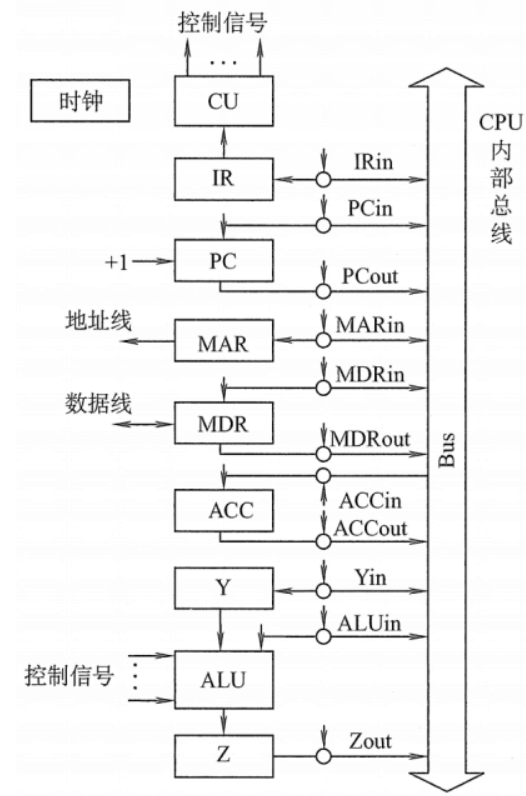

单总线

CPU内部单总线方式

将所有寄存器的输入端和输出端都连接到一条公共通路上,这种结构比较简单,但数据传输存在较多的冲突现象性能较低。连接各部件的总线只有一条时,称为单总线结构:CPU中有两条或更多的总线时,构成双总线结构或多总线结构

专用数据通路方式

根据指令执行过程中的数据和地址的流动方向安排连接线路,避免使用共享的总线,性能较高,但硬件量大。

内部总线

同一部件,如 CPU 内部连接各寄存器及运算部件之间的总线

系统总线

系统总线是指同一台计算机系统的各部件,如CPU、内存、通道和各类 /O接口间互相连接的总线

外部总线

外部总线是指各台计算机之间相互通信的总线

寄存器之间的数据传送

把PC 内容送至 MAR,实现传送操作的流程及控制信号为

(PC)->Bus ? PCout 有效,PC 内容送总线

Bus->MAR ? MARin 看效,总线内容送 MAR

主存与 CPU 之间的数据传送

CPU从主存读取指令为例说明数据在数据通路中的传送过程

(PC)->Bus->MAR ? PCout 和 MARin 有效,现行指令地址->MAR

1->R ? CU发读命令

MEM(MAR)->MDR ?

(MDR)->Bus->IR ? MDRout 和 IRin有效,现行指令->IR

执行算术运算和逻辑运算

Ad(IR)->Bus->MAR ? MDRout 和 MARin 有效

1->R ? CU 发读命令

MEM(MAR)->数据线->MDR ? 操作数从存储器->数据线->MDR

MDR->Bus->Y ? MDRout 和 Yin 有效,操作数->Y

(ACC)+(Y)->Z ? ACCout和ALUin有效,CU发出加命令结果->Z

Z->ACC ? Zout和ACCin有效,结果ACC

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- UDP特性之组播(多播)

- Linux-ionde(软硬件链接)剖析

- Supershell反溯源配置

- SQL Server的聚合函数、SQL Server的联合查询、SQL Server的左连接右连接内连接

- mac上cmake编译的库A,给其他库B使用报错ld64.lld: error

- 学习响应式编程中遇到的奇奇怪怪的问题

- 【开源】基于JAVA+Vue+SpringBoot的考研专业课程管理系统

- css3新增功能有哪些

- 智能论文降重 快码论文

- 越南访问国内服务器速度慢,云桥通SD-WAN企业组网解决加速问题