《EDA技术实用教程(第六版(黄继业, 潘松))》学习笔记——第三章

发布时间:2024年01月17日

《EDA技术实用教程(第六版)》学习笔记——第三章

第三章目录

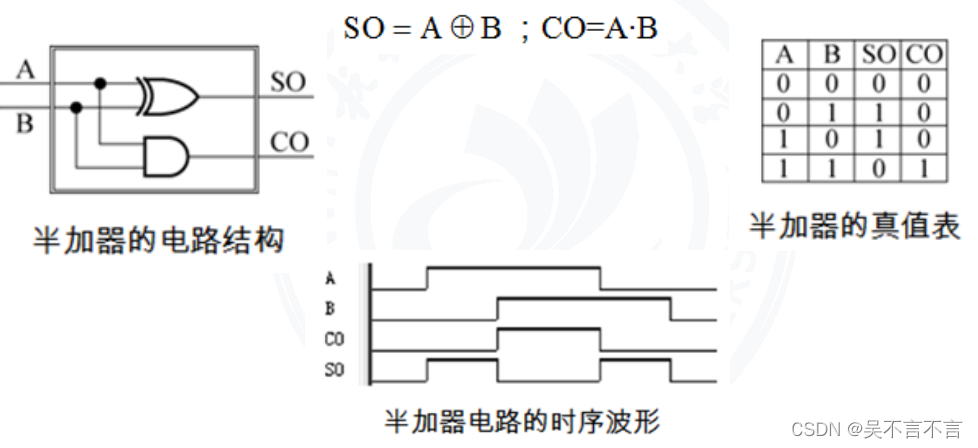

1、半加器的Verilog的描述

- 半加器的逻辑表述、半加器的电路结构、真值表、时序波形:

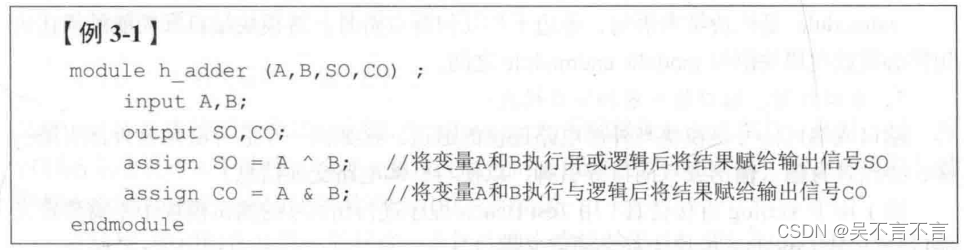

- 半加器的Verilog描述:

- h_adder是模块名,是设计者为其设计的模块所取的名字。

- h_adder旁的括号及其内容称为“端口表”,括号中的内容就是此模块的所有端口信号名。

- assign引导的赋值负责描述模块内部的逻辑功能和电路结构。

- assign引导的赋值语句属于并行赋值语句,无论有多少行语句,都是同时执行的,与语句的前后次序无关。

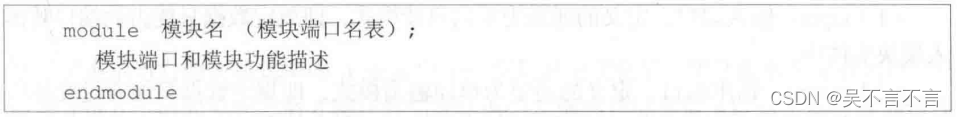

1、1模块语句及其表达方式

- 任一可综合的最基本的模块都必须以关键词module开头。

- 模块名最好根据相应电路的功能来确定。如4位二进制计数器用counter4b。

- 模块端口列表中须列出此模块的所有输入、输出或双向端口名,端口名间用逗号分开,括号外加 分号。

- endmodule是模块结束语句关键词,旁边不加任何标点符号。对模块端口及其功能的描述语句都

必须放在模块语句module_endmodule之间。

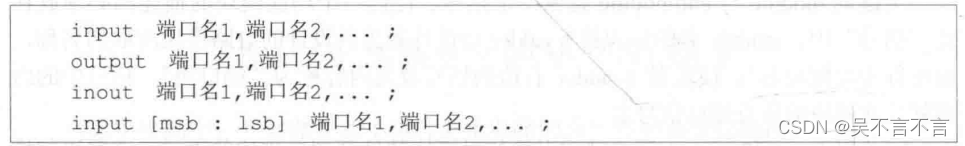

1、2端口语句、端口信号名和端口模式

- 输入端口:input

- 输出端口:output

- 双向端口:inout 使用比较复杂,后续有专门章节讲述,在未理解前,不要轻易使用

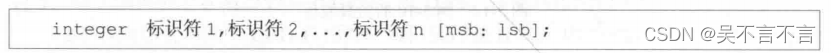

- 最后一种端口描述方法是端口信号的逻辑矢量位表达方式,其中的msb和lsb分别是信号量的最高和最低位数。output [3:0] C,D; // C、D均为4位输出端口。

1、3逻辑操作符

Verilog的逻辑操作符大部分与C语言一致,比如:

- 逻辑按位与: &

- 逻辑按位或: |

- 逻辑按位异或:^

- 逻辑按位取非:~

但Verilog也有自己的扩展,比如

- 逻辑按位 与非 ~&

- 逻辑按位 或非 ~|

- 逻辑按位 同或 ~^

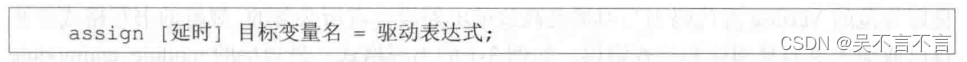

1、4连续赋值语句

- 当等式右端的驱动表达式(赋值源)中任一信号发生变化时,此表达式即被重新计算一遍。

- assign语句是Verilog的并行语句,模块中所有的assign语句同时执行,语句的前后顺序无关;

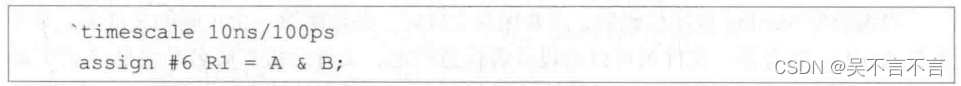

- -加入[延时],表示经过指定延时后再赋值,

- 但这个延时值在综合器中是被忽略的,不参与综合。

- 只对仿真器有效

- 此句表示,仿真的基本时间单元是 10ns,仿真时间的精度是 100ps。在这个时间划分单元下,语句assign #6 R1=A&B”在执行后,一旦计算出A&B的值还要再等待6个时间单元也就是60ns后才将此值赋给 R1。

1、5关键字

- 指verilog语言中预定义的有特殊含义的英文词语。input、output、module、assign、endmodule

关键词必须小写。

1、6标识符

- 设计者在verilog程序中自定义的,用于标识不同名称的词语。例如模块名、信号名、端口名等。Verilog中标识符区分大小写。

1、7书写规范

- Verilog标识符,以英文字符(大小写均可)、数字、下划线“_”组合而成但只能用英文字符或者下划线开头(下划线开头需要慎用,一般为软件自带库来使用),标识符用数字开头是不允许的。

- 最顶层的module_endmodule模块描述语句放在最左侧,比它低一层次的描述语句则向右靠一个Tab键距离。同一语句的关键词要对齐。

1、8Verilog模块文件取名和存盘

- 文件后缀名必须是“.v”。

- 文件取名的大小写也是敏感的。文件名与存储路径不能带有中文字符。

- 对于Quartus,程序名必须和该程序的模块名一致。

1、9注释符号

- //后的注释文字只能放在同一行

- /…/ 可以换行文件取名的大小写也是敏感的。文件名与存储路径不能带有中文字符。

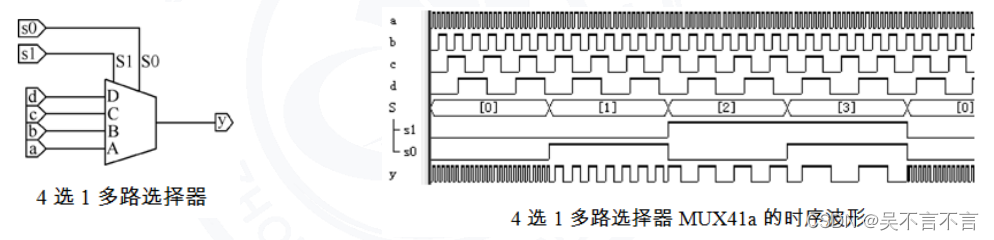

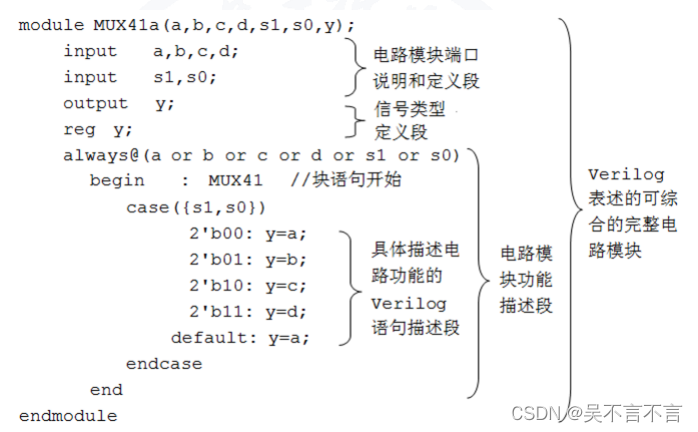

2、4选1多路选择器及其case语句表述方式

- 4选1多路选择器的电路结构、时序波形:

- 4选1多路选择器的Verilog描述:

本例还包含以下五方面新的语句结构和表述方式: - 以reg关键词定义的模块内相关信号的特性和数据类型。

- 以always关键词引导的对模块逻辑功能描述的顺序语句。

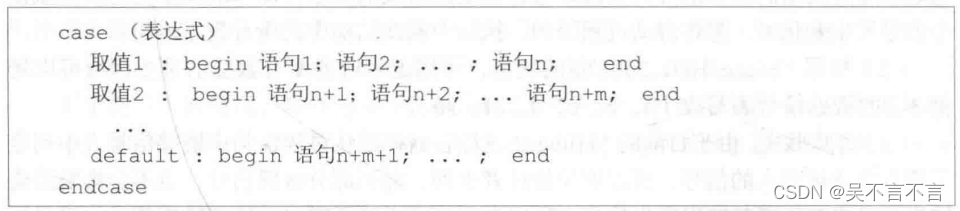

- 以case_endcase引导的多条件分支赋值语句。

- 以begin_end引导的顺序块语句。

- Verilog数据并位及数据表达方式。

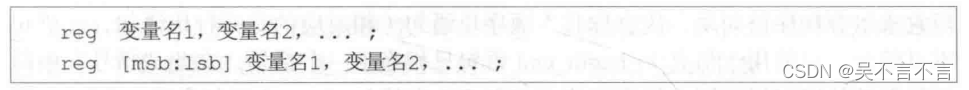

2、1reg型变量定义

- reg: 寄存器型变量;

- 在过程语句always@引导的顺序语句中, 被赋值信号规定必须是reg型变量;

- 输入或双向口信号不能定义为reg型。

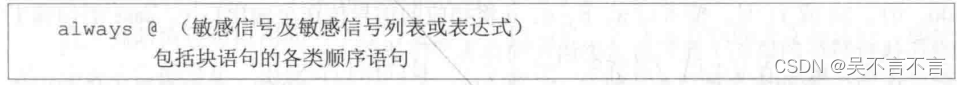

2、2过程语句

- Verilog中有两类能引导顺序语句的过程语句,always在可综合语句

中最为常用,另一类过程语句是initial语句。

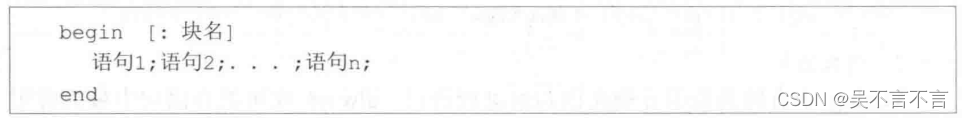

2、3块语句begin _end

- 块语句begin end仅限于在always引导的过程语句结构中使用,只相当于一个括号。

- 以上方括号中的“:块名”可以省略。

2、4case条件语句

2、5Verilog的四种逻辑状态

Verilog有四种基本数值:

- 0:含义有四个,即二进制数0、低电平、逻辑0,事件为伪的判断结果。

- 1:含义也有四个,即二进制数1、高电平、逻辑1、事件为真的判断结果。

- z或Z。高阻态,或高阻值。

- x或X。不确定,或未知的逻辑状态。x与z大小写都不分。

2、6并位操作运算符

2、7Verilog的数字表达形式

- (1)B:二进制, O:八进制,H:十六进制,D:十进制

- (2)不分大小写,如:2’b10, 4’hA等

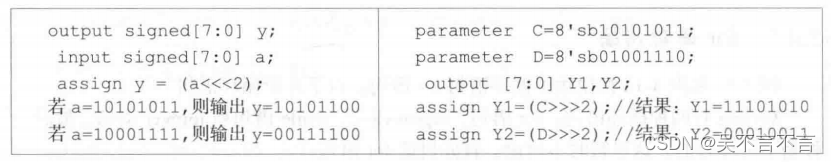

- (3)sb定义有符号二进制数:8’sb10111011,最高位1是符号。

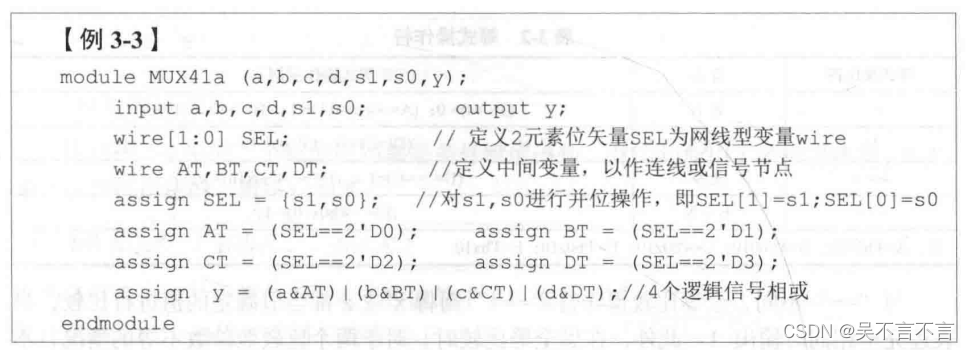

3、4选1多路选择器及其case语句表述方式

- 4选1多路选择器的Verilog描述:

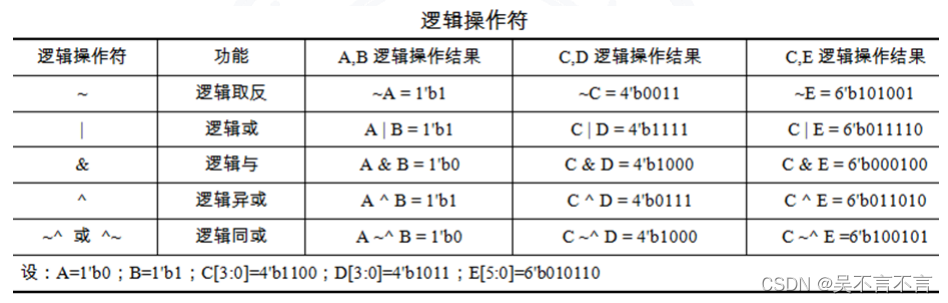

3、1按位逻辑操作符

- 如果两个操作数位矢具有不同长度,综合器将自动根据最长位的操作数的位数,把较短的数据按左端补0对齐的规则进行运算操作。

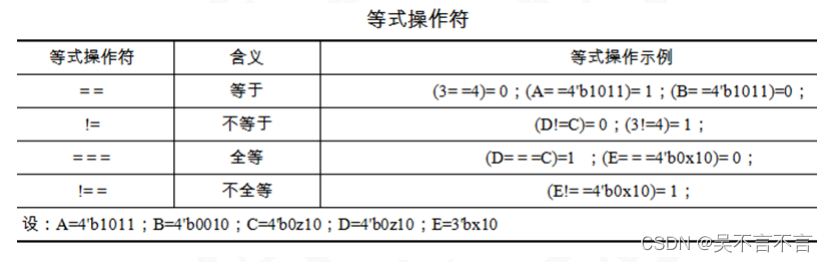

3、2等式操作符

- Verilog中任何变量有4个状态:0;1;z (高阻态);x (不确定或未知状态)

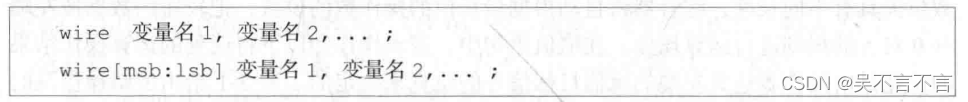

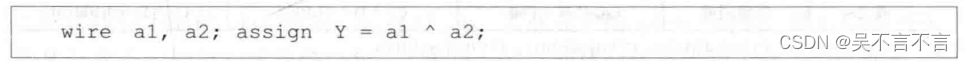

3、3wire定义网线型变量

- 如果assign语句中需要有端口以外的信号或连接线性质的变量(由于端口都已默认为网线型变量),则必须用网线型变量定义语句事先给出显式定义。

- 用wire定义的网线型变量可在任何类型的表达式或赋值语句(包括连续赋值和过程赋值语句)中用作输入信号,也可以在连续赋值语句或实体元件例化中用作输出信号。

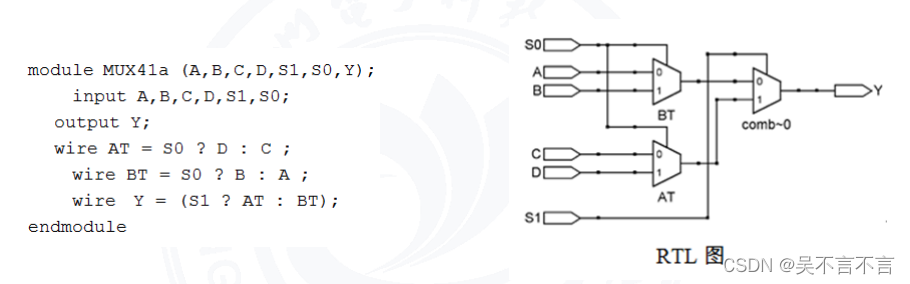

4、4选1多路选择器及其case语句表述方式

- 4选1多路选择器的Verilog描述和RTL:

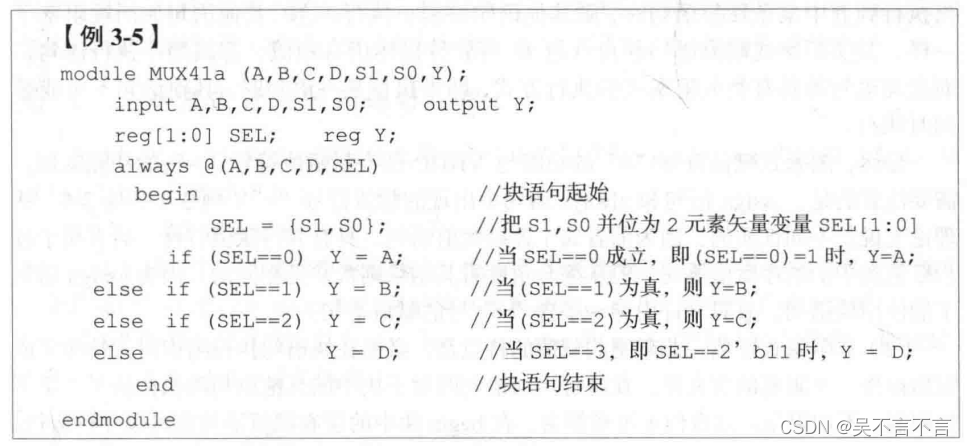

5、4选1多路选择器及其条件语句表述方式

- 4选1多路选择器的Verilog描述和RTL:

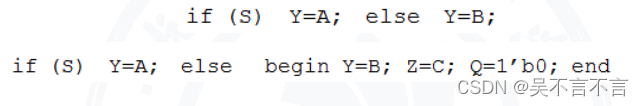

5、1if条件语句

5、2过程赋值语句

- 阻塞式赋值:如y=b; 一旦执行完当前的赋值语句,赋值目标变量y即刻获得来自等号右侧表达式的计算值。如果在一个块语句中含有多条阻塞赋值语句,**而当执行到其中某条赋值语句时,其他语句被禁止执行,**这时其他语句如同被阻塞了一样。

- 非阻塞式赋值:如y<=b;在执行当前语句时,对于块中的其他语句的执行情况一律不加限制。

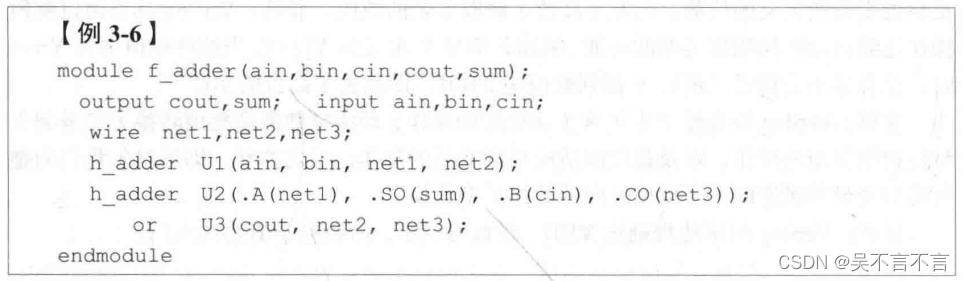

6、全加器设计及例化语句应用

6、1全加器原理图结构

- Sum=第一个半加器的和,加上Cin (即两个半加器的级联,最终的和输出)。

- Cout=第一个半加器的进位,“或”第二个半加器的进位。

6、2顶层设计文件

元件例化:

- 引入一种连接关系,将预先设计好的设计模块定义为一个元件,

- 然后利用特定的语句将此元件与当前的设计实体中指定端口相连接,

- 从而为当前设计实体引进一个新的、低一级的设计层次。

6、3Verilog例化语句及其用法

- <模块元件名>,它具有唯一性。如果是用Verilog描述的模块,则是模块名,也即元件名;

- <例化元件名>:在具体电路上模块被调用后放在不同的位置或担任不同的任务又必须有对应 的名称。

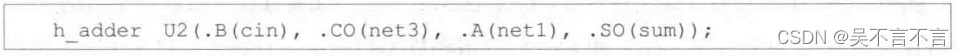

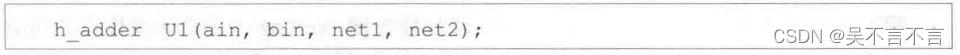

- 端口名关联法:括号中的信号名是外部端口名,括号外带点的信号名是待连接的元件自己的端口名。

- 位置关联法,关联表述的信号位置十分重要,注意端口顺序,不能放错。

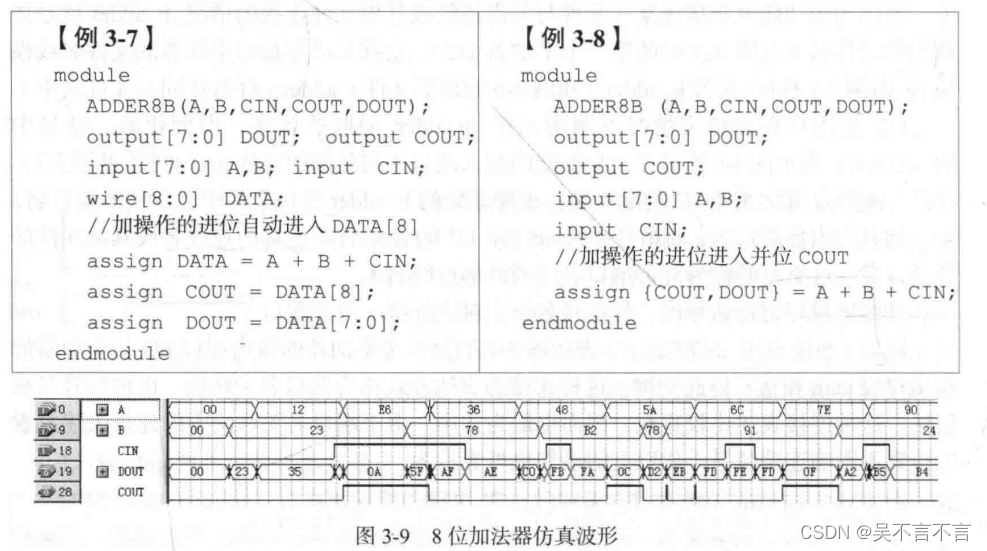

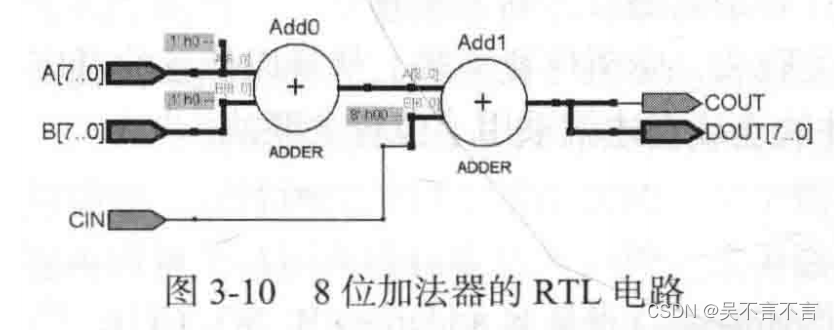

7、8位加法器设计及算术操作符应用

- 8位加法器Verilog描述和仿真波形:

- 8位加法器RTL图:

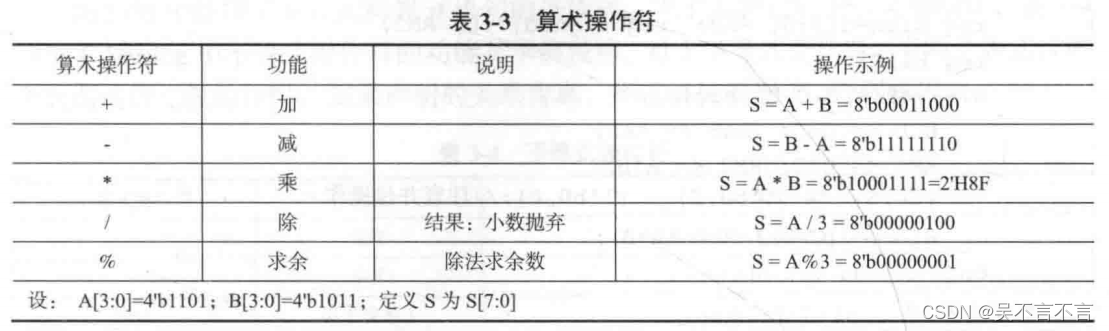

7、1算术运算操作符

- 所有算数运算都是按无符号操作数进行的,如果是减法运算,输出的结果是补码。对于乘法,若为无符号数,可直接用乘法算符(*);若为有符号数乘,则需将操作数和输出结果用signed定义为有符号数,乘法结果为补码。

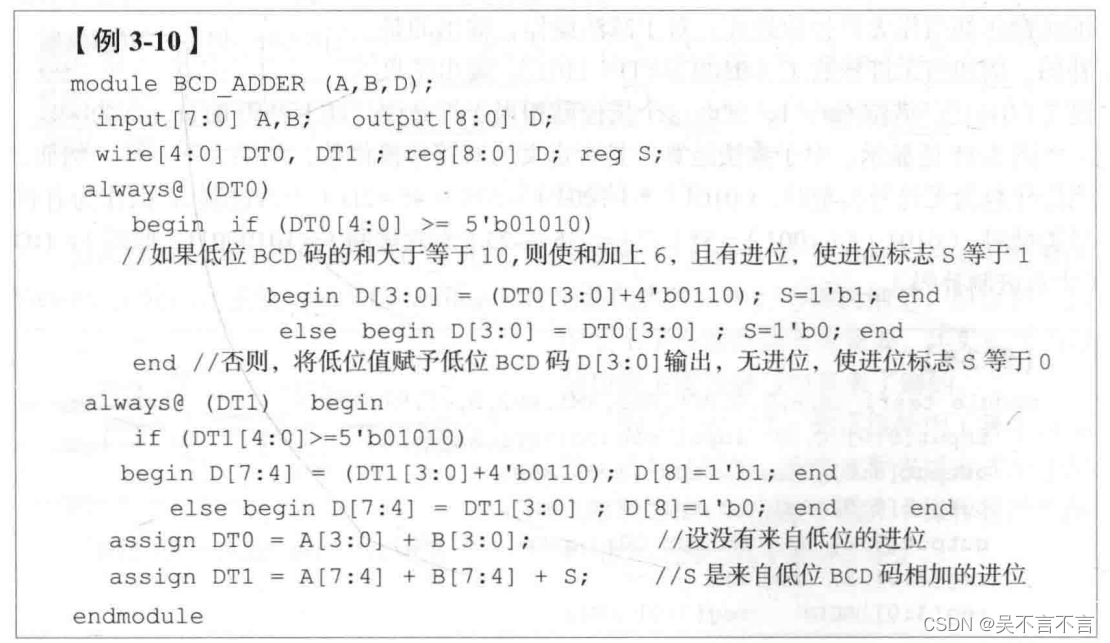

8、BCD码加法器设计

8421BCD码相加的编程应该考虑以下两个问题:

- (1)由于用4位二进制数表示的BCD码的表示范围是0~9,其余的6个数,10(4b1010)15(4b1111)都属于无效BCD码,因此如果当两个BCD码相加后的值超过9,则必须再加上6来得到一个有效的BCD码,且向高位进位1。

- (2)有时尽管当两个BCD码相加后的值仍旧是有效的BCD码,但如果相加后向高位有进位,仍然认为其和大于等于10,故仍需要将相加的结果再加上6。

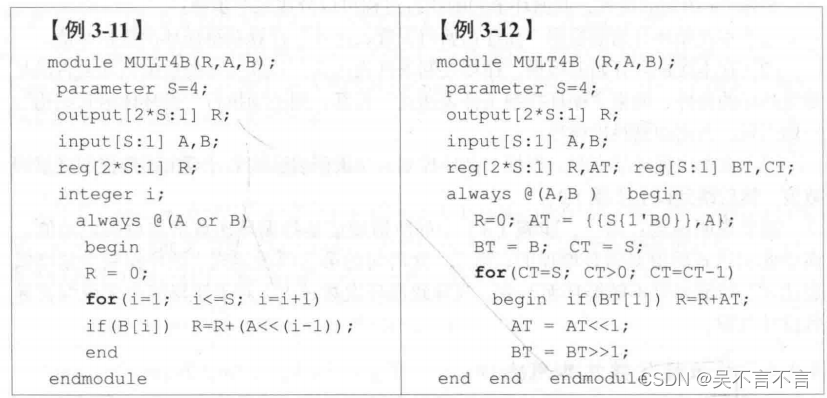

9、组合逻辑乘法器设计

9、1参数定义关键词parameter和localparam

- localparam的功能和用法与parameter类似,它是一个局部参数定义关键词,但无法通过外部程序的数据传递来改变localparam定义的常量。

9、2整数型寄存器类型定义

- reg类型必须明确定义其位数。但integer类型的定义不必特指位数,因为它们都默认为32位宽的二进制寄存器类型。

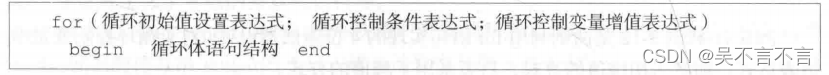

9、3for语句用法

- (1)本次循环开始前根据“循环初始值设置表达式”计算获得循环次数初始值。

- (2)在本次循环开始前根据“循环控制条件表达式”计算所得的数据判断是否满足继续循环的条件,如果“循环控制条件表达式”为真,则继续执行“循环体语句结构”中的语句,否则即刻跳出循环。

- (3)在本次循环结束时,根据“循环控制变量增值表达式”计算出循环控制变量的数值,然后跳到以上步骤(2)。

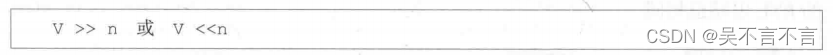

9、4移位操作符及其用法

- 右移或左移,移出腾空的位用0填补:

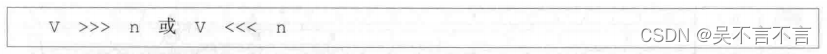

- 有符号数左右移,右移一律将符号位,即最高位填补移出的位。左移操作同普通左移<<。

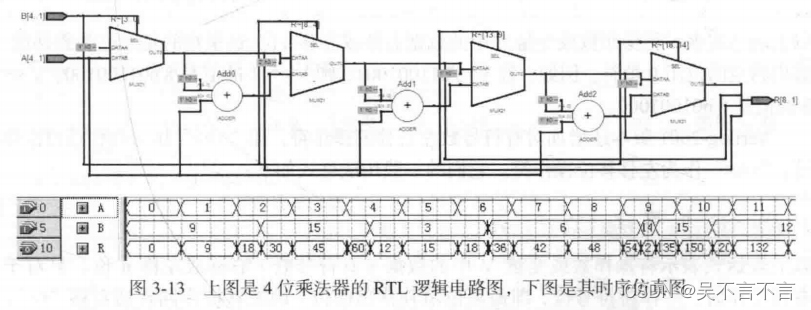

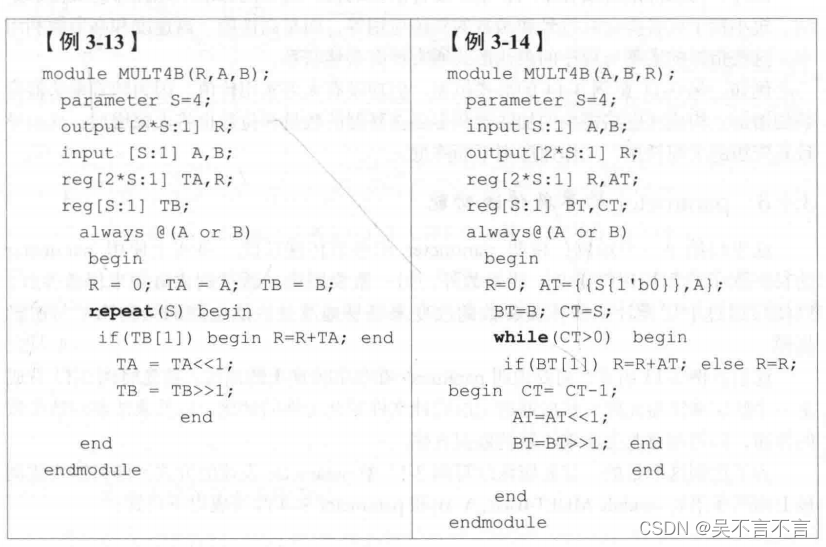

9、5两则乘法器设计示例

- 乘法器Verilog描述:

- 乘法器电路图和时序仿真图:

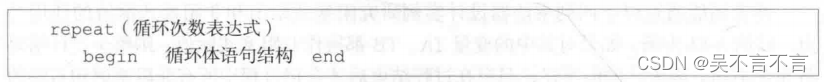

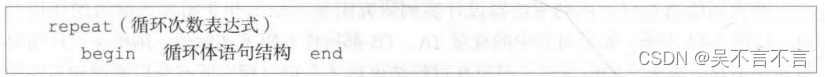

9、6repeat语句用法

- “循环次数表达式”可以是数值确定的整数、变量或定义了常数的参数标识符等。

- repeat语句的循环次数是在进入此语句执行以前就已决定的,无需循环次数控制增量表达式及其计算。

9、7repeat语句用法

- 首先根据“循环控制条件表达式”的计算所得判断是否满足继续循环的条件,如果为真,执行一遍“循环体语句结构”中的所有语句;若为伪,即不满足循环表达式的条件,结束循环。

- 对于此种循环语句,必须在“循环体语句结构”中包含类似for语句的“循环控制变量增值表达式”。

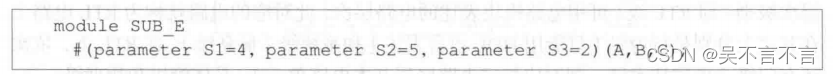

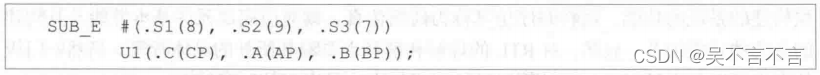

9、8parameter参数传递功能

- 例如若底层文件的模块语句和参数表述是

- 则在例化语句中应作如下类似表述:

- SUB_E是模块元件名,即底层模块名;诸如参数定义parameter S2=5可省略为parameter

S2。这是因为当一层模块被调用后,其内部原来被parameter定义的参数5已经失效,而对应的参数将来自上层例化语句给定的9。

10、RTL

RTL描述

- 把切用可综合的语句表述的,可由综合器生成实际电路的HDL代码形式称为 RTL描述。

RTL级或RTL电路

- 将RTL表述确定为数字系统表述的某一层次级别,即RTL级(可用电路模块表述的电路层次,此对应的电路就称为RTL电路).在其之上分别是行为级(只能用 HDL语言表述)和系统级(最高级);在RTL下,依次还有门级(也称技术级,即对应集成电路底层基本电路单元)、晶体管级和物理级。

- 可以无寄存器

- 状态存储元件+组合逻辑

- 比门级更高一级(更抽象)的逻辑电路描述

- 已经对应硬件电路的结构

- Verilog描述的模块大多在RTL层次

- 用RTL思维方式,理解硬件,然后用Verilog描述出来

如有需要课本PDF与课件可以评论区联系发邮箱。

文章来源:https://blog.csdn.net/QI__HAO/article/details/135625557

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章