数字IC设计——数字电路基本元器件

发布时间:2024年01月03日

现代数字集成电路基本由CMOS晶体管构成,而CMOS门电路由PMOS场效应管和NMOS场效应管以对称互补的形式组成,所谓“互补”,即利用互补型MOSFET,即pMOS和nMOS,二者成对出现构成互补电路。

这种电路具有高的电路可靠性和抗干扰能力,同时可以实现低功耗和高速运算。

注:本文所述元器件均为数字集成电路范畴

组合逻辑电路

传输门

用于放大传输信号

时序逻辑电路

D锁存器

锁存器通常由一个使能信号(Enable)控制,当使能信号有效时,锁存器可以锁住或保持当前的输入状态;当使能信号无效时,锁存器的输出与输入相同。因此,锁存器是电平触发的,属于异步控制。

在锁存状态下,输出与输入信号无关,保持之前的状态。这使得锁存器在某些情况下可以作为一个简单的数据保持器件。

由于其电平触发的特性,锁存器对输入电平敏感,容易受到布线延迟的影响,输出可能会产生毛刺。

D锁存器由3个反相器、2个与非门和2个或非门组成,共需22个管子。在ASIC中使用锁存器的集成度通常比DFF高,因为锁存器消耗的门电路资源较少。在FPGA中,由于标准单元库中没有锁存器,实现锁存器需要更多的逻辑单元(LE)。

锁存器常用于数据有效迟于时钟信号有效的场合,例如在某些运算器电路中作为数据暂存器。

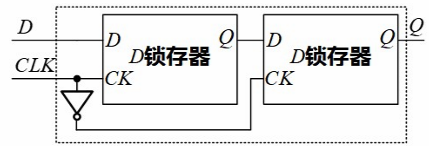

D触发器

两个D锁存器构成一个D触发器,触发器受时钟信号(Clock)控制,只有在时钟信号的边沿(上升沿或下降沿)到来时,触发器才会采样当前的输入并产生输出。因此,触发器是由时钟沿触发的,属于同步控制。

触发器具有两种状态,在保持状态下,输出会保持当前的状态,直到下一个时钟信号到来。由于时钟信号的同步控制,触发器不易受到布线延迟的影响,输出毛刺较少。

D触发器需要2X22+2=46个管子

触发器广泛用于各种时序逻辑电路,如计数器、寄存器等。

RS触发器

相比D触发器,RS触发器是边沿触发的。

参考文献

文章来源:https://blog.csdn.net/qq_39815222/article/details/135279398

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 从零开始搭建ubuntu 16.04 pwndocker环境

- Linux上搭建YApi

- 链表的逆置

- led手电筒照明线性恒流驱动芯片推荐:SM2123EGL双通道可调光

- Java新手必看:final关键字的正确使用技巧,让你避免常见错误!

- ChatGPT在金融财务领域的10种应用方法

- libcurl使用默认编译的winssl进行https的双向认证

- 大家转行软件测试,简历都是咋写的?

- js案例应用

- Google Earth Engine谷歌地球引擎GEE批量下载ImageCollection遥感影像数据合集的方法