【ZYNQ】教你用 Vivado HLS 快速设计一个 IP

发布时间:2023年12月28日

Xilinx 推出的 Vivado HLS 工具可以直接使用 C、C++或 System C 来对 Xilinx 系列的 FPGA 进行编程,从而提高抽象的层级,大大减少了使用传统 RTL 描述进行 FPGA 开发所需的时间。

Vivado HLS 的功能简单地来说就是把 C、C++ 或 SystemC 的设计转换成 RTL 实现,这样就可以在 Xilinx FPGA 或 Zynq 芯片的可编程逻辑中综合并实现,我们仍然是在进行硬件设计,只不过使用的不再是硬件描述语言。

以实现 LED 闪烁为例,通过使用 HLS 生成一个 LED 闪烁 IP,并导入到 Vivado 中验证,学习掌握使用 HLS 快速设计 IP 的方法。

-

开发环境:Windows

-

软件版本:Vivado 2017.4

-

验证平台:黑金 ZYNQ 7035

HLS 设计

- 打开 HLS,点击

Create New Project:

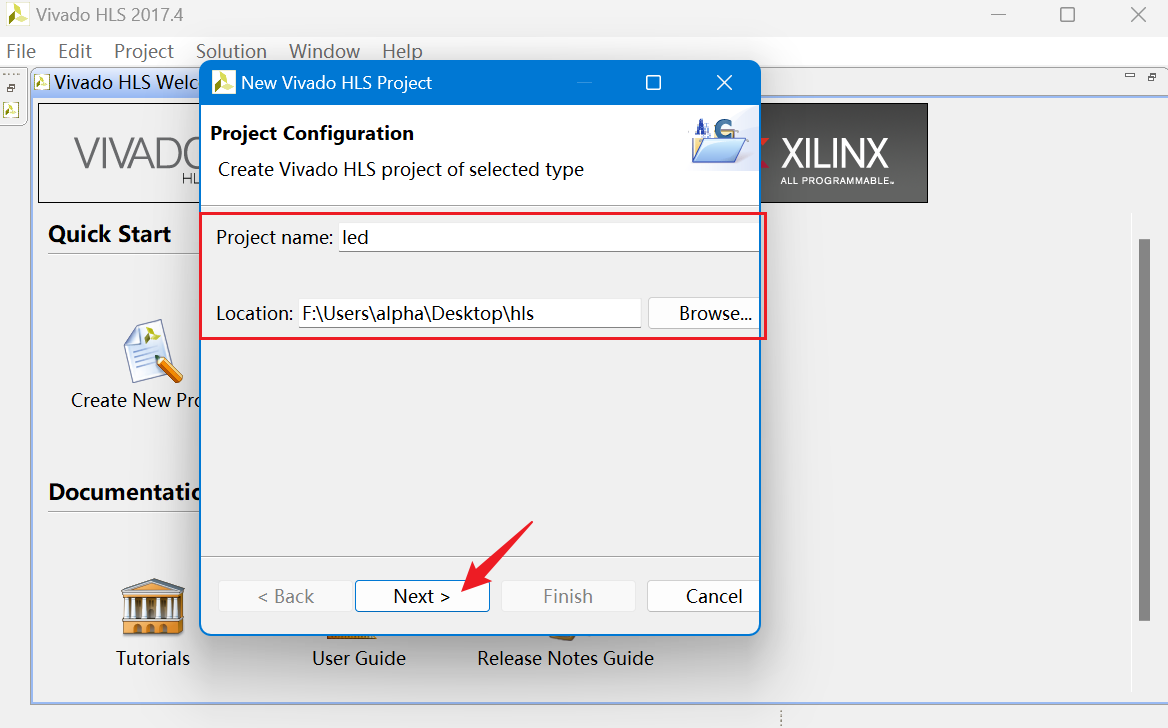

- 填写工程名字,选择工程保存路径,注意不可包含中文,点击

Next:

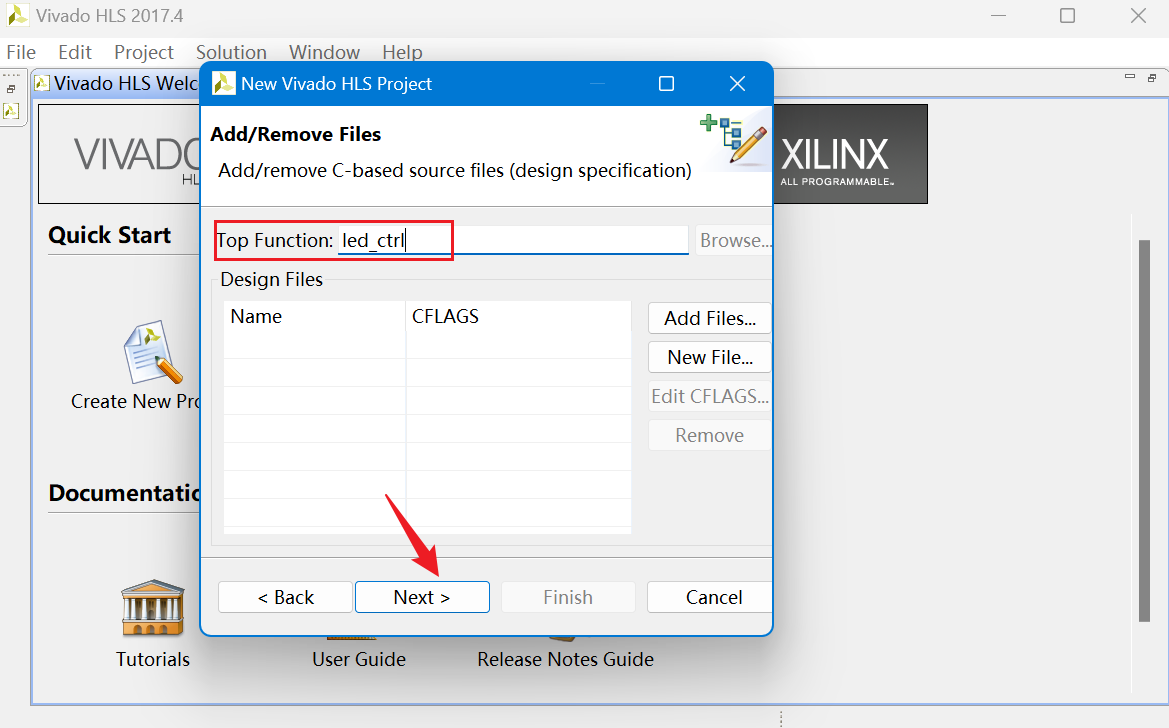

- 填写顶层函数名字,点击

Next:

- 暂时不添加文件,点击

Next:

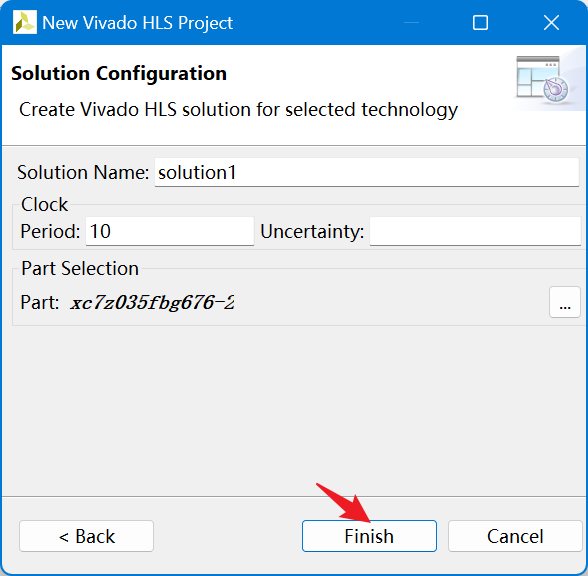

- Clock Period 为运行时钟的周期,默认是 10ns,Clock Uncertainty 默认为时钟周期的 12.5%。点击

...选择芯片类型:

- 我们使用的验证板卡为黑金的 ZYNQ7035 开发板,搜索选中

xc7z035fbg676,点击OK:

- 点击

Finsh,工程配置完成:

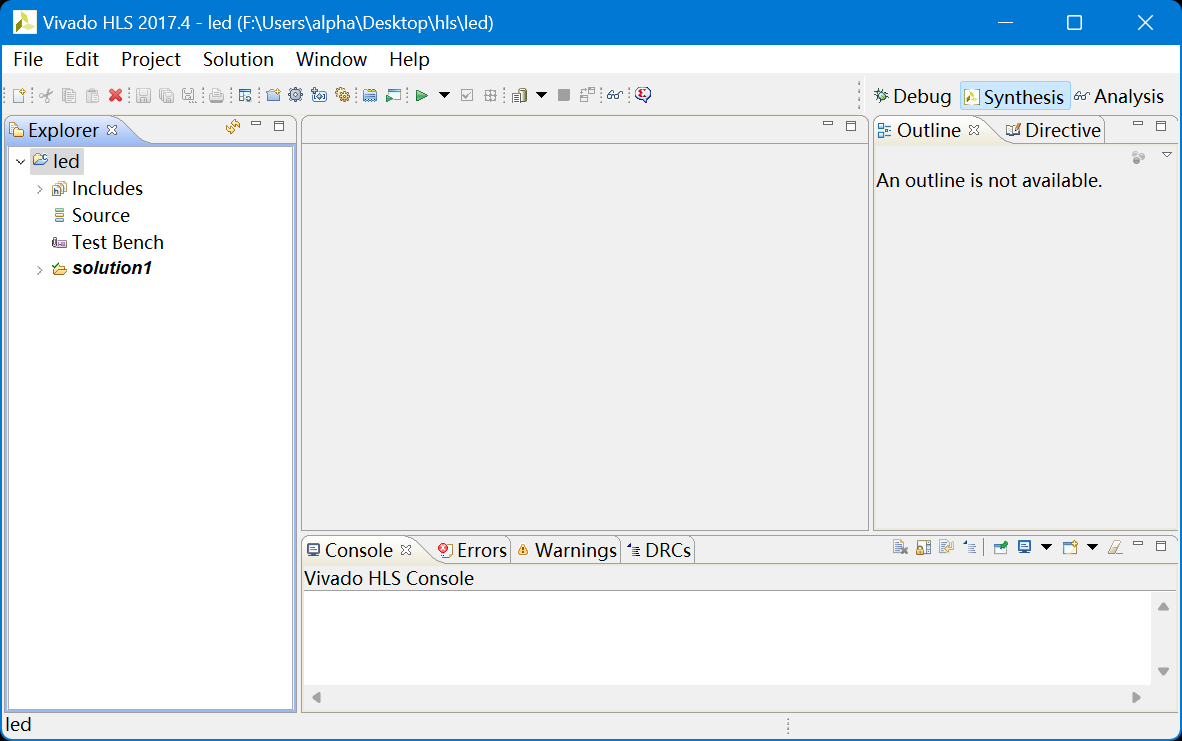

- 等待工程创建完毕,如图所示:

- 添加源文件,右键

Source-->New File:

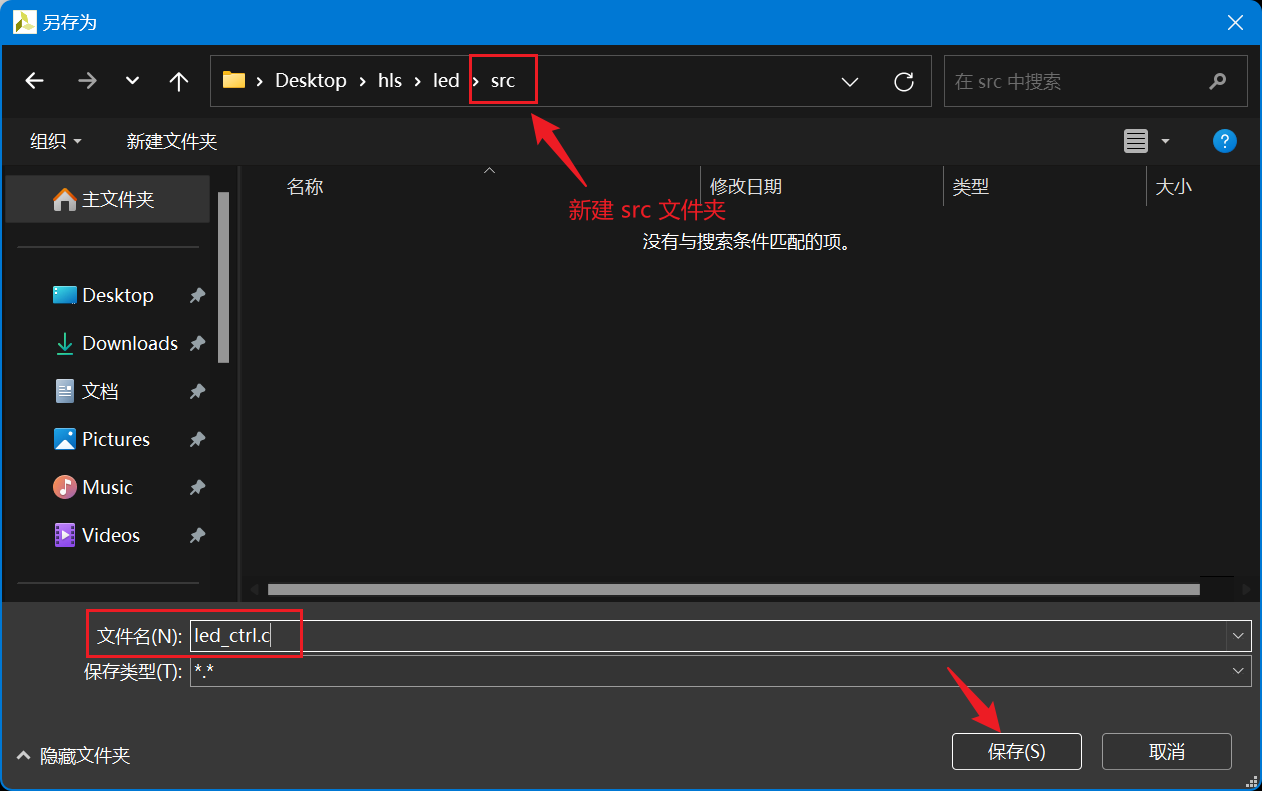

- 在工程目录下新建

src文件夹,创建.c文件,文件命名和顶层函数一致:

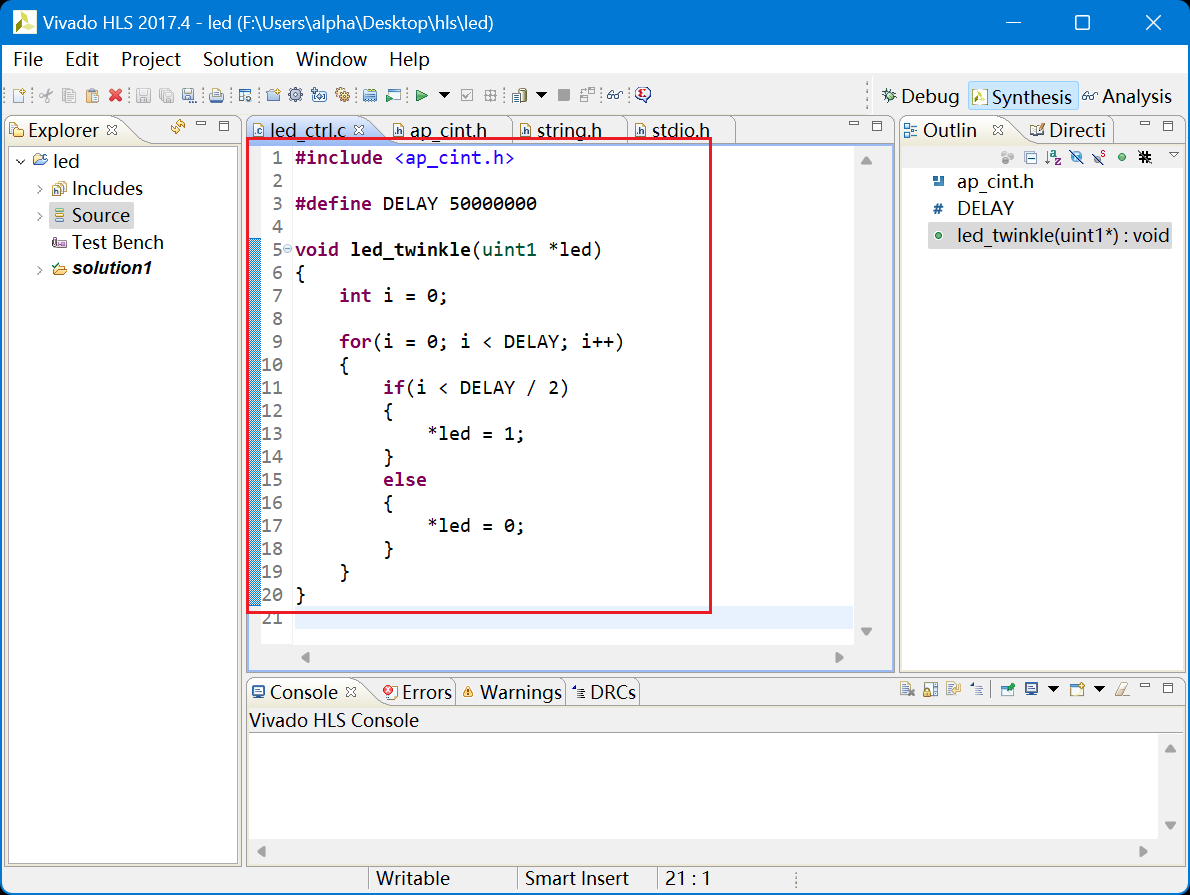

- 在源文件中添加源代码,代码功能是实现一个 LED 的闪烁:

#include <ap_cint.h>

#define DELAY 50000000

void led_ctrl(uint1 *led)

{

int i = 0;

for(i = 0; i < DELAY; i++)

{

if(i < DELAY / 2)

{

*led = 1;

}

else

{

*led = 0;

}

}

}

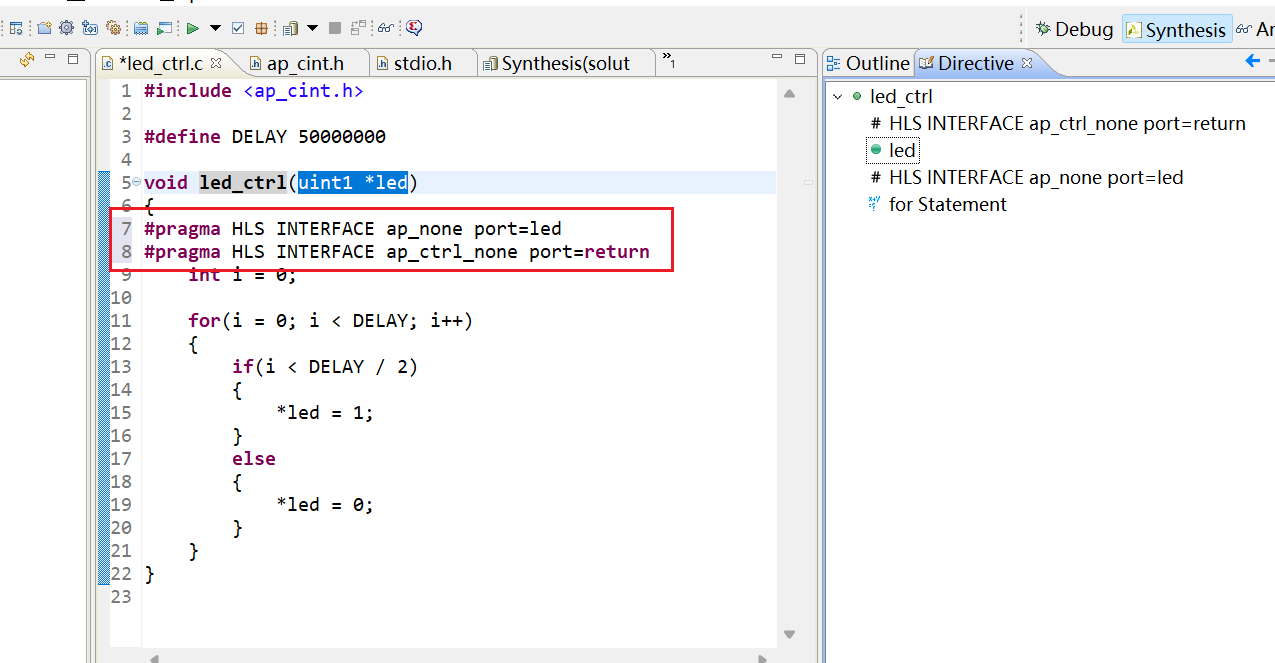

- 如下图所示:

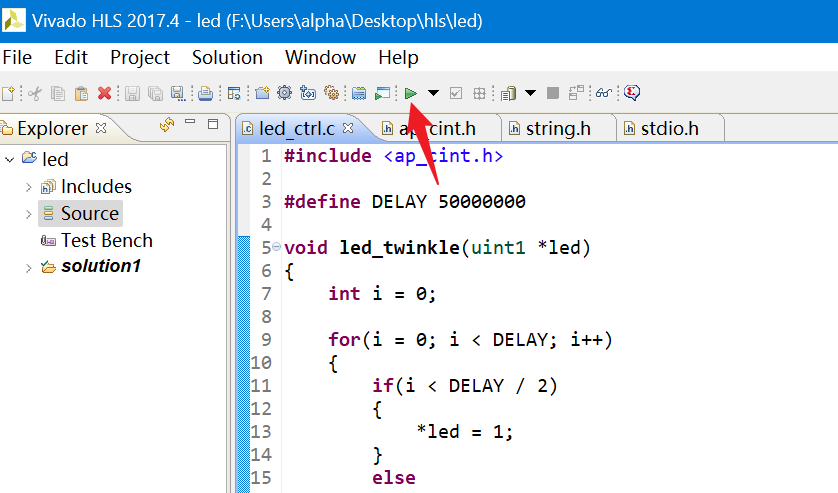

- 点击

Run C synthesis对代码进行综合:

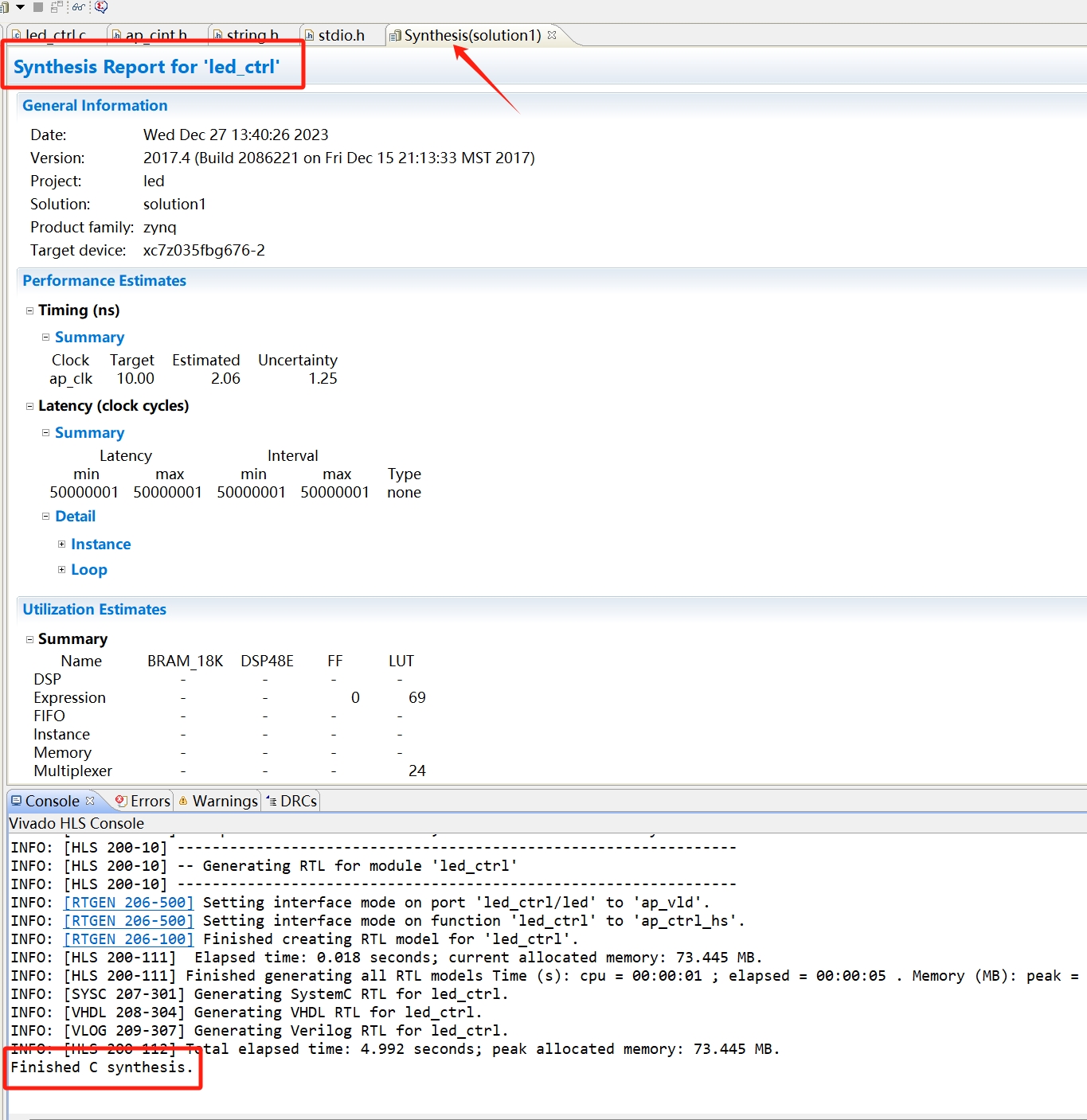

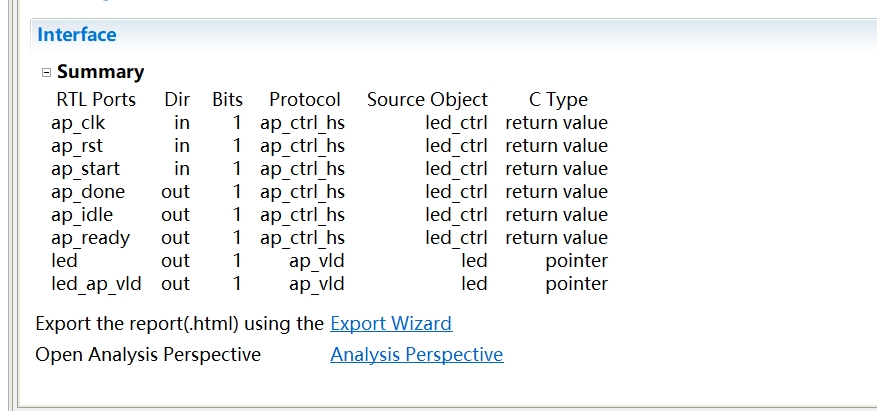

- 综合完成后可以查看综合报告:

- 重点关注生成的接口信息,如图所示:

- 此次我们实现的功能相对比较简单,采用更为简单的 ap_ctrl_none 和 ap_none 协议来综合,在源代码中添加两行指令:

#pragma HLS INTERFACE ap_none port=led

#pragma HLS INTERFACE ap_ctrl_none port=return

- 保存后再次进行综合:

- 综合完成后查看综合报告,端口简化了许多:

- 点击

Export RTL导出 IP:

- 保持默认设置,点击

OK:

- 等待导出完成:

- 在目录下可以看到导出的 IP:

- 如果在导出 RTL 时报如下错误:

IP 验证

- 创建 Vidado 基础工程,在工程目录下创建

ip_repo文件夹,将 HLS 创建的 IP 复制过来并解压缩:

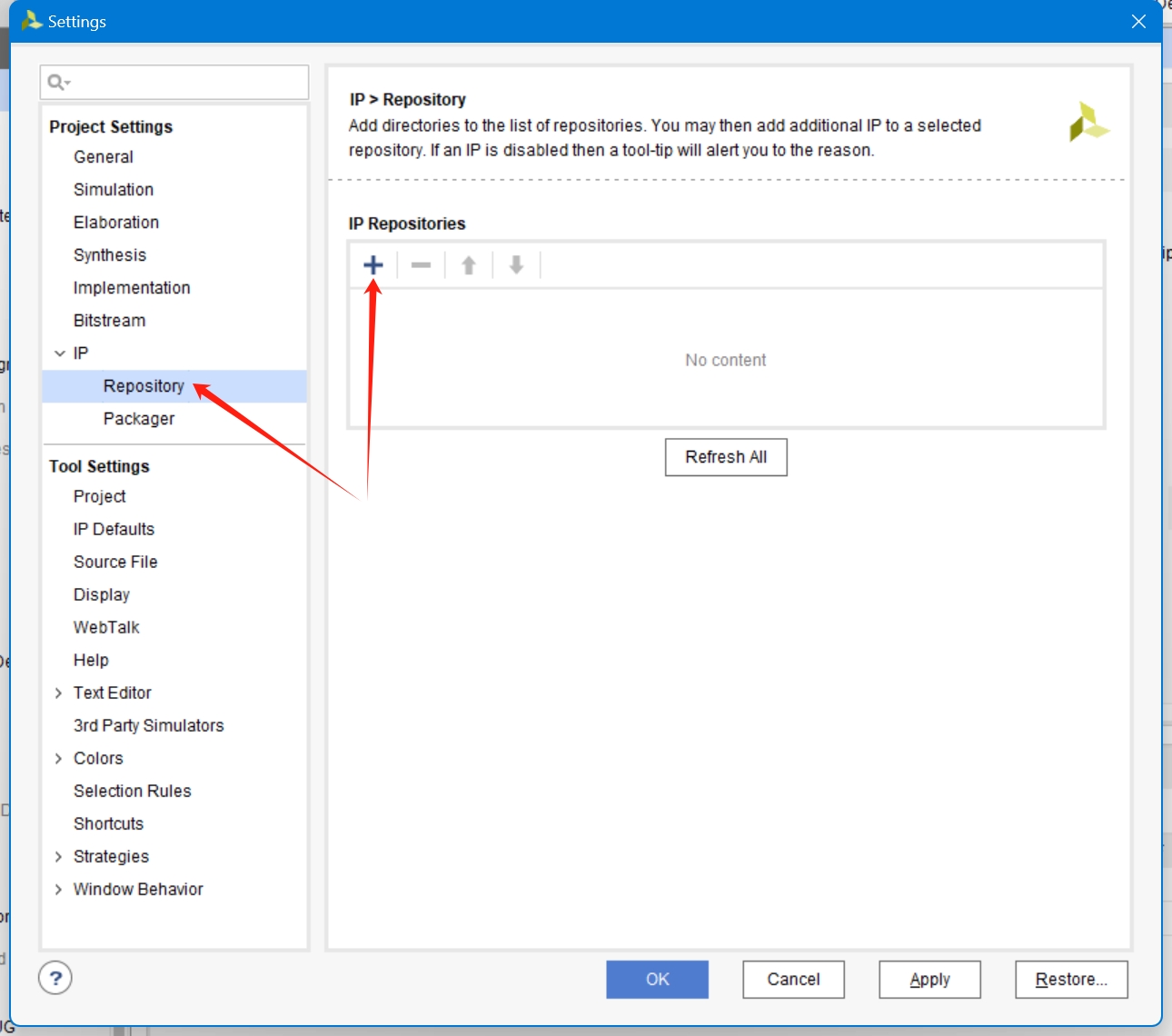

- 在 Vivado 中导入创建的 IP,点击菜单栏

Tool-->Settings:

- 点击

IP --> Repository,点击右侧+号:

- 找到 IP 存放路径,点击

Select:

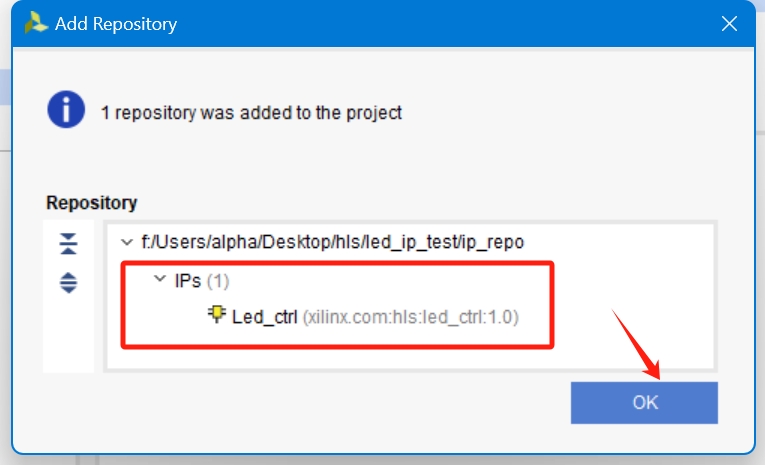

- 在弹出的界面中可以看到已经识别出来的 IP,点击

OK:

- 创建

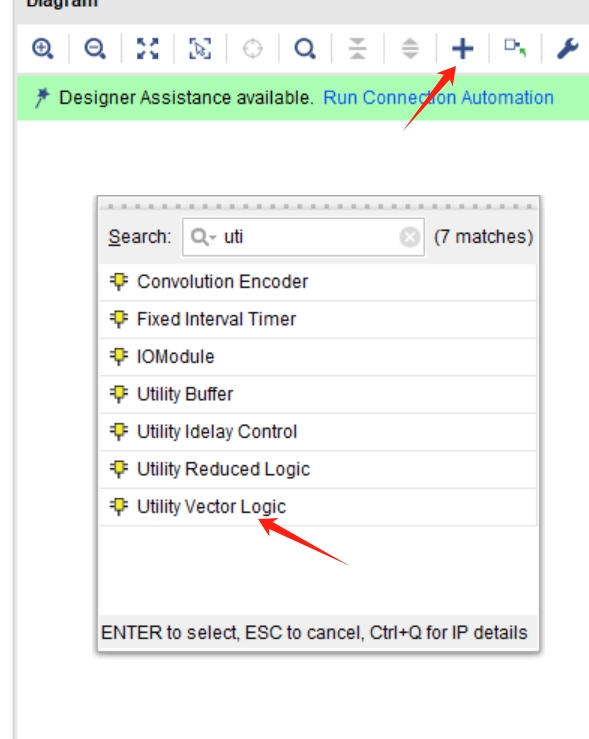

Block Design,首先导入一个Utility Vector Logic:

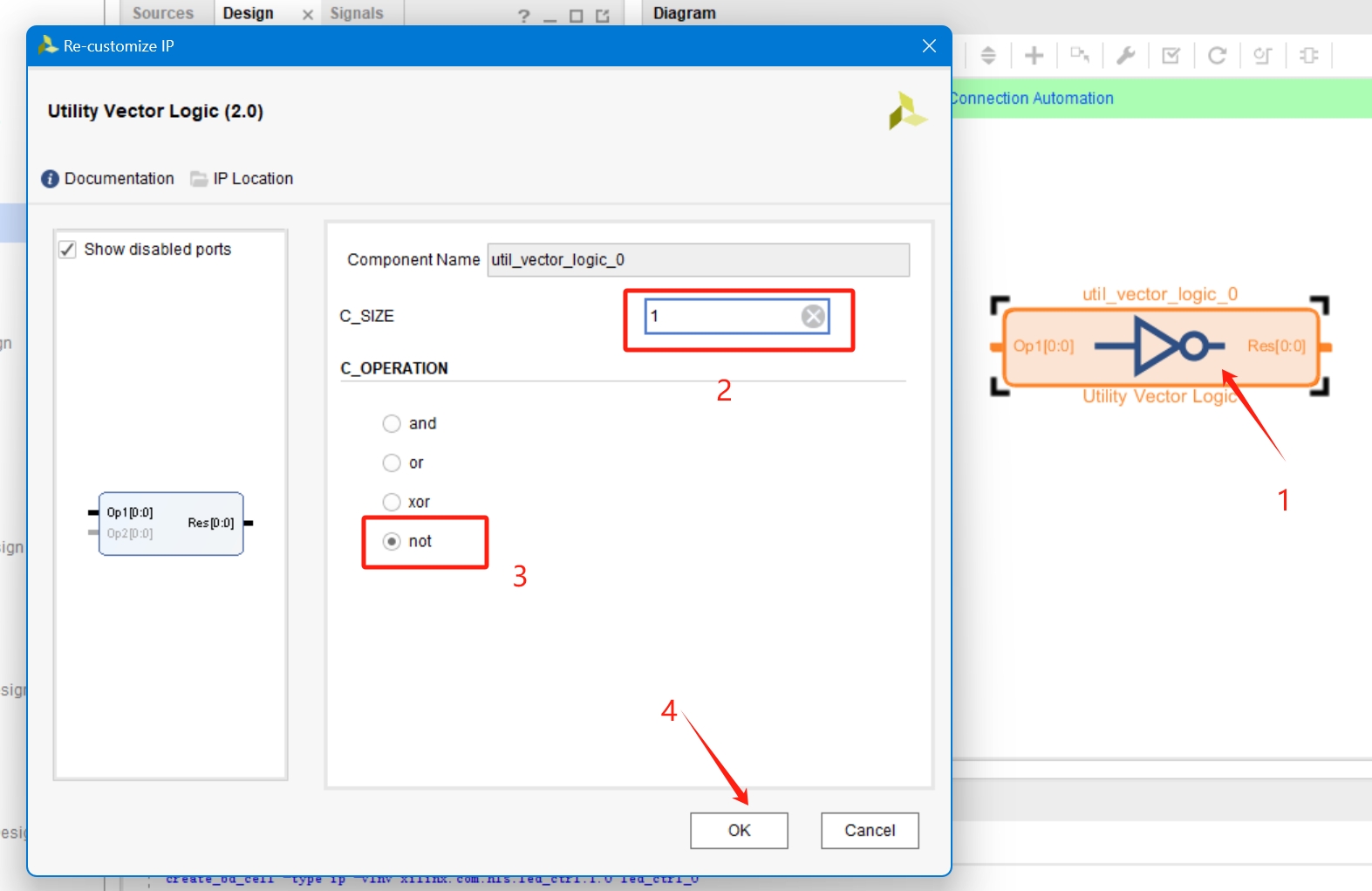

- 将其配置成

1位位宽的非门:

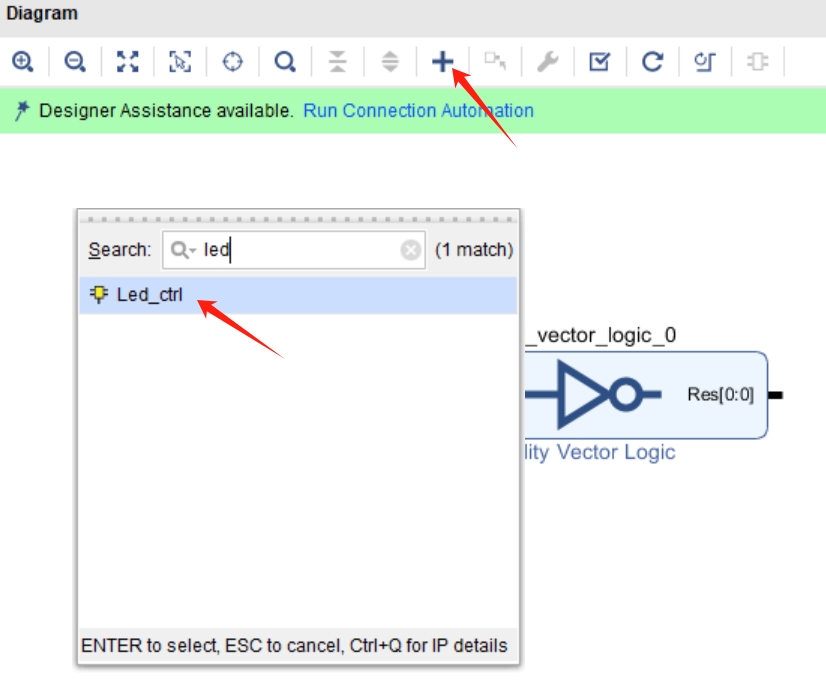

- 导入我们创建的 IP:

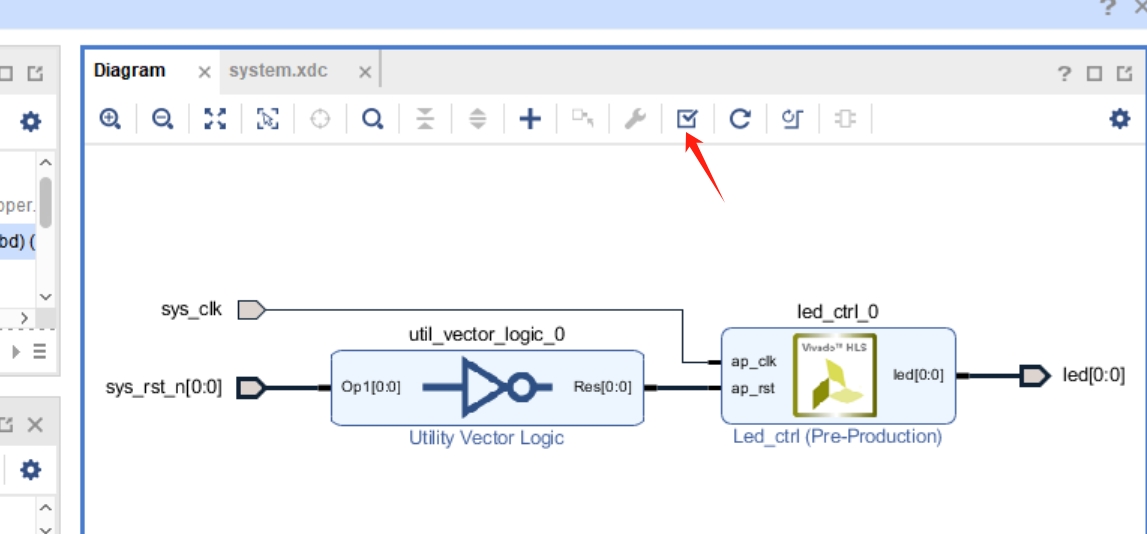

- 如图连接两个 IP 并创建外部端口:

- 选择

Validate Design验证设计,验证无误后保存设计:

- 执行

Generate Output Products和Create HDL Wrapper:

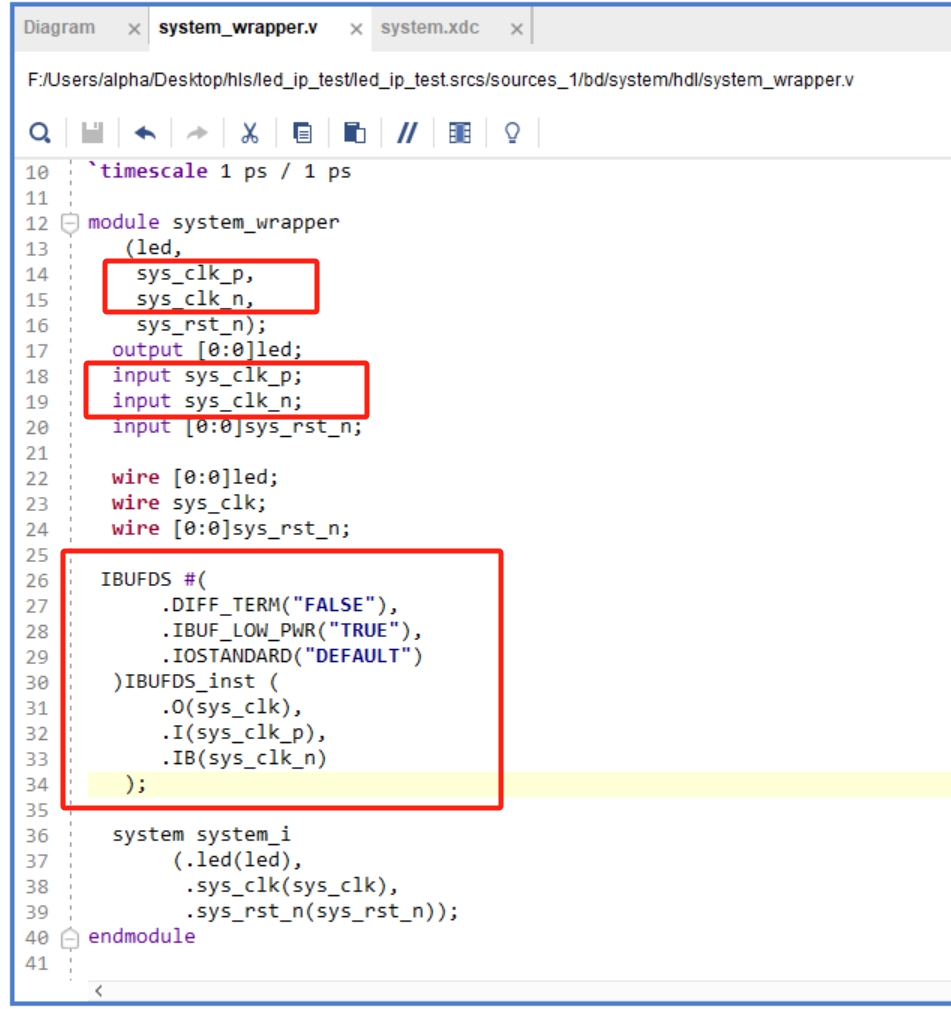

- 由于验证板卡时钟为差分输入,这里将

wrapper文件稍作修改:

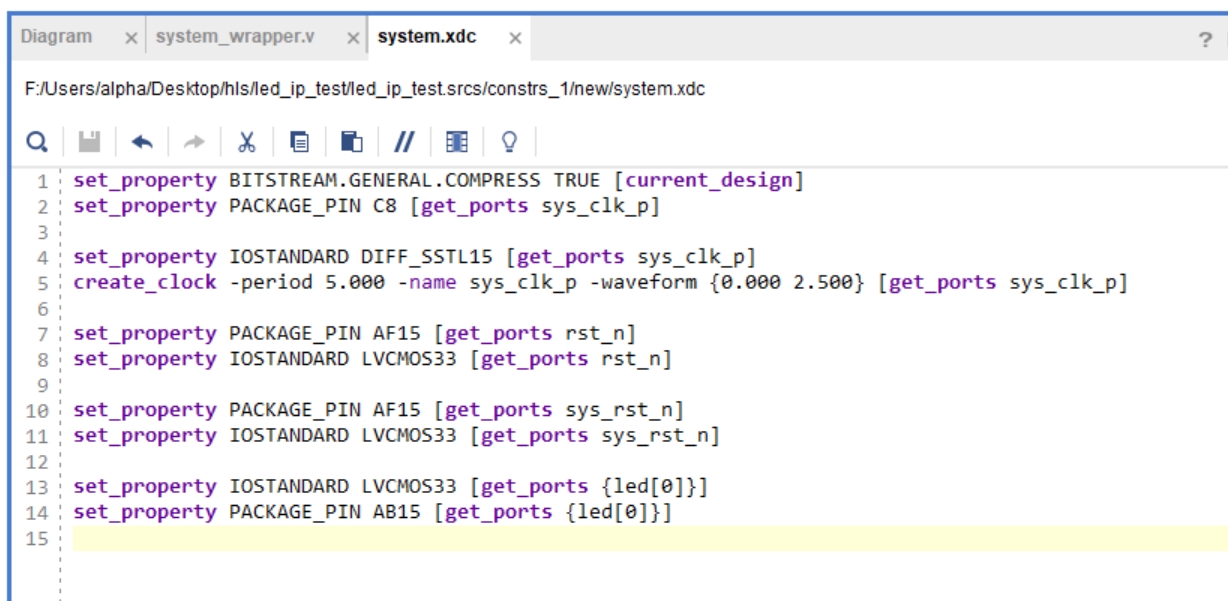

- 添加约束文件:

- 点击

Generate Bitstream,对设计进行综合、实现、并生成 Bitstream 文件。

板级验证

- 将比特流文件下载到开发板中,实现效果:

参考来源

- 正点原子领航者

- 黑金 ZYNQ7035

更多内容

文章来源:https://blog.csdn.net/weixin_44550536/article/details/135250360

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 2023版本QT学习记录 -11- 多线程的使用(QT的方式)

- 计算机视觉与美颜SDK:详解人脸美型功能的实现过程

- 大中台,小前台:打造快速响应市场的企业竞争力

- Vue3 面试题

- 【大数据进阶第二阶段之Hadoop学习笔记】Hadoop 运行模式

- [Angular] 笔记 19:路由参数

- C++ STL priority_queue容器详解

- 抖音商品详情API:开启电商应用新纪元

- XSS语句

- 一起玩儿物联网人工智能小车(ESP32)——16. 用ESP32的GPIO控制智能小车运动起来(MicroPython)