实验九 基于FPGA的计数译码显示电路设计

发布时间:2023年12月30日

基本任务一:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW4-7控制数码管位选

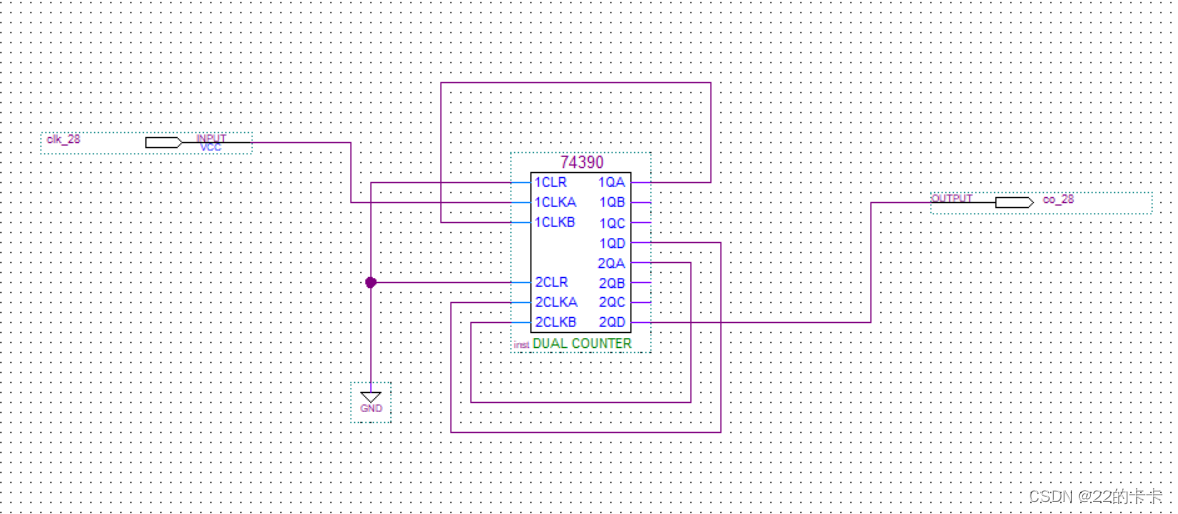

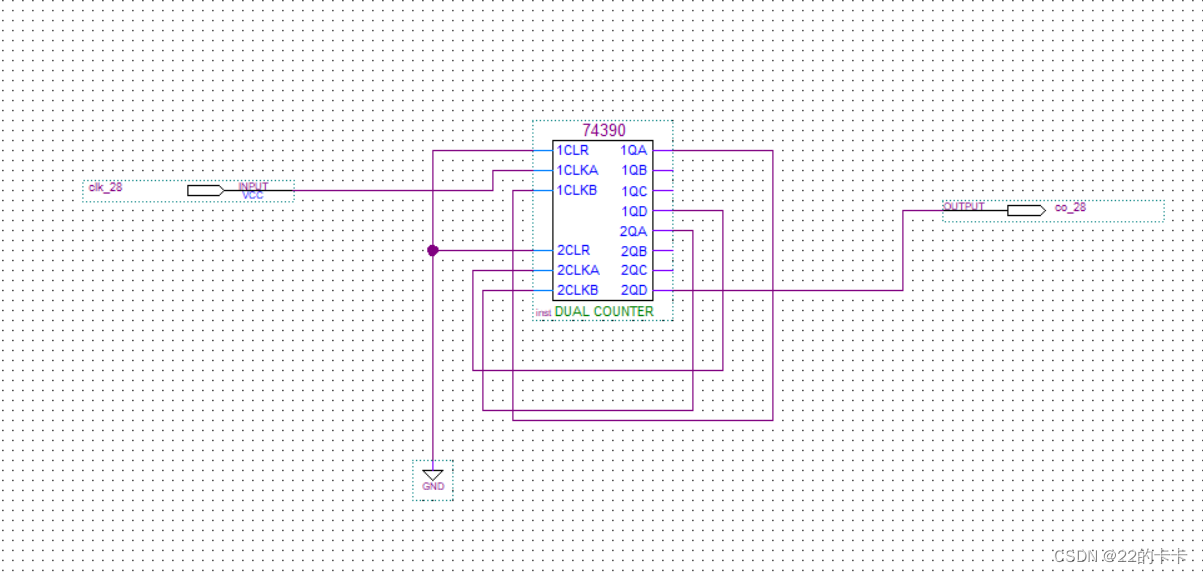

m100:

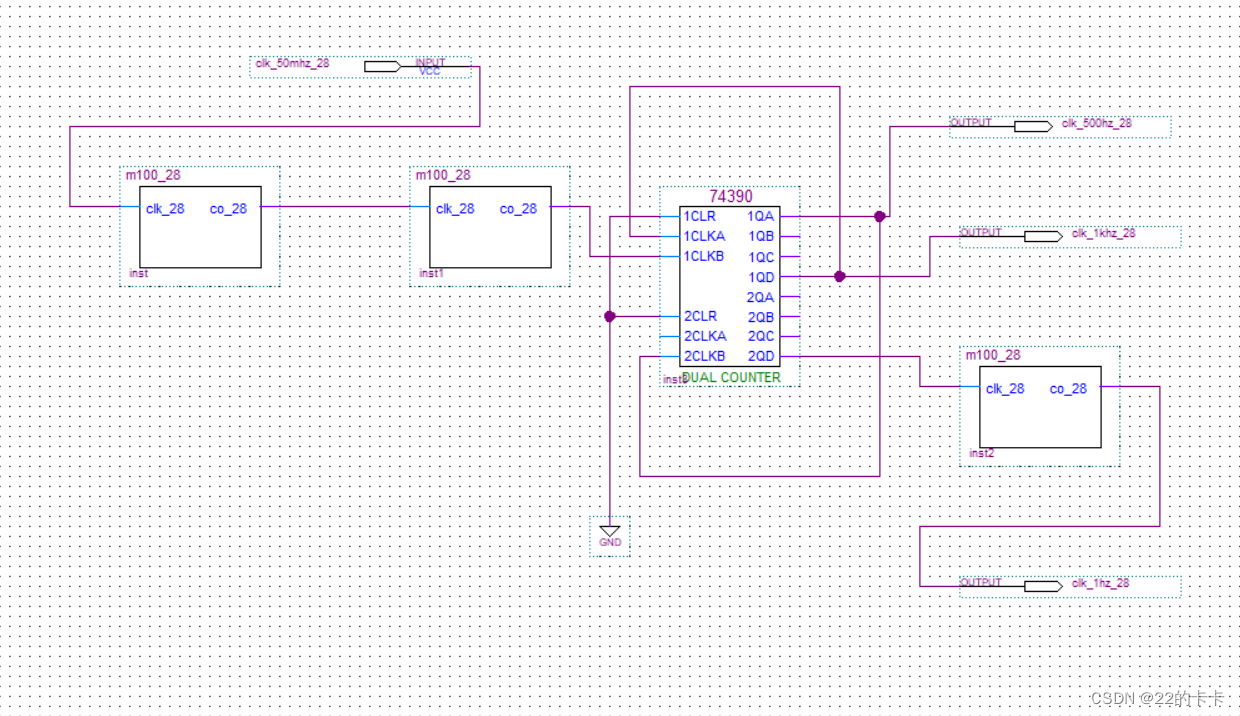

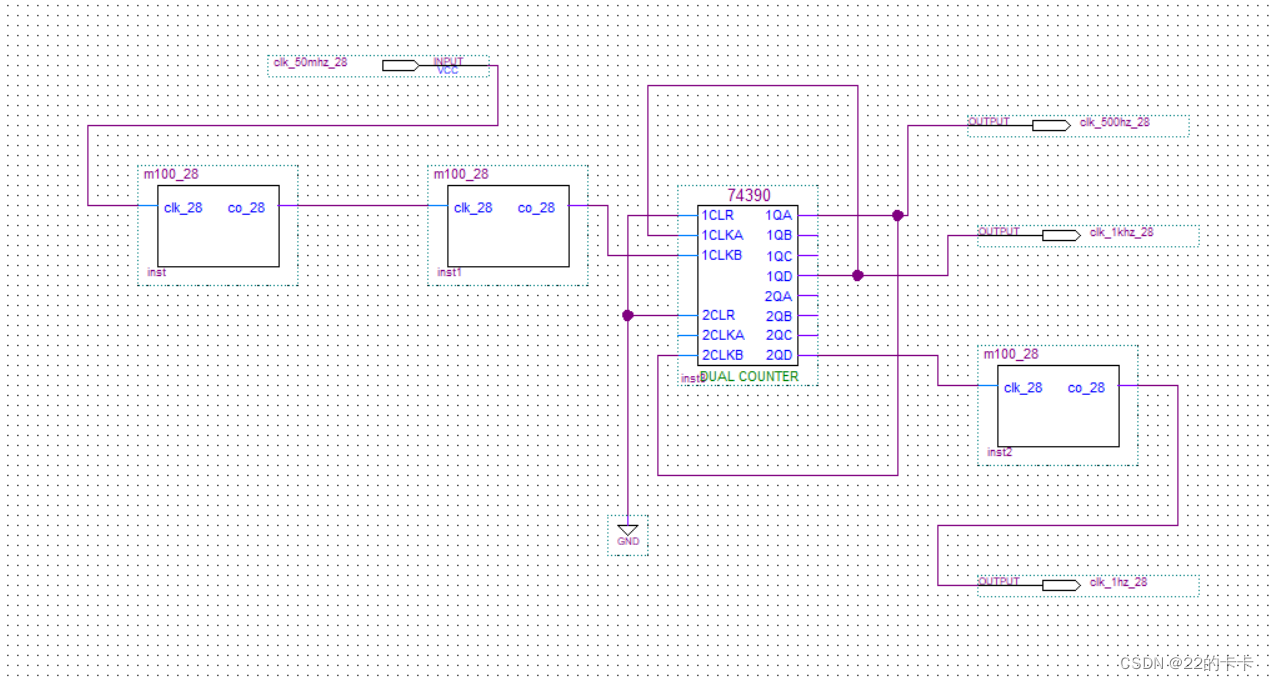

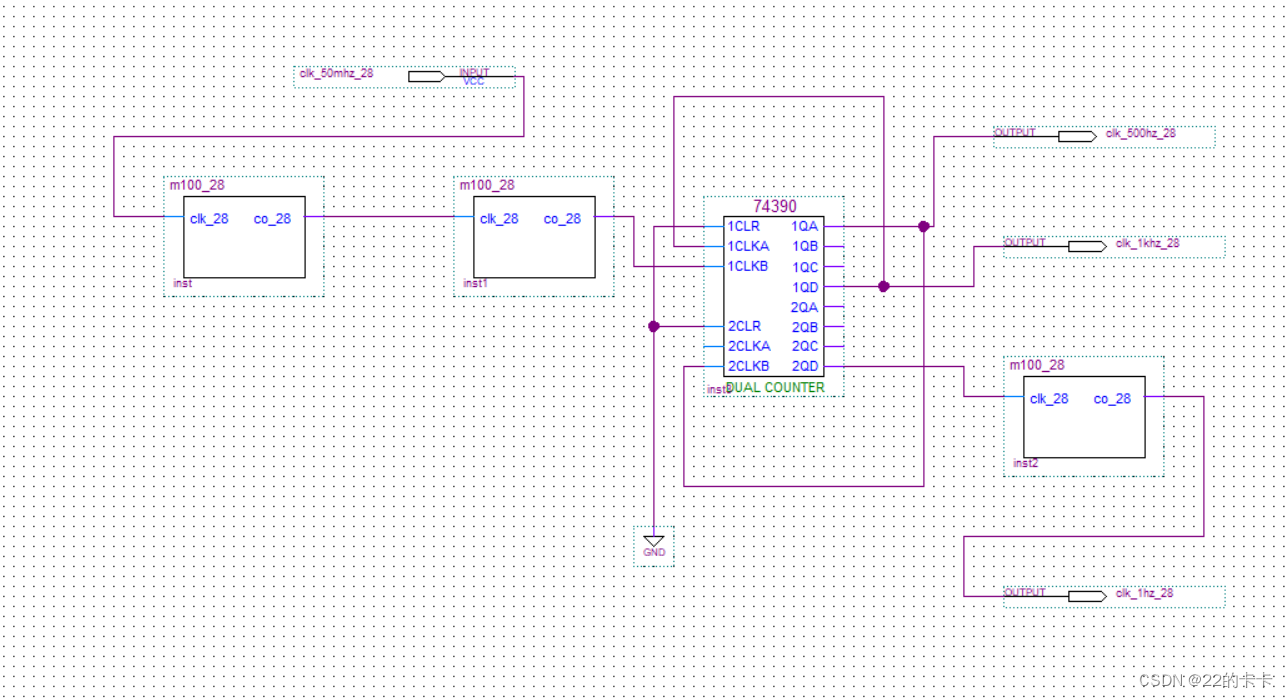

frediv:

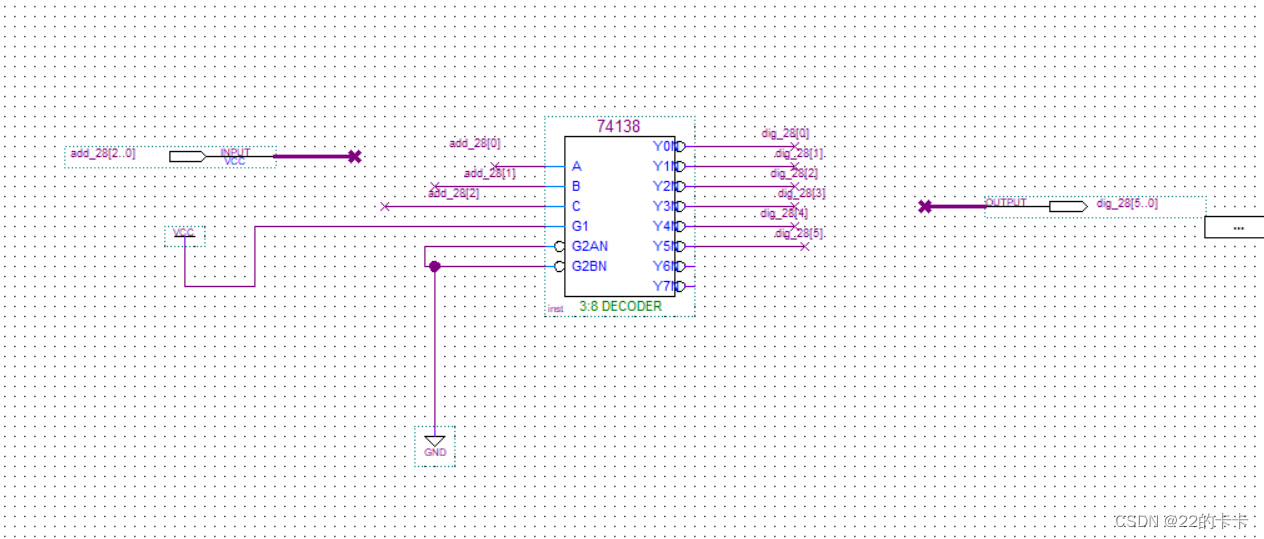

decoder:

基本任务二:利用FPGA硬件平台上的4位数码管显示m10技术结果

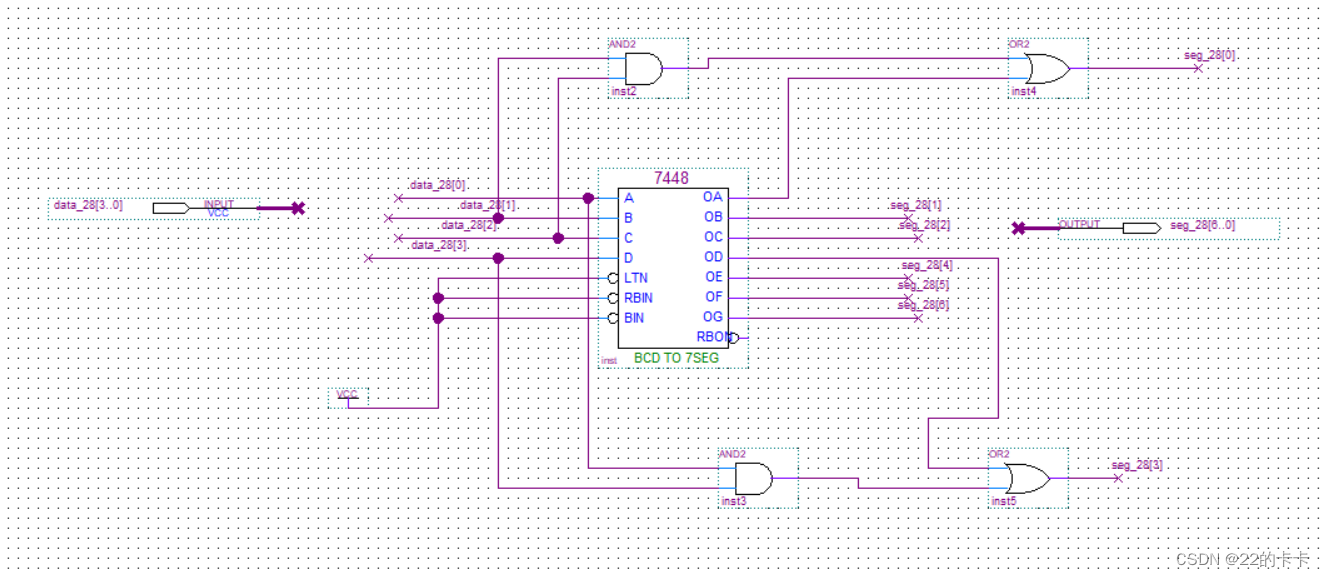

扩展任务一:对7448译码的6和9进行补段

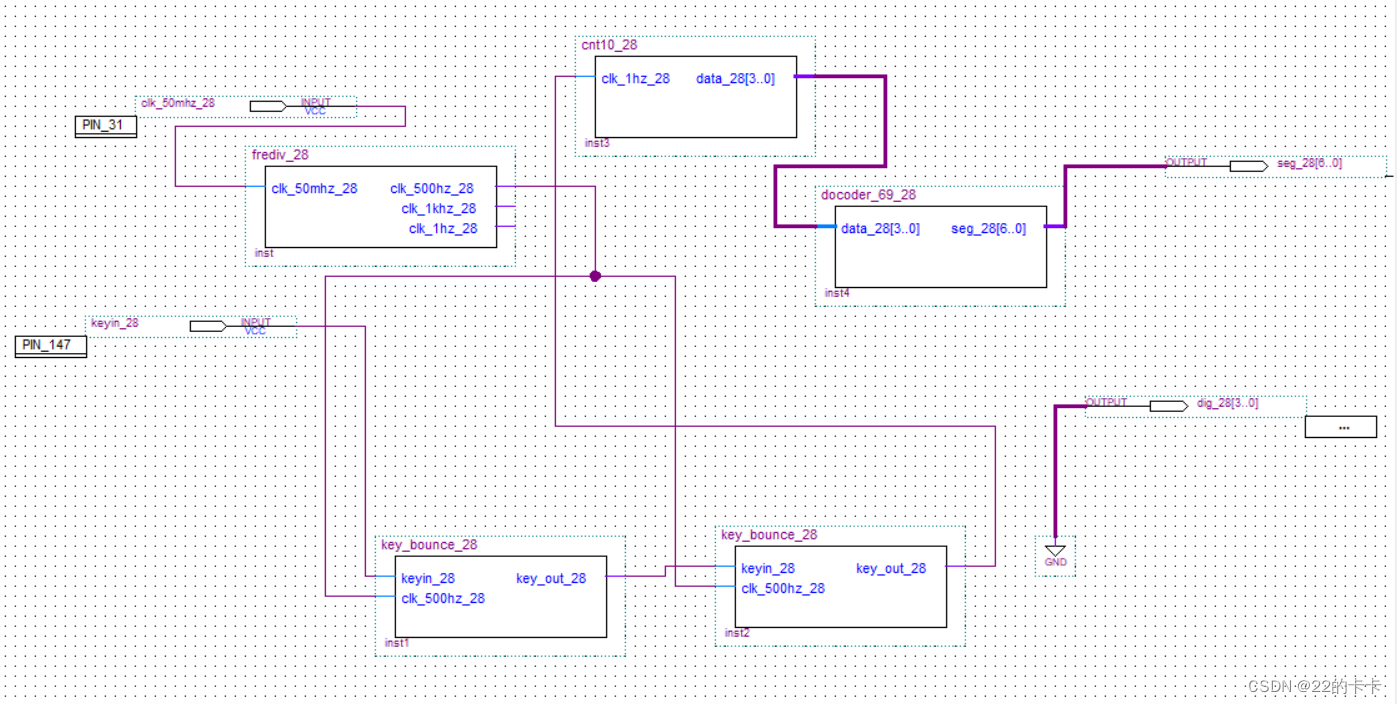

扩展任务二:用按键控制计数器从0-9计数,4位数码管显示技术结果。

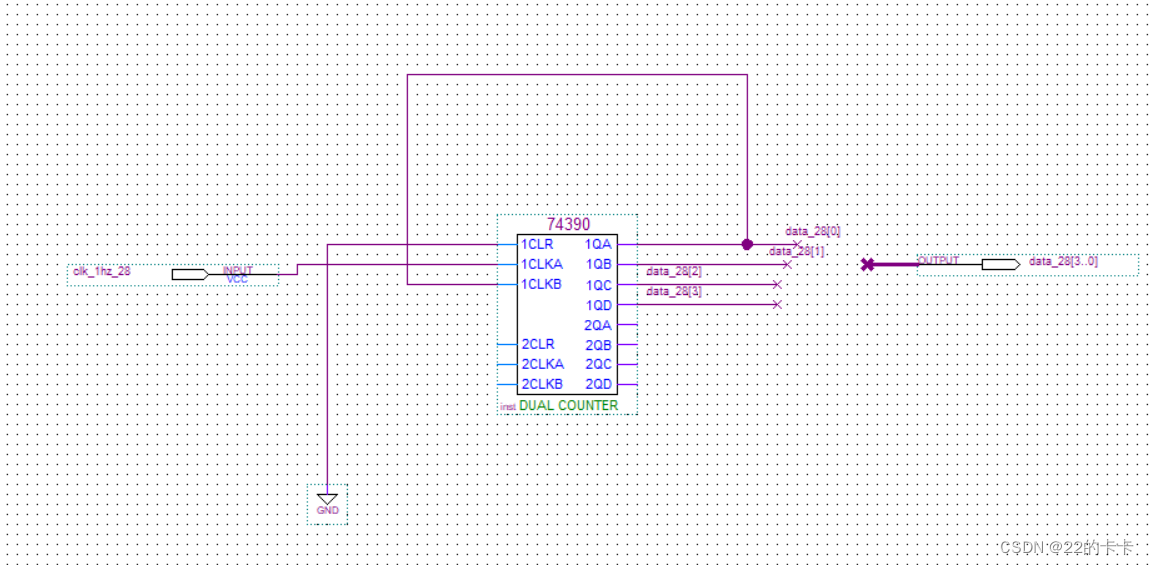

cnt10:

decoder69:

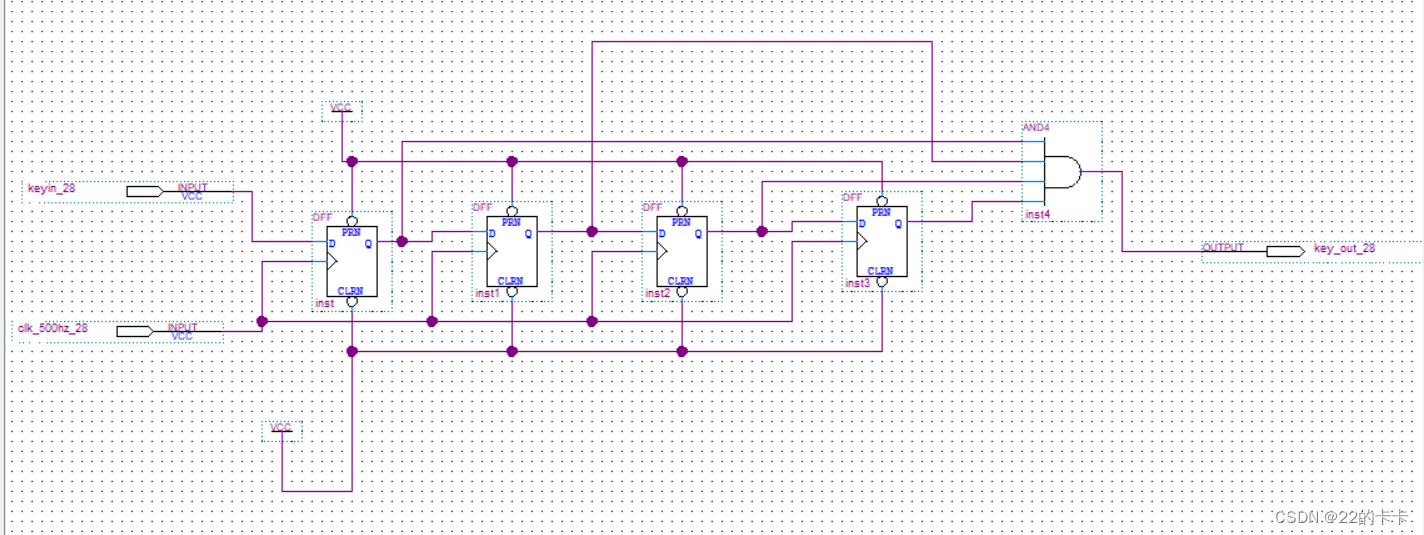

key_bounce:

frediv:

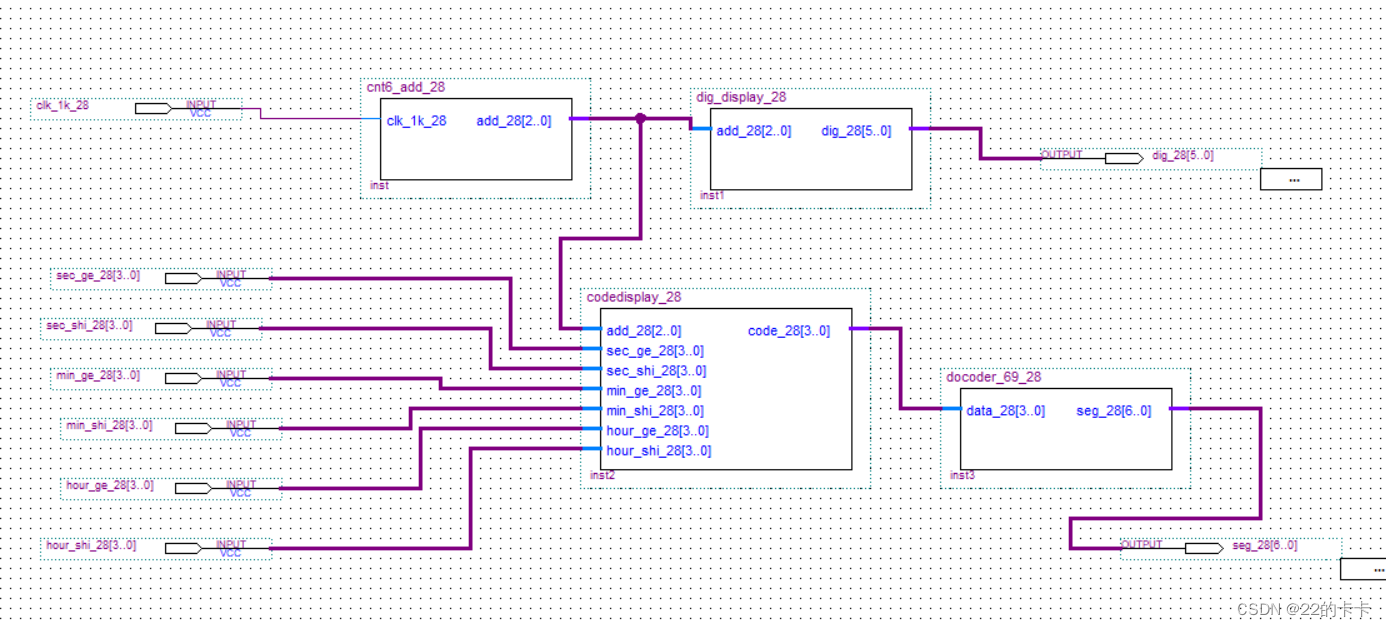

基本任务三:利用FPGA硬件平台上的6位数码管显示模100计数结果。

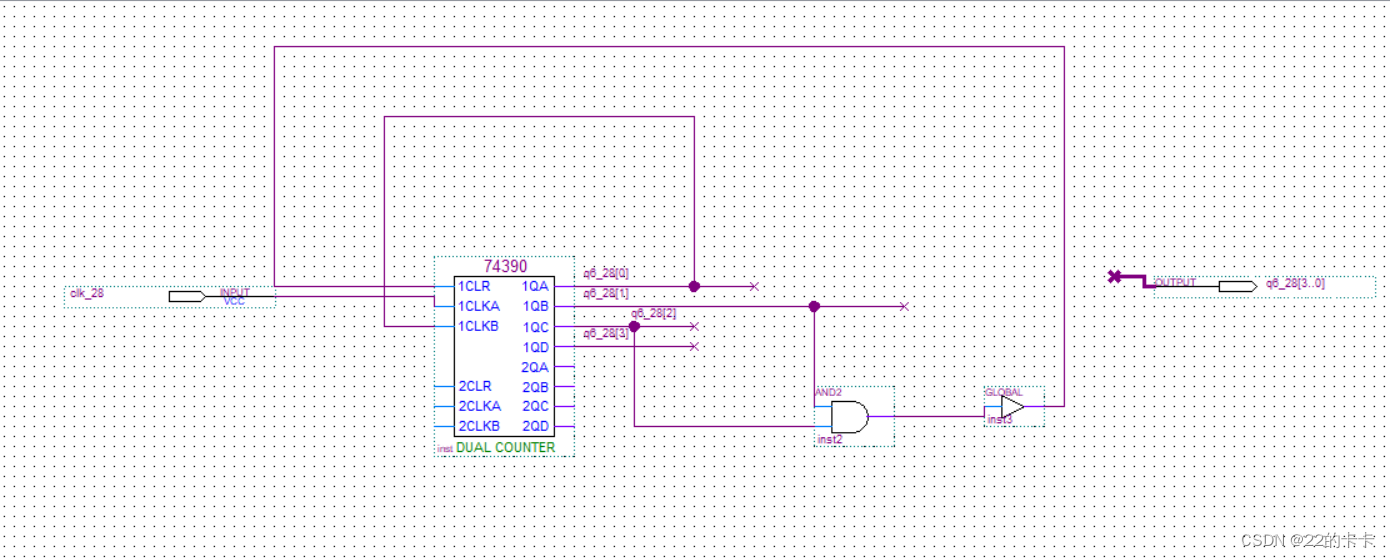

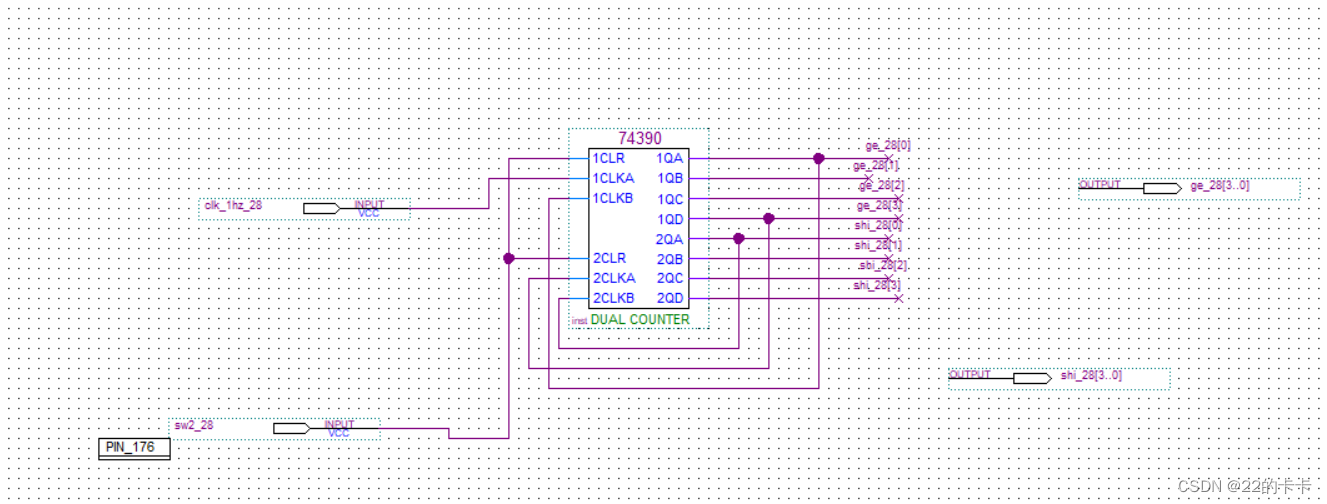

cnt6:

m100:

frediv:

decoder——69:

m100_2output:

dig_select:

code_select:

display_m100:

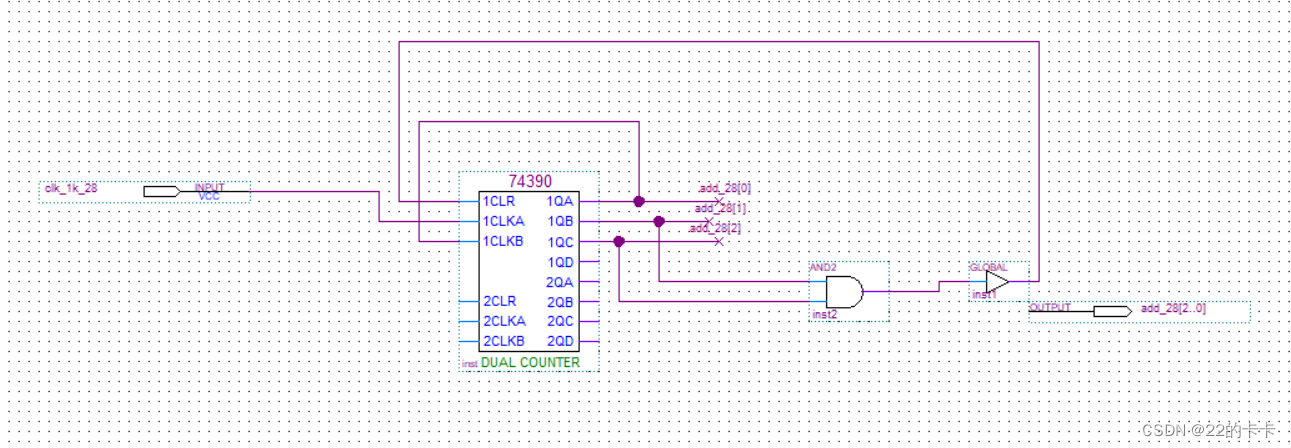

cnt6_add

文章来源:https://blog.csdn.net/m0_73605862/article/details/135306785

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 影剧联动成热门生意,同一个IP能让观众持续买单吗?

- L1-007 念数字(Java)

- PHP调用淘宝/拼多多电商平台商品详情API接口的方法及实现

- 大数据小白初探HDFS从零到入门(一)

- C#的String.ToCharArray 方法

- 模拟适配器设计方案:360-基于10G以太网的模拟适配器

- LeetCode刷题--- 下降路径最小和

- 学习Go语言Web框架Gee总结--上下文Context(二)

- 回归预测 | Matlab实现DE-BP差分算法优化BP神经网络多变量回归预测

- 720VR全景通微信小程序商业运营版+多用户+云储存+大图切图效率高+完整的代码包以及搭建教程 功能强大