Original PIPE and Serdes PIPE

发布时间:2024年01月23日

PIPE is PHY Interface for PCIE ,STAT, USB, DispalyPort and Converged IO,上述协议都可以使用这种通用接口。

它是连接物理层PHY 与 MAC( 或者是Link layer ASIC)。PIPE 的技术规范是在上述几种规范基础上发展来的,如果PIPE规范与上述规范有冲突以上述规范为准。

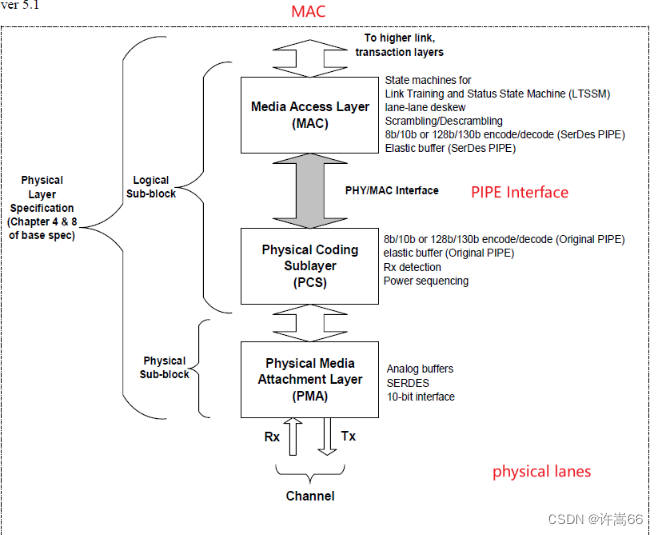

PCIE PHY 系统结构框图如下所示,它包括逻辑子层(编解码),物理子层(数据的模数转换)。

Original and Serdes PIPE

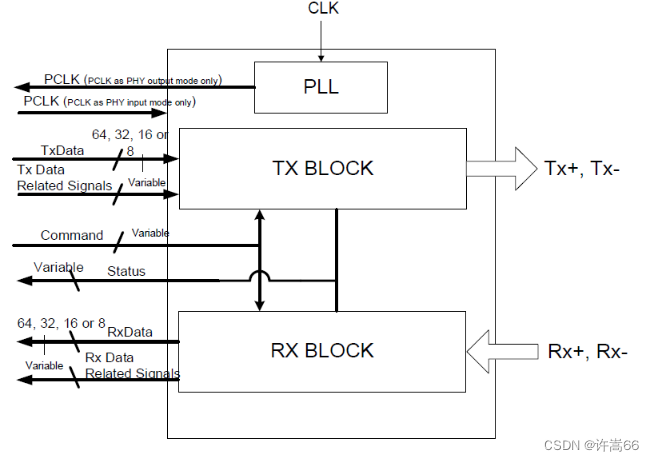

下图表示兼容 PIPE协议的PHY 功能框图,右侧为RX TX的差分线对,左侧是PIPE标准接口的MAC。

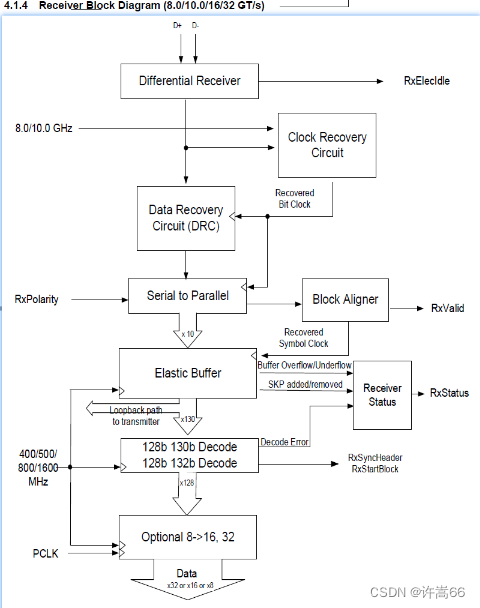

1 Original PIPE Architecture

从图中可以看到original pipe是通过标准的pipe接口与MAC交互,数据的编解码集成在phy部内部。

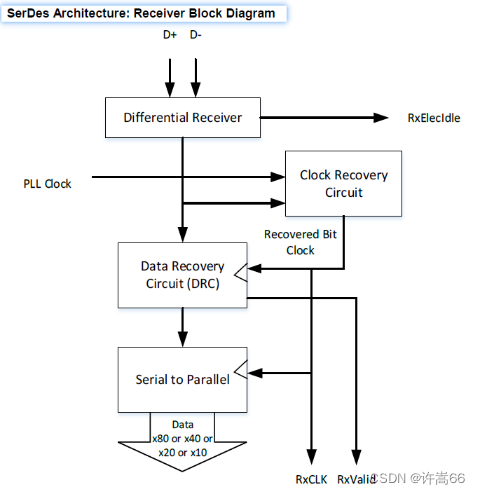

2 Serdes PIPE

相比于Original PIPE,serdes pipe 仅包含很小的数字逻辑,这部分逻辑主要是关于串并转换的。 Loopback的逻辑

都是在MAC层实现。 这种模式下的TX 主要是负责将来自MAC的PIPE形式的并行数据转换成串行数据,RX主要是负责将差分线

上的数据封装成并行数据(包括CDR后的clk)并转发给MAC,

文章来源:https://blog.csdn.net/qq_41496495/article/details/135775466

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!