基于HFSS的微带线特性阻抗仿真-与基于FDTD的计算电磁学方法对比(Matlab)

基于HFSS的微带线特性阻抗仿真-与基于FDTD的计算电磁学方法对比(Matlab)

工程下载:

HFSS的微带线特性阻抗仿真工程文件(注意版本:HFSS2023R2):

https://download.csdn.net/download/weixin_44584198/88748285

基于FDTD的微带线特性阻抗仿真Matlab工程:

https://download.csdn.net/download/weixin_44584198/88748215

目录

1、微带线特性阻抗仿真基础

微带线特性阻抗的仿真是电磁学里面一个比较基本的仿真了,很多学校都会把这个当成HFSS学习的作业来弄。当然,微带线阻抗的仿真和实际的测量是有一定差别的,在仿真时候我们可以用波端口或者使用CPML边界截断,而实际测量的话手段是非常有限的。感兴趣可以阅读:

利用矢网测试PCB走线的特性阻抗

第二章 微带线阻抗实验

这种基于四分之一阻抗线的实际测量方法只能大概测一下,因为不同频率下的特性阻抗实际都是不一致的,要不然SMA接口还分0-6Ghz、0-10GHz那么多类型干嘛。

当然,有些刚刚入门的小伙伴会问了,特性阻抗不是可以使用公式进行计算的嘛,确实是这样的,但是这种是基于大量近似的计算,其精度必然没有电磁学方法准确。那么我们来给出今天的一个简单的案例:

基板:Rogers5880(相对介电常数2.2,损耗角正切0.0009)

结构:背板覆铜,正面信号线(微带线)

参数:铜厚35um,微带线宽为1mm,板子高度为1mm

目标:计算1-10GHz的该微带线特性阻抗

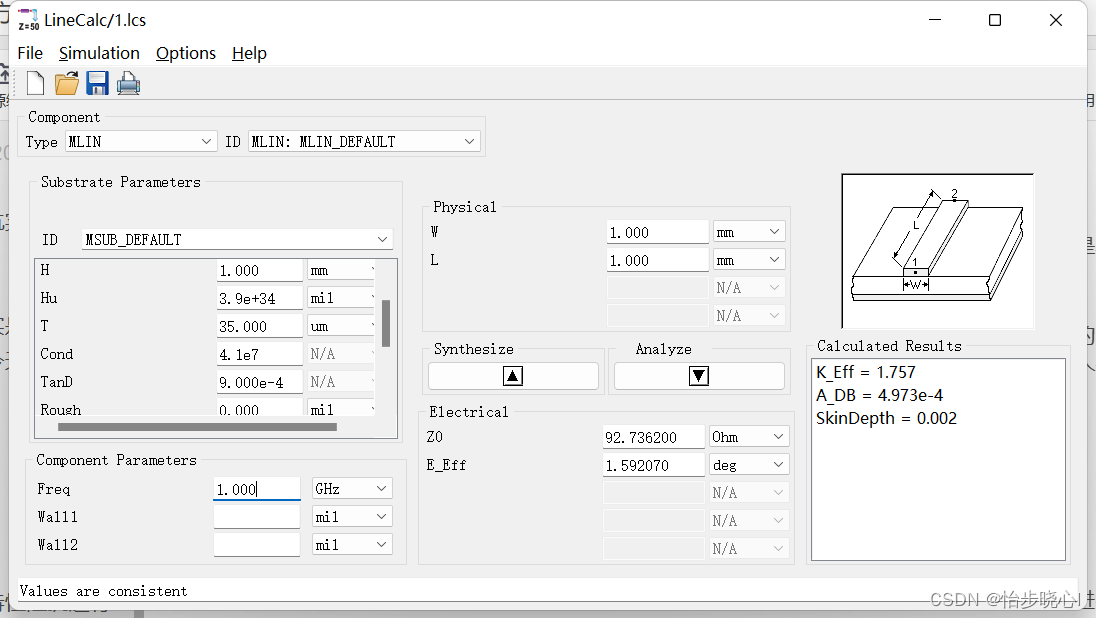

事实上,使用上面的这些参数,我们已经可以使用市面上常见的特性阻抗计算工具对特性阻抗进行计算了,比如ADS自带的计算工具linecalc:

计算出来的结果也非常明确,该结构在1GHz的特性阻抗为92.7欧姆。之前也提到,微带线特性阻抗对于不同频率是变化的,在10GHz处,计算出来的特性阻抗为93.6欧姆。使用linecalc工具得到的结果如下表,其基本的趋势是频率越高特性阻抗越大:

| 频率 | 特性阻抗 |

|---|---|

| 1GHz | 92.736200 |

| 2GHz | 92.741900 |

| 3GHz | 92.758900 |

| 4GHz | 92.796500 |

| 5GHz | 92.859500 |

| 6GHz | 92.950900 |

| 7GHz | 93.073200 |

| 8GHz | 93.228200 |

| 9GHz | 93.417100 |

| 10GHz | 93.640700 |

2、使用HFSS确定微带线特性阻抗

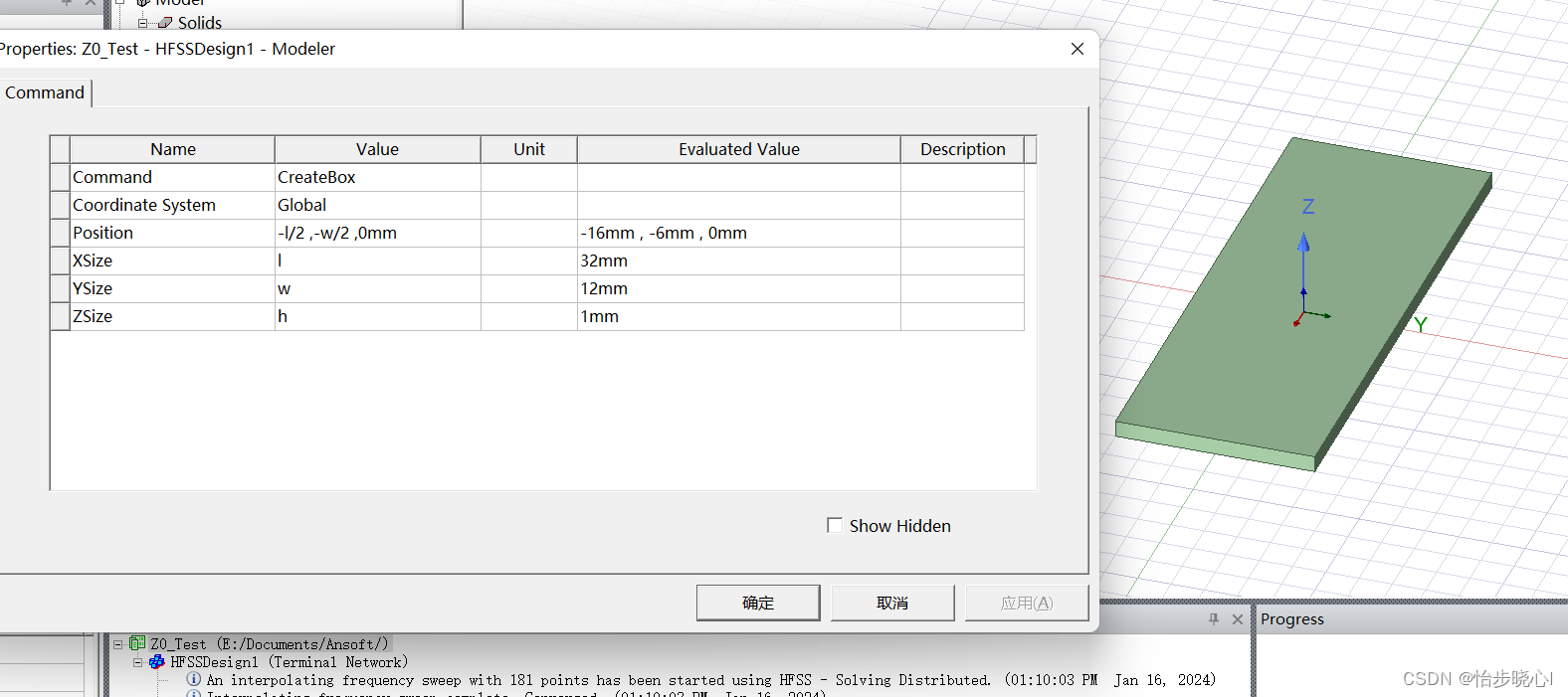

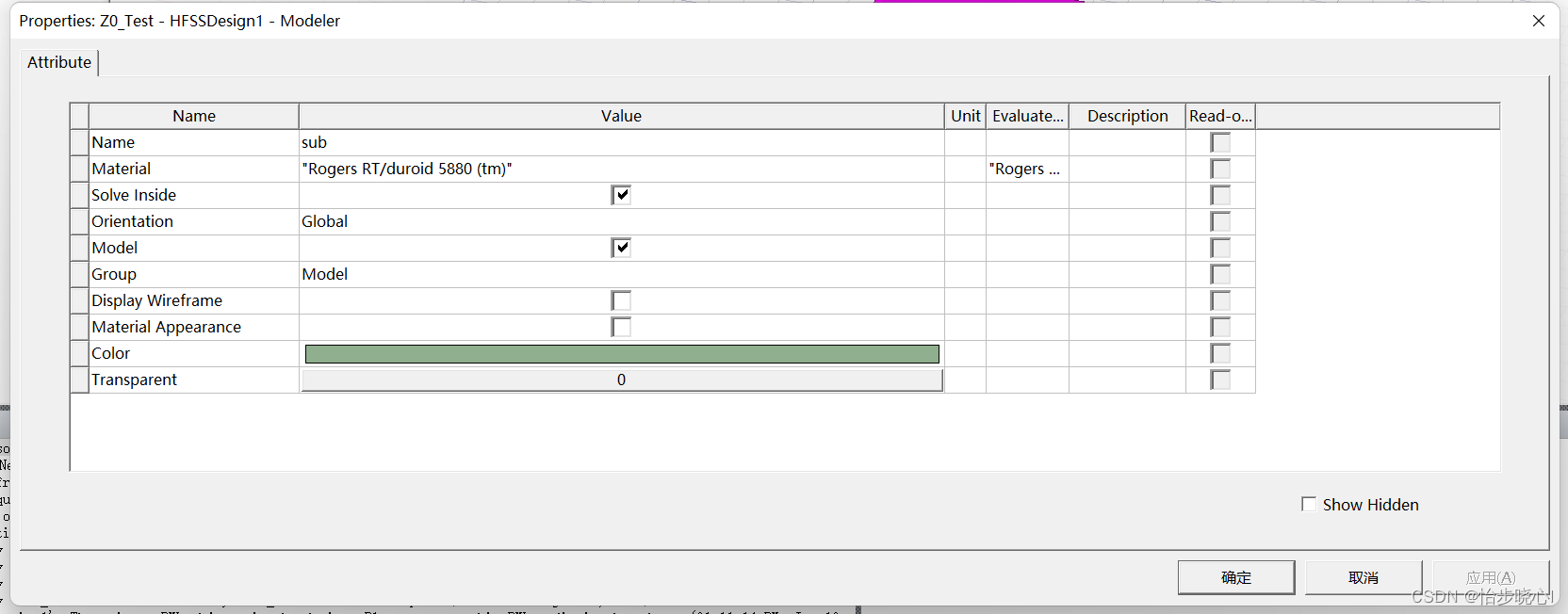

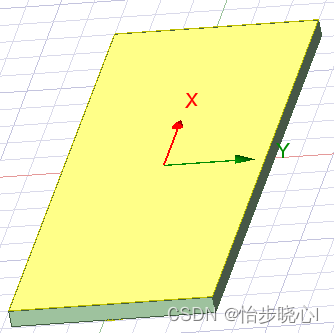

2.1、创建基板

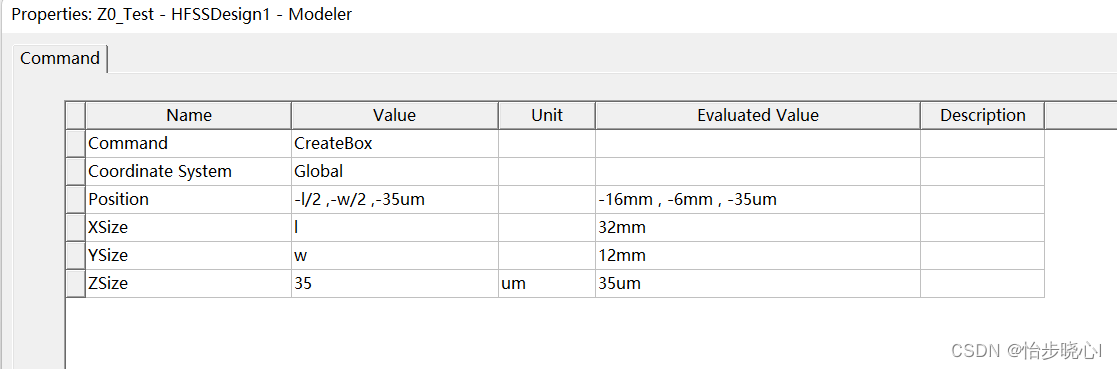

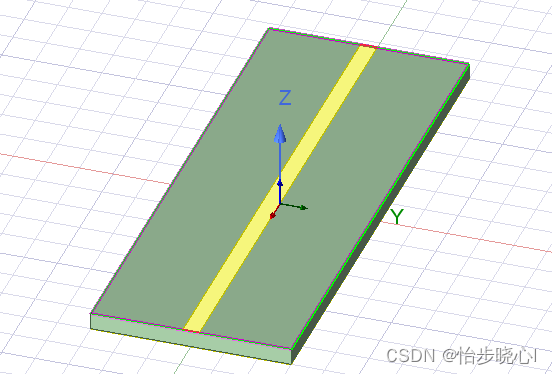

首先创建基板,基板材料直接选5880就行,这个材料的相对介电常数2.2,损耗角正切0.0009,设置基板的高h=1,宽度一般为线宽的11倍左右,此处微带线线宽是1mm,因此板材的宽被设置为12mm,长度随意设置,美观就行,此处长设置为32mm:

2.2、背面覆铜

然后就是设置铜皮的位置了,此处我们底部是全部覆铜的,厚度为35um:

2.3、信号线覆铜

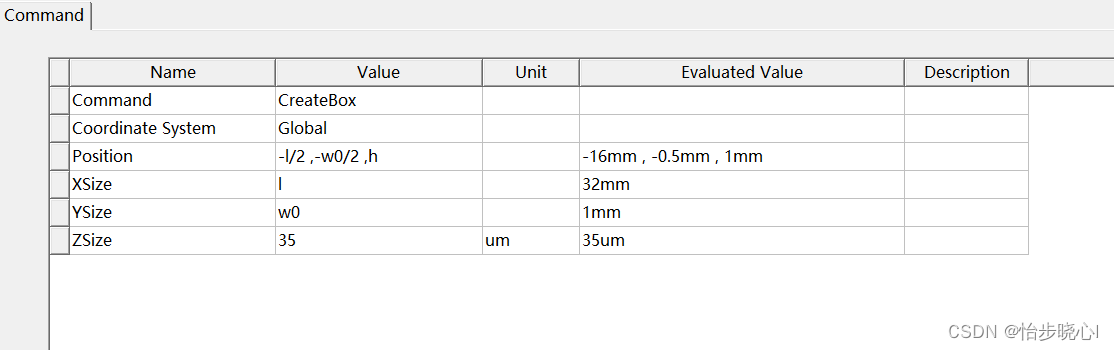

我们的顶部是信号线,也就是宽度为1mm的微带线:

2.4、设置空气盒子

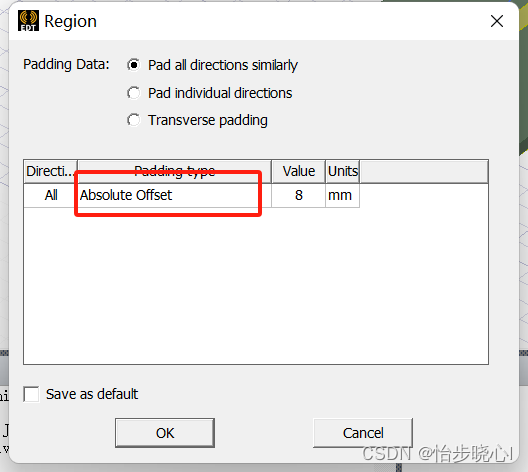

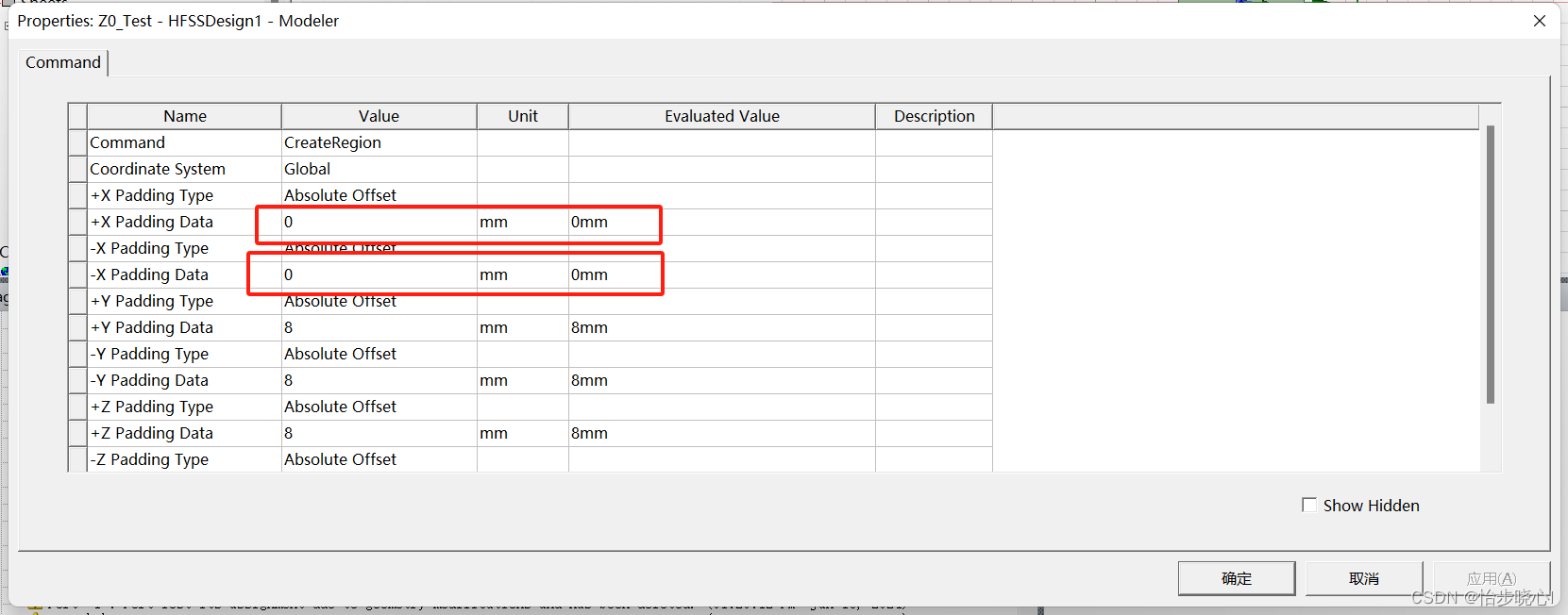

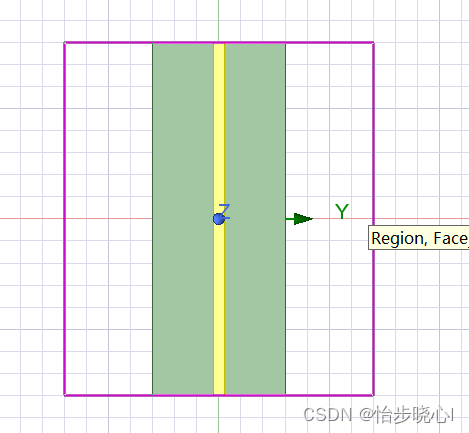

下一步就是设置空气盒子了,一般要原理自己设置的结构的四分之一波长,根据上面的要求,我们要计算1-10GHz的该微带线特性阻抗,那么使用的最高频率所对应的波长为30mm,也就是空气盒子需要大于7.5mm,此处设置为8mm即可:

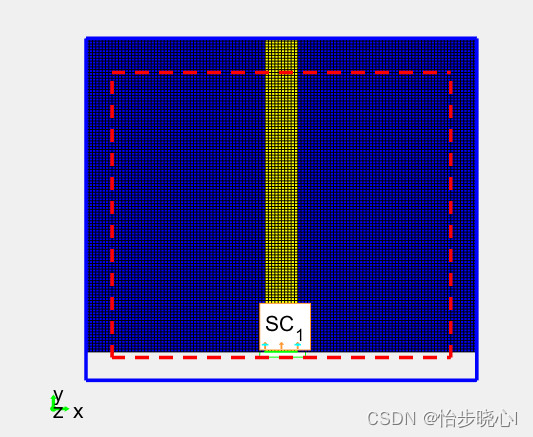

观察上面的图片,还有地方需要改一下,因为我们使用的是波端口,所以空气盒子要紧贴两个端口位置,改为:

2.5、设置波端口

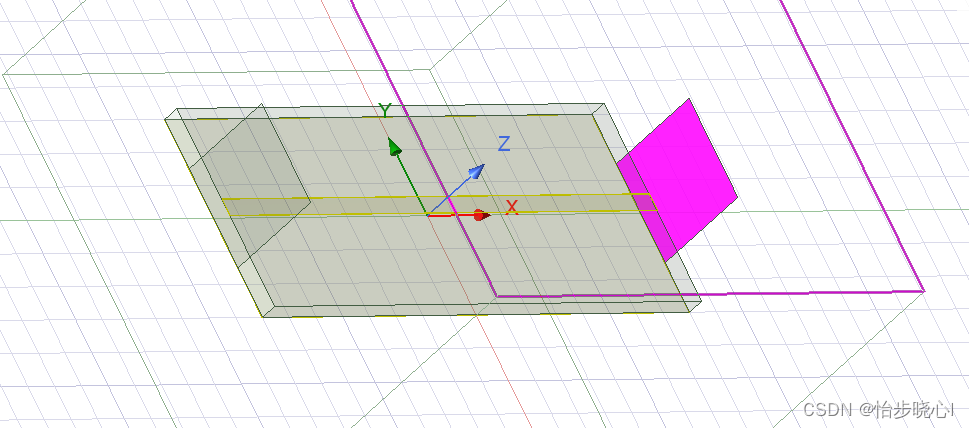

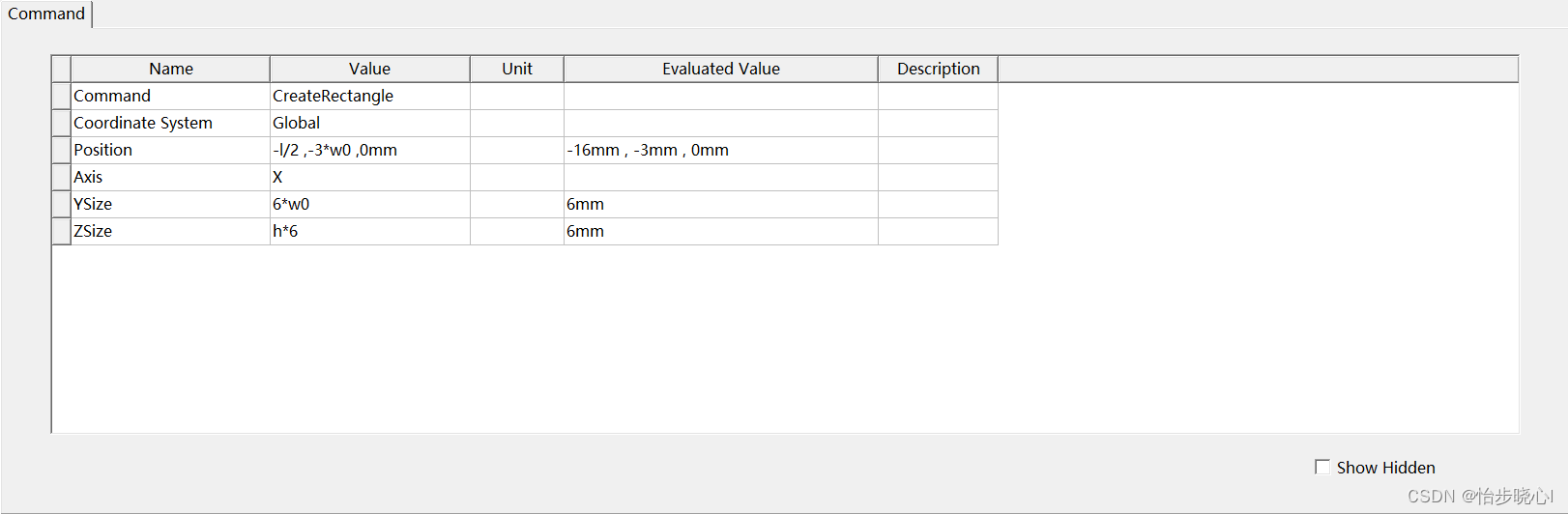

下面需要设置波端口,波端口是一个面,其与微带线基板紧贴,但是要比基板结构高一点,比信号线铜皮宽一点(波端口要尽量大,因为要包含整个辐射面):

在此给出一种推荐的设置(高度为基板的6倍,宽度为微带线的6倍):

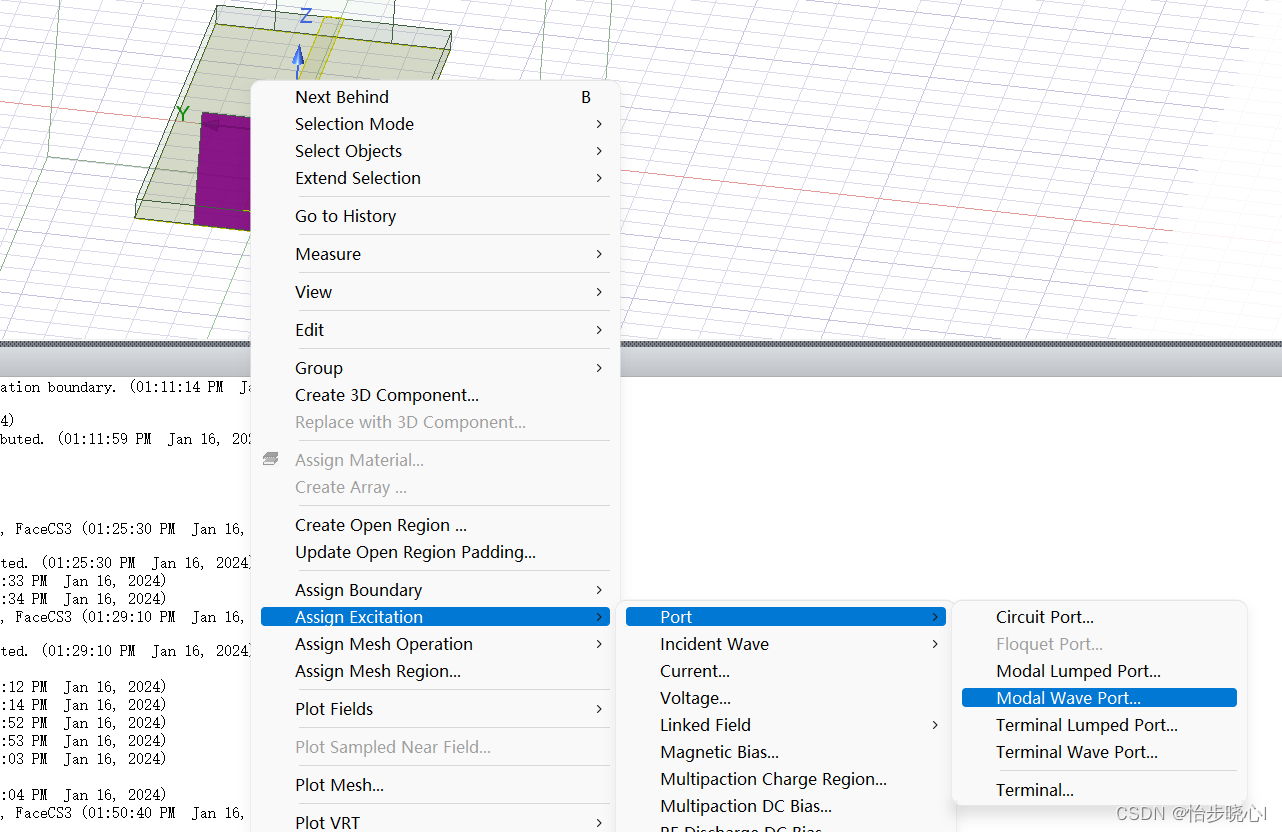

当然,还要选中刚刚创建的面,添加激励为Modal的Waveport(Modal:用于计算无源高频结构的S参数,如微带、波导和由源驱动的传输线,并用于计算入射平面波散射。S矩阵解将用波导模的入射功率和反射功率来表示。Terminal:用于计算单或多导体传输线端口的无源、高频结构的基于终端的S参数,这些S参数是由源驱动的。这种解决方案类型是基于终端的电压和电流描述):

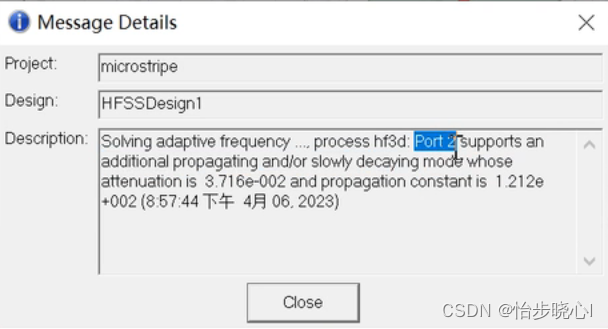

此外,如果在之后的仿真中出现这样的信息,我们需要将其适当缩小,因为面太大了引入了其他的传播模式,这在此处的实验中是不恰当的:

2.6、设置分析

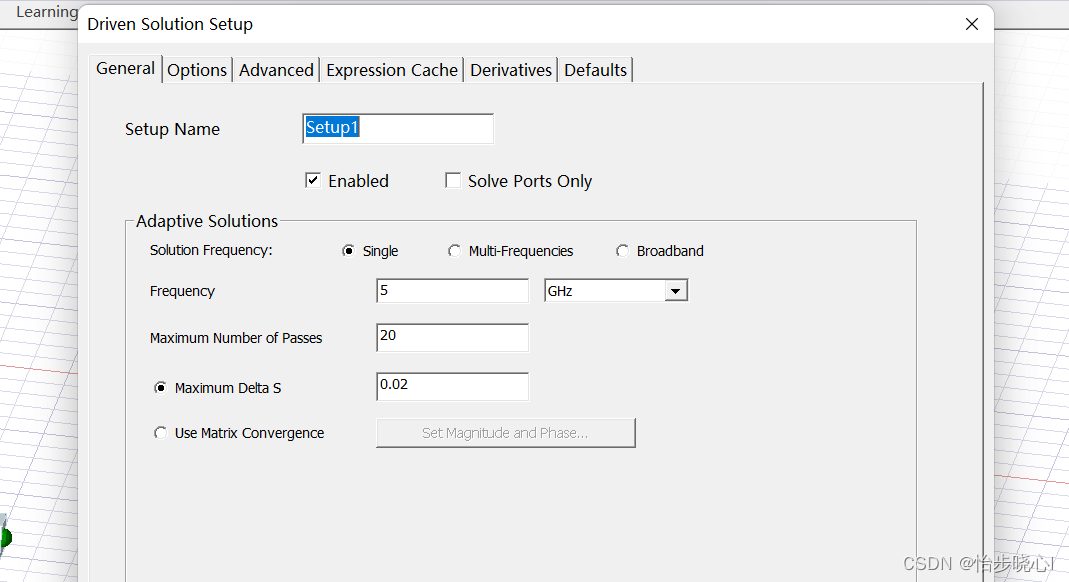

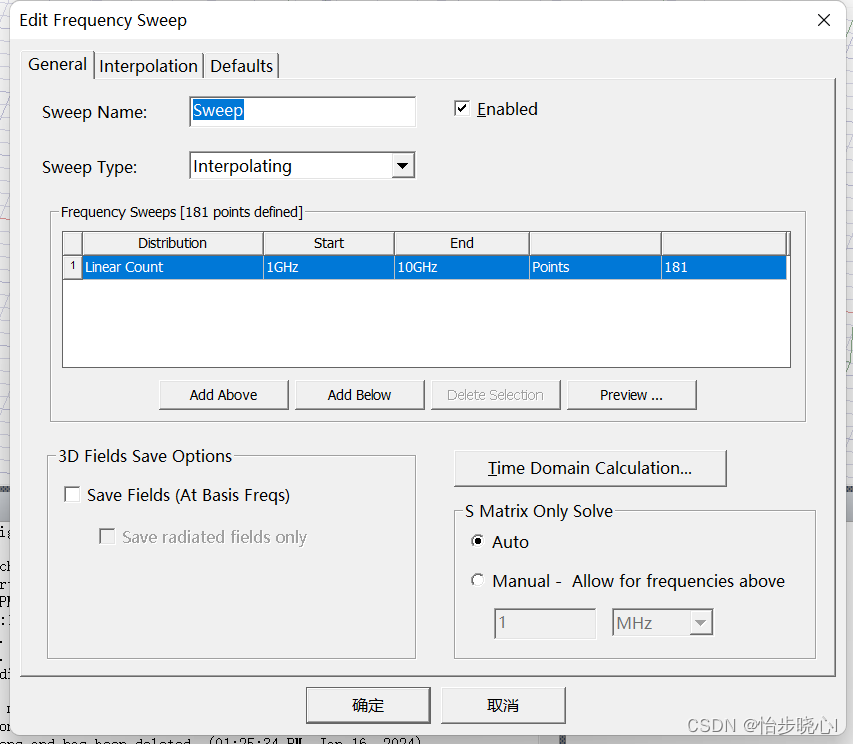

设置求解器和扫频范围:

2.7、check和运行

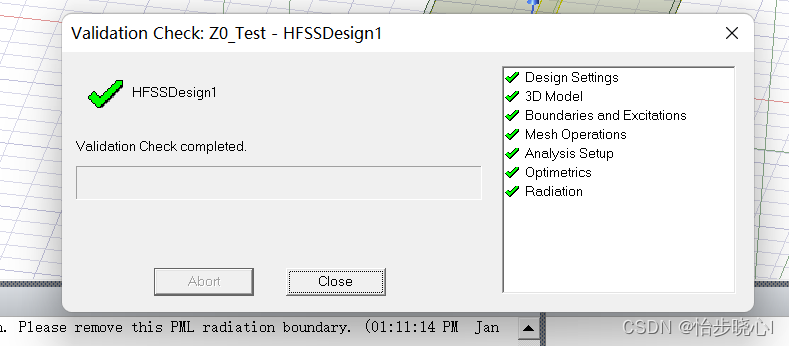

check一下,发现没有问题:

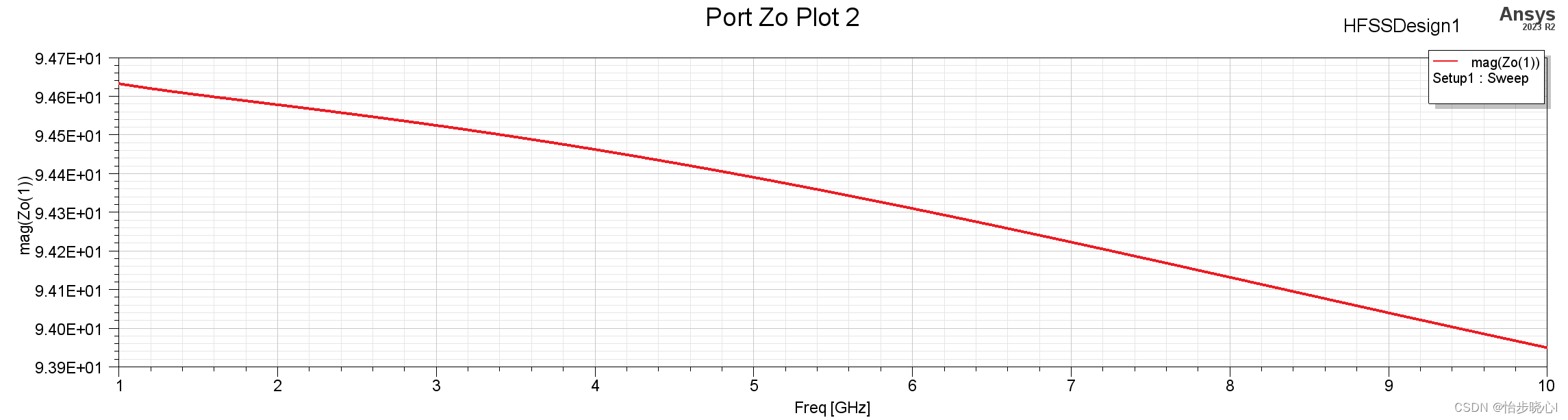

在结果中查看特性阻抗Z0,频率越高阻抗越低,好像和之前LineCalc算出来的相反有没有(算出来的大概范围是94-95欧姆的样子):

3、使用FDTD确定微带线特性阻抗

3.1 基本思路

FDTD没有HFSS的波端口可以直接用来确定特性阻抗Z0,此处使用S参数作为中间量求取特性阻抗。在终端完美匹配时,输入回波损耗S11和传输线特性阻抗具有如下关系:

Z

0

=

Z

t

e

r

m

1

+

S

11

1

?

S

11

Z0 = {Z_{term}}\frac{{1 + {S_{11}}}}{{1 - {S_{11}}}}

Z0=Zterm?1?S11?1+S11??

其中Z0是要求的微带线的阻抗,

Z

t

e

r

m

Z_{term}

Zterm?是端口1的阻抗。为达到终端完美匹配的条件,在实际仿真过程中将板材后半部分用CPML截断。

3.2 建模

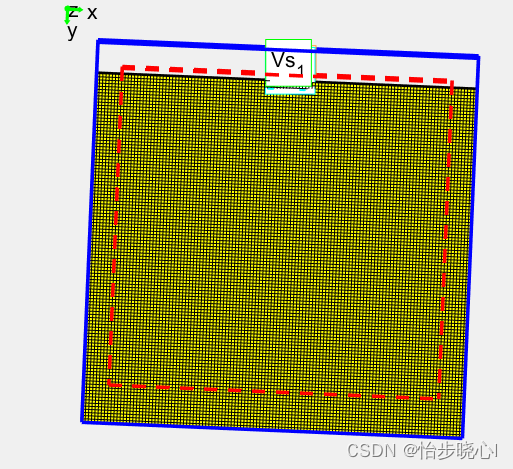

实际上,电路板的三个边都被CPML截断,来实现无限大的电路板结构:

背面全部覆铜:

3.3 网格剖分

close all; clc;

addpath(genpath('K:\Project_WXP\20240115_FDTD\FDTD_Z0'))

% initialize the matlab workspace

%参数赋值,定义分辨率单位m

wxp_dx = 1.00e-4;

wxp_dy = 1.00e-4;

wxp_dz = 0.25e-4;

%定义板材和微带大小参数,单位mm

wxp_cond_width = 1;

wxp_cond_T = 0.00;

wxp_cond_bottom_T = 0.00;

wxp_sub_width = 12;

wxp_sub_length = 11;

wxp_sub_height = 1;

wxp_sub_eps_r = 2.2;

wxp_sub_eps_i = 0.0009;

wxp_sample_position = 0.25;

fdtd_solve;

3.4 结果

在结果中查看特性阻抗Z0,频率越高阻抗越高,算出来的结果也和LineCalc中比较接近,很难说哪个比较准确:

3.5 代码运行的tips

主函数在FDTD_Z0\main里面的wxp_main.m

第一次运行修改addpath(genpath(‘K:\Project_WXP\20240115_FDTD\FDTD_Z0’))为实际电脑上的路径

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Mysql8新特性-json函数

- WIFI电路原理时序检修思路

- 助力焊接场景下自动化缺陷检测识别,基于YOLOv8【n/s/m/l/x】全系列参数模型开发构建工业焊接场景下工件表面焊接缺陷检测识别分析系统

- 九州金榜|为什么孩子越大越难管,是孩子变坏还是我们做错了?

- Git 平时工作基本操作

- 异步计算斐波那契数列

- 第一章 Java线程池技术应用

- DB2除法的小数位问题(四舍五入问题)以及其他常用的函数

- knockout调试线上环境,无法通过nginx转发的备选方案

- 使用Python做个可视化的“剪刀石头布”小游戏