DSP数字信号处理知识点(二)

发布时间:2024年01月24日

TMS320DM6437

TMS320C64x+DSP内核;32位定点处理器;工作频率为700MHz,最大处理速度为5600MIPS。

64个32位通用寄存器,8个独立的计算功能单元(2个乘法器+6个ALU),两级Cache;

一、CPU组成部分

2个数据通路、2个寄存器组、8个独立计算的功能单元;

各个功能单元的功能:

.M? ? ? ? ? ? ? 执行所有乘法操作

.S &.L? ? ? ? 完成一系列算术、逻辑、分支功能

.D? ? ? ?????????从存储器加载数据到寄存器&将寄存器中的结果保存到存储器中(地址计算)

二、CPU数据通路组成部分

1)2个通用寄存器组

2)8个功能单元

3)2个存储器加载数据通路(LD1、LD2)

4)2个存储器保存数据通路(ST1、ST2)

5)2个数据地址通路(DA1、DA2)

6)2个寄存器数据交叉通路(1X、2X)

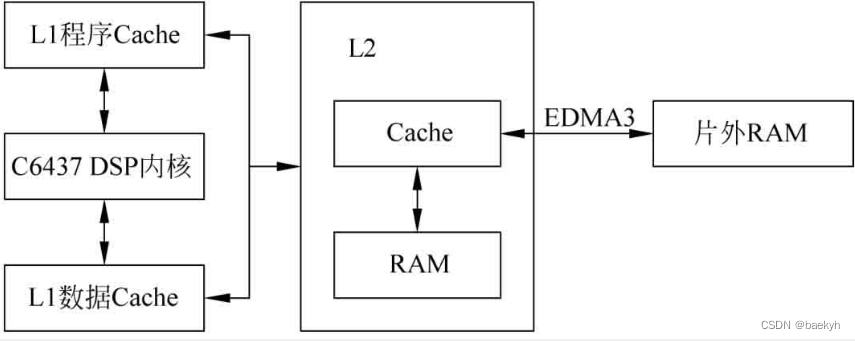

三、片内存储器结构

存储空间结构

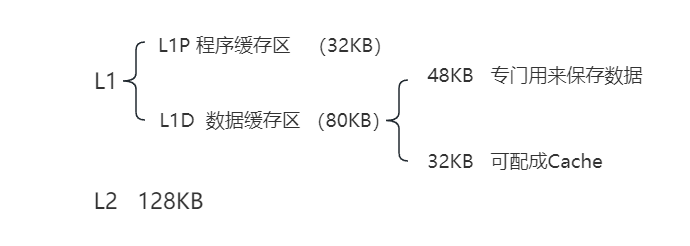

1.两级缓存结构

L1可以直接与内核交换数据,L2不能直接交换,可以全为SRAM映射到空间,全为Cache,SRAM+Cache(Cache大小只能为 0/32/64/128KB)

2.L2配置方式

四种配置方式:

1)全为SRAM(128KB)

2)全为Cache(128KB)

3)SRAM:Cache=3:1 (96KB:32KB)

4)SRAM:Cache=1:1?(64KB:64KB)

Cache配置原则:尽量多的关键数据分配在片内。

L1一般默认为Cache模式,L2一般默认为SRAM模式。

L1P功能——最大代码执行的性能;L1D功能——最大化数据处理功能。

3.存储器空间分配

存储器的映射范围

4.如何提高命中率?

混合配置L2级内存:频繁使用的代码或数据——>SRAM?

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 连续调用的函数——>Cache

文章来源:https://blog.csdn.net/qq_61271980/article/details/135749298

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!