FPGA之LUT

发布时间:2024年01月16日

????????由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构。LUT本质上就是一个RAM.它把数据事先写入RAM后,每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

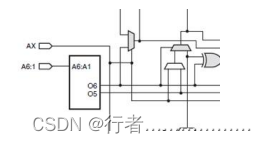

????????FPGA中的函数发生器通过六输入查找表(LUT)实现。slice的4个查找表(A, B, C和D)中的每一个都有六个独立输入(A 输入 A1 至 A6)和两个独立输出(O5 和 06)。

查找表可以实现的函数功能:

任意定义的六输入布尔函数

两个任意定义的五输入布尔函数,只要这两个函数共享公共输入·

两个任意定义的布尔函数(3个和2个或更少输入)

六输入功能使用:

?Al~A6 输入

?o5、o6 输出

两个五输入或更少的输入使用:·

Al-A5输入

·A6 驱动高.

05和06输出

多路复选器 F7AMUX, F7BMUX 和 F8MUX

·F7AMUX:用于从LUTA和B生成七个输入

F7BMUX:用于从 LUTC和D生成七个输入.

F8MUX:用于组合所有LUT以生成八个输入

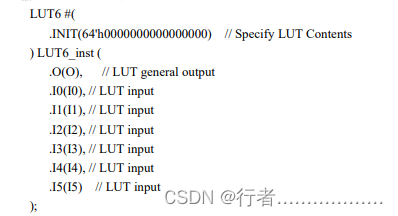

六输入查找表原语如下:

文章来源:https://blog.csdn.net/lsh11111/article/details/135613434

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- .net core 6 集成nacos的服务注册和配置中心

- 【GitHub项目推荐--Git 教程】【转载】

- 挖掘文本的奇妙力量:传统与深度方法探索匹配之道

- 计算机组成原理-CPU的功能与结构

- 如何在Android Termux中使用SFTP实现远程传输文件

- Aspx漏洞总结

- 基于SpringBoot的车辆管理系统

- 统信系统申威cpu 部署mysql、 portainer、node-exporter、Prometheus、AlertManager、grafana

- 使用kibana查看es数据

- VUE项目目录与运行流程(VScode)