程序在FLASH中的执行效率比RAM中高?

背景

通常的说法是,程序在RAM中运行的效率比FLASH中的运行效率高,但是你见过程序在FLASH中运行比在RAM中运行效率高的芯片吗?

1 系统结构简介

想要了解芯片是如何取指的,需要对MCU系统的结构有一定的了解,特别是对ICode、DCode和系统总线,下面就对STM32F103系列MCU的系统总线进行一个简单的讲解,带领大家认识MCU取指过程。

下图是STM32F103大容量系列单片机的系统结构,主要由以下部分组成:

- Corte-M3内核ICode总线(I-bus),DCode总线(D-bus),和系统总线(S-bus)

- 两个DMA

- 内部SRAM

- 内部FLASH

- FSMC

- AHB和APB上的所有设备

本节主要针对Corte-M3内核ICode总线(I-bus),DCode总线(D-bus),和系统总线(S-bus)进行讲解,它是ARM公司定义的总线架构,框图如下所示。

1.1 I-BUS、D-BUS、SYS-BUS的含义

- I-BUS(Instruction bus):指令总线,该总线将内核的指令总线与闪存指令接口相连接,指令预取在该总线上完成

- D-BUS(Data bus):数据总线,该总线将内核的数据总线与闪存存储器的数据接口相连接(常量加载和调试访问)

- SYS-BUS(System bus):系统总线,该总线连接内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间的访问

简单来说,也就是I-BUS是指令总线,负责CPU指令的正确执行,如果I-BUS出现问题,程序就不能正常运行了(程序下载到FLASH中)。

D-BUS也就是数据总线,比如访问存储在FLASH或者RAM中的数据,例如数组的值,是通过D-BUS完成的。

S-BUS是系统总线,它既可以取指,也可以访问数据,也可以访问外设。

对于STM32F103系列来说,当代码存储在FLASH中,S-BUS主要负责访问外设,I-BUS取指,D-BUS访问数据;当代码存储在RAM中的时候,此时I-BUS空闲,取指主要是通过S-BUS。

2 STM32F103在RAM和FLASH中的取指效率

2.1 Latency含义

要弄明白后面的问题,这里讲一下Latency的含义,Latency也就是Flash读取数据的等待时间,根据时钟频率不同,这个时间有所不同。

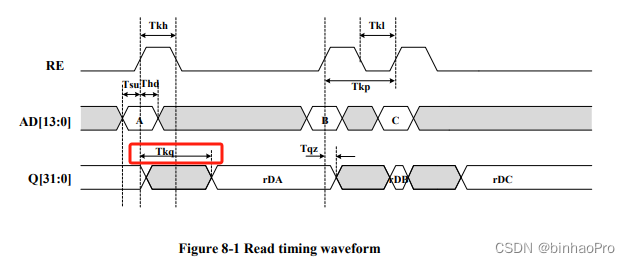

下图是Flash读时序图,可以看出,当读使能(RE)拉高之后,MCU向Flash发送需要读取的地址,Flash收到这个地址之后,有一个等待时间(Tkq),当等待的时间大于等于Tkq的时候,才能读出有效的数据,否则数据无效,这个Tkq就是我们常说的Latency。

2.2 STM32F103取值说明

从系统结果框图可知,Cortex-M3内核对Flash的操作路径比对SRAM的操作路径更短(操作SRAM多走了一条总线矩阵),按照路径的长短,内核读取Flash的数据比读取SRAM的数据更快,但是STM32F103系列单片机的FLASH在写入读取的地址之后,需要有一个等待时间,满足这个等待时间之后,才能读取有效的数据(等待时间根据主频不同有所不同),而SRAM则没有这个等待时间,所以,SRAM的取指速度比Flash快的原因就体现在Flash读取数据有一个等待时间,我们把这个等待时间叫做latency。

下图是STM32F103不同的系统时钟下,FLASH读取数据的延迟时间。

3?GD32F303在RAM和FLASH中的取指效率

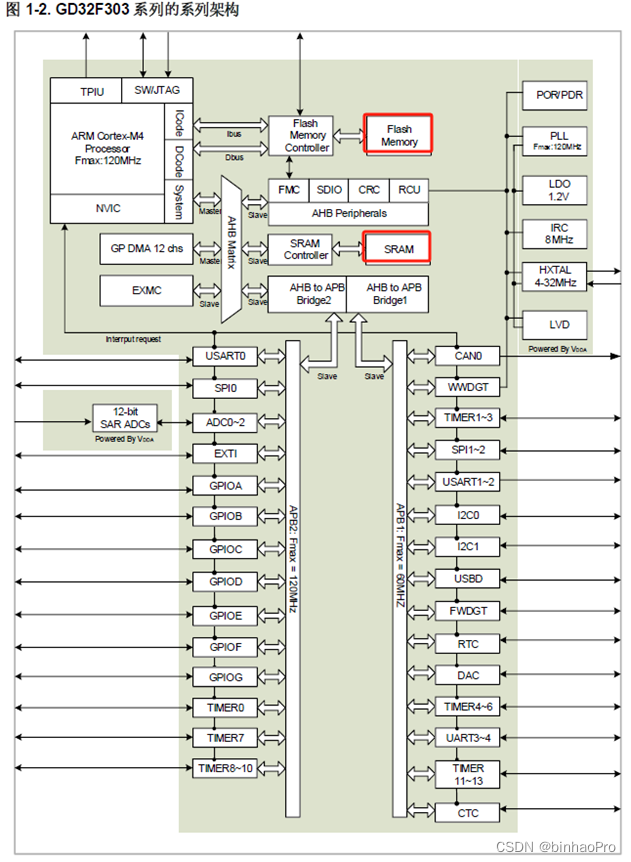

通过查看GD32F303的手册发现,GD32F303对Flash前256K字节的读取没有等待时间。

再查看GD32F303的系统框图,发现操作SRAM的路径比Flash的路径长,如果程序小于256KB,那么程序在GD32F303这款芯片的Flash中的运行效率比SRAM的运行效率高。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!