《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(8)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(7)

2.2 HOST主桥

MPC8548处理器的拓扑结构如图2-2所示:

2.2.2 存储器域地址空间到PCI总线域地址空间的转换

MPC8548处理器使用ATMU(Address Translation and Mapping Unit)寄存器组进行存储器域到PCI总线域、以及PCI总线域到存储器域的地址映射。ATMU寄存器组由两大寄存器组组成,分别为Outbound和Inbound寄存器组。其中,Outbound寄存器组将存储器域的地址转换为PCI总线域的地址,而Inbound寄存器组将PCI总线域的地址转换为存储器域地址。

在MPC8548处理器中,只有当CPU读写访问的地址范围在Outbound寄存器组管理的地址空间之内时,HOST主桥才能接收CPU的读写访问,并将CPU在存储器域上的读写访问转换为PCI总线域上的读写访问,然后才能对PCI设备进行读写操作。

如图2-2所示,CPU对存储器域的地址访问,首先使用CCB(Core Complex Bus)总线事务。如果所访问的地址在Cache中,则从Cache中直接获得数据,否则将从存储器域中获取数据。而在绝大多数情况下,外部设备使用的地址空间是不可Cache的(PCI设备使用的ROM空间可以是“可Cache”的地址空间),所以发向PCI设备的CCB总线事务通常不会与Cache进行数据交换。

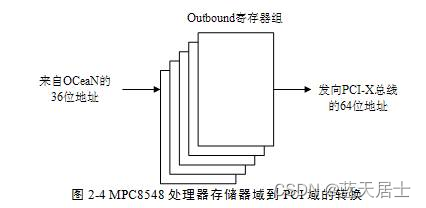

如果CCB总线事务使用的地址在HOST主桥的Outbound寄存器窗口中命中,HOST主桥将接收这个CCB总线事务,并将其转换为PCI总线事务,之后再发送到PCI总线上。MPC8548处理器的每一个HOST主桥都提供了5个Outbound寄存器窗口来实现存储器域地址到PCI总线域地址的映射,其映射过程如图2?4所示。

在介绍MPC8548处理器如何使用Outbound寄存器组进行存储器域地址空间到PCI总线域地址空间的转换之前,本节将首先介绍Outbound寄存器组中的相应寄存器。Outbound寄存器组的地址偏移、属性和复位值如表2?2所示。

表2?2 PCI/X ATMU Outbound寄存器组

| 地址偏移 | 寄存器名 | 属性 | 复位值 |

|---|---|---|---|

| 0x0_8C00/20/40/60/80 | POTARn | 可读写 | 0x00000000 |

| 0x0_8C04/24/44/64/84 | POTEARn | 可读写 | 0x00000000 |

| 0x0_8C28/48/68/88 | POWBARn | 可读写 | 0x00000000 |

| 0x0_8C30/50/70/90 | POWARn | 可读写 | 0x00000000 |

(1)POTARn和POTEARn寄存器

在PORTARn和PORTEARn寄存器中保存当前Outbound窗口在PCI总线域的64位地址空间的基地址。这两个寄存器的主要字段如下:

- POTARn寄存器的TEA字段,第0~11位,保存PCI总线地址空间的43~32位。

- POTARn寄存器的TA字段,第12~31位,保存PCI总线地址空间的31~12位。

- POTEARn寄存器的TEA字段,第12~31位,保存PCI总线地址空间的63~44位。

(2)POWBARn和POWARn寄存器

POWBARn寄存器保存当前Outbound窗口在存储器域中的36位地址空间的基地址。其主要字段如下:

- WBEA字段保存存储器域地址的第0~3位。

- WBA字段保存存储器域地址的第4~23位(WBA字段并没有保存存储器域的第24~35位地址,因为Outbound窗口大小至少为4KB的整数倍。注意在PowerPC处理器中,第0位是地址的最高位)。

POWARn寄存器描述Outbound窗口的属性,其主要字段如下:

- EN位,第0位。该位是Outbound窗口的使能位,为1表示当前Outbound寄存器组描述的存储器地址空间到PCI总线地址空间的映射关系有效;为0表示无效。

- RTT字段,第12~15位,该字段描述当前窗口的读传送类型,为0b0100表示存储器读,为0b1000表示I/O读。

- WTT字段,第16~19位,该字段描述当前窗口的写传送类型,为0b0100表示存储器写,为0b1000表示I/O写。在PCIe总线控制器中,RTT字段和WTT字段还可以支持对配置空间的读写操作。

- OWS字段,第26~31位,该字段描述当前窗口的大小,Outbound窗口的大小在4KB~64GB之间,其值为2OWS+1。

(3)使用Outbound寄存器访问PCI总线地址空间

MPC8548处理器使用Outbound寄存器组访问PCI总线地址空间的步骤如下:

(1)MPC8548处理器需要将程序使用的32位有效EA(Effective Address)转换为41位的虚拟地址VA(Virtual Address)。E500 V2内核不能关闭MMU(Memory Management Unit),因此不能直接访问物理地址。

(2)MPC8548处理器通过MMU将41位的虚拟地址转换为36位的物理地址。在E500 V2内核中,物理地址是36位(缺省是32位,需要使能)。

(3)检查LAWBAR和LAWAR寄存器,判断当前36位的物理地址是否属于PCI总线空间。在MPC8548中定义了一组LAWBAR和LAWAR寄存器对,每一对寄存器描述当前物理空间是与PCI总线、PCIe总线、DDR还是RapidIO空间对应(该组寄存器的详细说明见MPC8548 PowerQUICC III? Integrated Host Processor Family Reference Manual)。如果CPU访问的空间为PCI总线空间,则执行第(4)步,否则处理器将不会访问PCI地址空间。

(4)判断当前36位物理地址是否在POWBARn寄存器1~4描述的窗口中。如果在,则将36位的处理器物理地址通过寄存器POTARn和POTEARn转换为64位的PCI总线地址,然后HOST主桥将来自处理器的读写请求发送到PCI总线上;如果不在,则将POWBAR0寄存器作为缺省窗口,接管这个存储器访问,并使用寄存器POTAR0和POTEAR0,将处理器物理地址转换为PCI总线地址,当然在正常设计中很少出现这种情况。

许多系统软件,将Outbound窗口两边的寄存器使用“直接相等”的方法进行映射,将存储器域的地址与PCI总线地址设为相同的值。但是系统软件程序员务必注意这个存储器地址与PCI总线地址是分属于存储器域和PCI总线域的,这两个值虽然相等,但是所代表的地址并不相同,一个属于存储器域、而另一个属于PCI总线域。

更多内容请看下回。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Talk | ACM MM 2023最佳论文,CATR:基于组合依赖和音频查询的视频分割模型

- 用了这8个 Python 数据挖掘工具包,生产力明显得到了提升!

- 【无标题】

- springboot实现netty的websocket服务端与客户端

- openlayers [八] 地图覆盖物overlay详解

- thinkphp5向数据表插入数据并且获得id

- 晶闸管(Thyristor)

- Zabbix“专家坐诊”第218期问答汇总

- 网络/信息安全(黑客)技术——自学2024

- 【msvcr120.dll】修复电脑出现msvcr120.dll找不到的详细方法