ADS学习笔记(一)

在ADS中,信号上升时间为信号从0~100%所用的时间,而实际上定义的上升边均为10%~90%,所以可以认为上升边=0.8*ADS设置上升时间。

一、终端开路及短路的反射信号

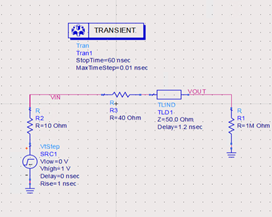

1.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V:

传输线:特性阻抗为50Ohm,

时域扫描:结束时间60ns,步长0.01ns:

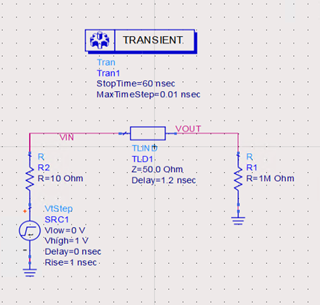

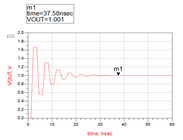

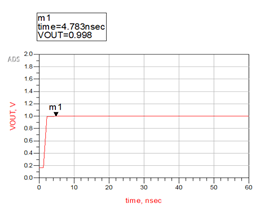

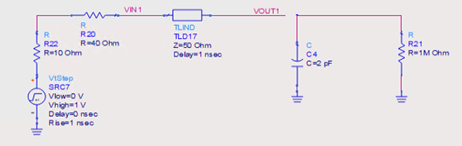

图1.1传输线仿真模型

传输线仿真模型如图1.1所示,分别在负载为1KOhm(开路),0.01Ohm(短路),50Ohm(阻抗匹配)情况下仿真传输线远端的电压。

2.仿真结果

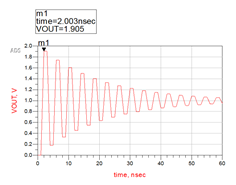

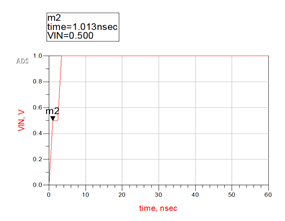

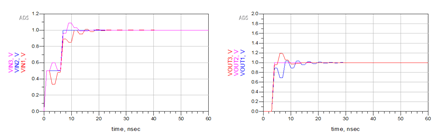

图1.2负载为1KOhm(开路)

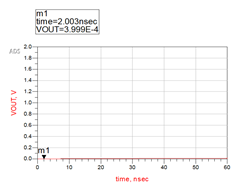

图1.3负载为0.01Ohm(短路)

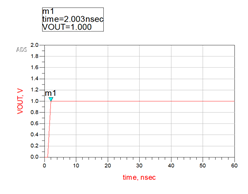

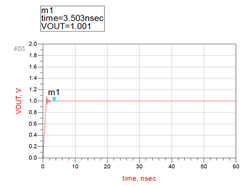

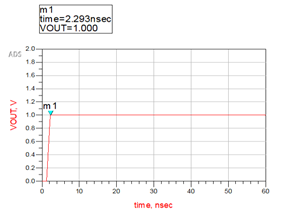

图1.4负载为50Ohm(阻抗匹配)

从以上三图中可以看出,当负载开路时输出电压振铃噪声峰值接近2V(1KOhm非完全开路),最终趋于1V:负载为0.01Ohm(接近短路)时,输出电压为0V;负载为50Ohm(阻抗匹配)时,输出电压接近1V,且没有反射电压,故没有振铃噪声。实验现象符合传输系数和反射系数p的定义。

二、多长需要端接

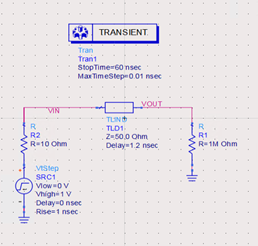

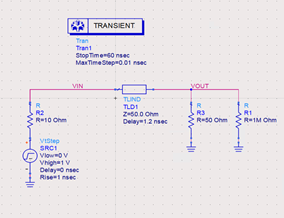

1.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V:

驱动器内阻:10Ohm;

时域扫描:结束时间60ns,步长0.01ns;

终端负载输入电阻可看作开路:

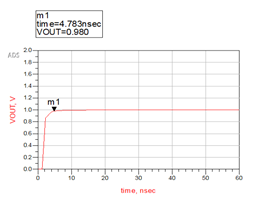

图2.1仿真模型

2.仿真结果

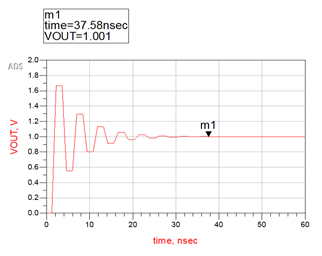

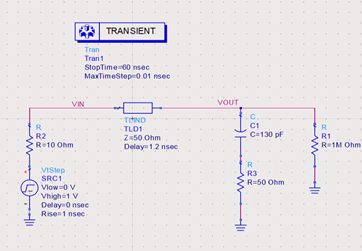

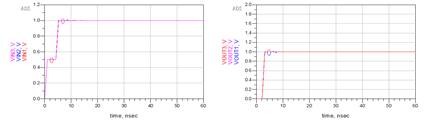

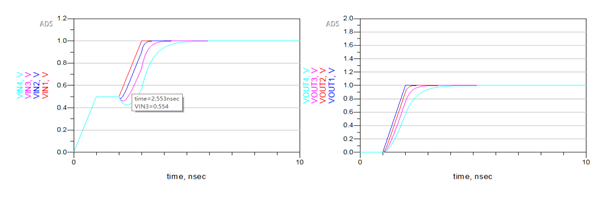

图2.2传输线时延1.2ns的信号波形

图2.3传输线时延0.2ns的信号波形

图2.4传输线时延0.1ns的信号波形

当驱动器具有内阻时,使用如图2.1的模型进行仿真,将传输线的时延设定为1.2ns、0.2ns和0.1ns分别仿真,终端输出电压如图2.2~图2.4所示,可以看出时延为1.2ns时振铃噪声相当严重,当传输线时延为0.2ns和0.1ns时可以看出振铃噪声较小。

本次仿真中上升时间为1ns,那么信号的10%~90%上升边为0.8ns,可以看出当传输线延时为0.2ns时,振铃噪声峰值已经超过了0.1V(稳态的10%),如果延时再增大就会出现信号完整性问题。那么这就验证了一条经验法则:当传输线时延超过上升边的20%时,振铃噪声有可能会引起问题。

因为在FR4中信号传播速度约为6in/s,所以无终端端接传输线的最大长度Lenmax=6in/s*0.2ns=1.2in,则有经验公式2-1:

Lenmax<RT? (2-1)

其中,Lenmax为无终端端接传输线的最大长度,RT为上升边。

综上,为了保证信号的传输质量,当传输线时延超过上升边的20%时,需要进行端接。

三、点到点拓扑的通用端策略

1.仿真验证

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V:

驱动器内阻:10Ohm;

时域扫描:结束时间60ns,步长0.01ns;

终端负载输入电阻可看作开路:

图3.1无端接系统模型

图3.2传输线时延1.2ns的信号波形

当传输线时延为1.2ns时,无端接系统的远端信号波形如图3.2所示,可见振铃噪声较大,需要进行端接优化。振铃是由源端和远端的阻抗突变,两端之间不断往复的多次反射引起的,所以如果能至少在一段消除反射,就可以减小振铃。

2.源端串联端接

2.1原理简述

源端串联端接系统模型如图3.3所示,源端串联端接为在驱动器与传输线中间串接电阻进行阻抗匹配,其中端接电阻与驱动器内阻之和应该与传输线特性阻抗相等。

2.2仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V;

驱动器内阻:10Ohm;

时域扫描:结束时间60ns,步长0.01ns:

终端负载输入电阻可看作开路;

源端端接电阻为40Ohm;

图3.3源端串联端接系统模型

2.3仿真结果

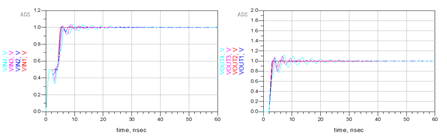

传输线前端和后端的信号如图3.4和图3.5所示,图3.4中值得注意的是源端电压呈台阶形状,这是源端串联端接的一个特点,且传输线往返时间越长,台阶形状就越长。在图3.5中可以看出源端串联端接基本消除了传输信号中的振铃噪声,源端串联端接不改变驱动器的驱动能力,信号不损耗,是最常用的端接方式。

图3.4传输线前端信号

图3.5传输线后端信号

3远端并联端接

3.1原理简述

远端并联端接系统模型如图3.6所示,远端并联端接为在传输线后端并接电阻进行阻抗匹配以消除振铃。

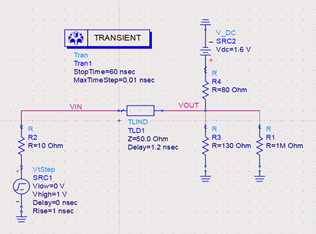

3.2仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V;

驱动器内阻:10Ohm;

时域扫描:结束时间60ns,步长0.01ns;

终端负载输入电阻可看作开路;并联端接电阻R8为50Ohm

图3.6远端并联端接系统模型

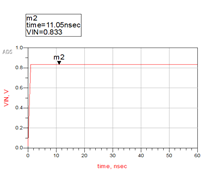

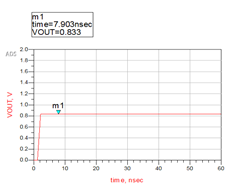

3.3仿真结果

传输线前端和后端的信号如图3.7和图3.8所示,在图3.8中可以看出远端并联端接基本消除了传输信号中的振铃噪声,由于分压和损耗,远端信号电压约为0.833V,相对于电源电压下降较多,使系统的驱动能力有所下降,驱动性能不如串联端接。远端并联端接的特点为会使驱动器的驱动能力下降,并联端接电阻消耗能量,因此不常用

图3.7传输线前端信号

图3.8传输线后端信号

4.远端戴维南端接

4.1原理简述

远端戴维南端接系统模型如图3.9所示,远端戴维南端接为在远端传输线后端并联直流源和电阻来拉高驱动能力,在保证系统驱动能力的同时消除振铃。

4.2仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V

驱动器内阻:10Ohm

时域扫描:结束时间60ns,步长0.01ns

终端负载输入电阻可看作开路

远端并联1.6V直流电压源

经调试得出上拉电阻R9为80Ohm:下拉电阻R10为1300hm。

图3.9远端并联端接系统模型

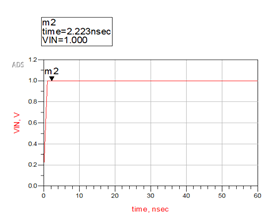

4.3仿真结果

传输线前端和后端的信号如图3.10和图3.11所示,在图3.11中可以看出远端戴维南端接基本消除了传输信号中的振铃噪声,由于有1.6V直流源存在,远端信号电压为1V,驱动能力强于远端并联端接且具有并联端接消除振铃优点。

图3.10传输线前端信号

图3.11传输线后端信号

5.远端RC端接

5.1原理简述

远端RC端接系统模型如图3.6所示,远端RC端接即为在传输线后端并接电阻和电容以消除振铃。其中端接电阻一般与传输线特性阻抗相等,电容值非常小(200pF-600pF)

5.2仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V

驱动器内阻:10Ohm

时域扫描:结束时间60ns,步长0.01ns

终端负载输入电阻可看作开路

经调试计算求得并联电阻R9为50Ohm,电容C1为130pF。

图3.12远端RC端接系统模型

5.3仿真结果

传输线前端和后端的信号如图3.13和图3.14所示,在图3.14中可以看出远端RC端接基本消除了传输信号中的振铃噪声,远端信号电压约为1V。远端RC端接的特点为可以减小高频反射,低频和直流损耗小,但是会减慢高速信号的速度(图3.14中上升边变长)。

图3.13传输线前端信号

图3.14传输线后端信号

四、短串联传输线的反射

1.原理简述

由反射系数p的定义可知,在一段均匀传输线中间某部分传输线的阻抗发生突变时,必然会产生反射信号并影响传输信号。

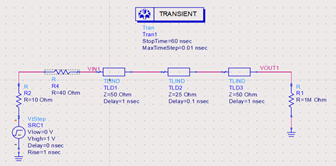

短串联传输线的系统模型如图4.1所示,可以看见图中有三段传输线TLD1、TLD2、TLD3,其中TLD1、TLD3均为特性阻抗为50Ohm,时延为1ns的传输线,接下来将改变TLD2的特性阻抗和时延来模拟传输线的电气突变,从而研究传输线特性阻抗突变对传输信号的影响。

2.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V

驱动器内阻:10Ohm

源端串联电阻:40Ohm

时域扫描:结束时间60ns,步长0.01ns

TLD1、TLD3均为特性阻抗为50Ohm,时延为1ns的传输线

终端负载输入电阻可看作开路

图4.1远端RC端接系统模型

3.仿真结果

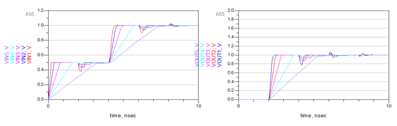

当TLD2的时延为1ns,特性阻抗分别为25Ohm、50Ohm、75Ohm时,因为时延为1ns,可以认为传输线上的这段电气上的突变是较长且均匀的,传输线上的反射信号和传输信号如图4.2所示:

图4.2传输线上的传输信号和反射信号(时延1ns)

当TLD2的时延为0.1ns,特性阻抗分别为25Ohm、50Ohm、75Ohm时,因为时延为0.1ns,为上升边的12.5%,可以认为传输线上的这段电气上的突变是较短的,传输线上的反射信号和传输信号如图4.3所示:

图4.3传输线上的传输信号(左)和反射信号(右)(时延0.1ns)

从图4.2中可得,当时延较长时,传输信号波动值较大:

从图4.3中可得,当时延较小时,传输信号波动较小(低于电压摆幅5%),可忽视不计:从而验证了经验法则:即可容许的阻抗突变最大长度:

Lenmax < RT (4-1)

Lenmxa为阻抗突变最大长度(in),RT信号为上升边(ns);

即突变段的时延小于信号上升边的20%,则突变对信号质量的影响可忽略。

五、短并联传输线的反射

1.原理简述

我们常常在一段均匀传输线上接一个分支,若分支很短,就称为桩线。桩线通常为BGA封装过程的产物。传输线上每一个桩线将会产生反射信号,其中一部分反射信号在桩线上来回振荡,也有一部分信号返回源端和远端。因为反射较多,这样分析桩线影响会变得很复杂。

分析桩线影响的仿真模型如图5.1所示,用一段特性阻抗为50Ohm的传输线TLD4来模拟桩线,分析在不同时延下桩线对传输信号的影响。

图5.1短并联传输线模型

2.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V:

驱动器内阻:10Ohm;

源端端接电阻:40Ohm;

时域扫描:结束时间60ns,步长0.01ns:

TLD1、TLD3均为特性阻抗为50Ohm,时延为1ns的传输线;

TLD2为特性阻抗为50Ohm的传输线(桩线):

终端负载输入电阻可看作开路:

3.仿真结果

图5.3传输线上的传输信号(左)和反射信号(右)

当TLD2的时延分别为1%,20%,40%,60%RT时,传输线上的反射信号和传输信号如图5.3所示。从图5.3的传输信号可以看出,当时延在20%RT以下时,反射噪声电压摆幅较小,其影响可以忽略,而时延在20%RT以上时,不可忽略桩线对信号质量的影响。

六、容性终端的反射

1.原理简述

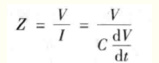

所有实际接收器都有门输入电容,一般约为2pF。当信号沿传输线到达末端的理想电容器时,决定反射系数的瞬时阻抗将随时间变化而变化。因为时域中电容器的阻抗为:

(6-1)

(6-1)

所以反射系数会随时间变化,此时传输线上的信号波形是由传输线的特性阻抗,电容器的电容量和信号上升边决定的。容性终端的反射模型如图6.1所示,观察电容C1不同取值时传输线信号的变化来研究容性终端反射的特点。

图6.1容性终端的反射模型

2.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V:

驱动器内阻:10Ohm:

源端端接电阻:40Ohm:

时域扫描:结束时间60ns,步长0.01ns:

TLD1为特性阻抗为50Ohm,时延为1ns的传输线:

终端负载输入电阻可看作开路:

3.仿真结果

图6.2传输线上的反射信号(左)和传输信号(右)

当电容分别为0pF、2pF、5pF、10pF时,传输线上的反射信号和传输信号如图6.2所示,随着电容值的增加,传输信号的上升边不断增加:参照RC电路的充电特性,若信号初始上升边小于RC充电时间,可以得出传输信号的10%~90%上升边主要由RC充电电路决定,可以近似的认为上升边090=2.2Z0C。如果信号初始上升边大于10%~90%RC上升边时,那么末端的电容器将使信号上升边累加上约等于10%~90%RC上升边的时延。

七、走线中途容性负载的反射

1.原理简述

测试焊盘、过孔、封装引线或连接到互联中途的短桩线都起着集总电容的作用。如果在传输线中有容性负载,对于远端而言,容性负载所产生的带负值符号的部分信号将反射回远端。这些反射回接收器端的信号为负电压,使接收端信号下降形成下冲而对传输信号造成一些影响。

传输线中突变处电容器的阻抗为:

Z=V/(C*dV/dt)=RT/C(7-1)

可以看出当电容量越大,电容阻抗就越小,其造成的下冲就越大:同理若信号上升边越小,电容阻抗就越小,下冲就越大。仿真模型如图7.1所示。

图7.1中途容性负载的反射模型

2.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V:

驱动器内阻:10Ohm:

源端端接电阻:40Ohm:

时域扫描:结束时间60ns,步长0.01ns:

TLD1、TLD2特性阻抗均为50Ohm,时延为1ns的传输线:

终端负载输入电阻可看作开路。

3.仿真结果

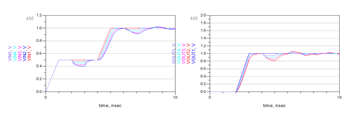

图7.2传输线上的传输信号(左)和反射信号(右)(电容值2pF)

图7.2上升时间分别为0.2ns、0.4ns、0.8ns、1.6ns、3.2ns,从中可以明显看出,当电容值一定时,信号上升边越小,传输信号下冲越明显,这与式7-1的结论相符。

图7.3传输线上的传输信号(左)和反射信号(右)(上升边1ns)

图7.3电容值为0.01pF、2pF、4pF、6pF、8pF,从中可以明显看出,电容值越大,传输信号下冲越明显,上升边时延越大,这与式7-1的结论相一致:当电容值大于2pF时,传输信号下冲的电压摆幅超过容许范围。从而可以得出经验法则:

(7-2)

其中Cm为反射噪声不产生问题时可容许的最大电容量(nF),RT为信号上升边(ns),当Zo为50Ohm时,其中RT单位为ns,Cm单位为pF

Cx<4RT? (7-3)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【NI国产替代】PXI-4498,204.8 kS/s , 114 dB , 4个增益选项, 0.5 Hz AC耦合,16输入PXI声音与振动模块

- ES分词查询

- #HarmonyOS:UIAbility组件生命周期--UIAbility组件启动模式

- css实现梯形tab切换

- 【39 Pandas+Pyecharts | 第七次人口普查数据分析可视化】

- 零售行业中的物联网:用例、优势和趋势

- 【Python】内置的type()函数详解和示例

- 理解Java中的AQS

- 【期末复习向】长江后浪推前浪之ChatGPT概述

- CMMI-项目总体计划模版